https://mp.weixin.qq.com/s/afRVgTCYs1Mxu898uSmVaQ

整理一篇介绍Diplomacy和TileLink的文章。

0. ABSTRACT

Modern systems-on-chip (SoCs) incorporate a large and growing number of specialized hardware units that must be integrated into a unified address space via a shared bus topology.

This process is labor-intensive and error-prone because the interface requirements of all connected blocks must be mutually satisfied.

The design productivity gains derived from the modularity of RISC-V are bottlenecked by the need to integrate the cross product of processor variants, bus ordering behaviors, and slave device capabilities.

This growing complexity has stimulated development of new tools and methodologies to enable the completion of complex and parameterized SoC designs.

We present two tools used to create correct-by-construction interconnects in the Rocket Chip generator:

Diplomacy is a parameter negotiation framework for generating parameterized protocol implementations. Beyond confirming the mutual compatibility of the system endpoints, Diplomacy enables them to specialize themselves based on knowledge of the other endpoints included in a particular system.

TileLink is a highly-parameterized chip-scale shared-memory interconnect standard. The implementation of TileLink in the Rocket chip generator exploits Diplomacy to specialize the interconnect to different levels of protocol conformance.

1. INTRODUCTION

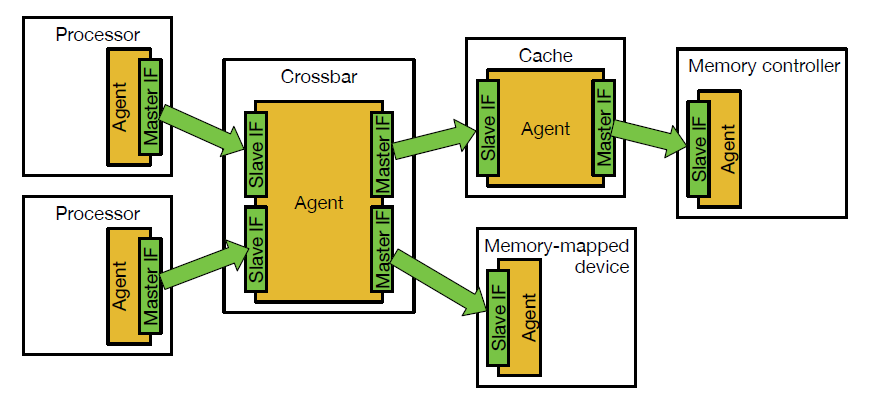

Modern systems-on-chip (SoCs) incorporate an ever-growing number of hardware units specialized to perform particular computational tasks. In order to communicate with one another and memory, these diverse compute resources must be integrated into a shared interconnection network. Such a network typically consists of a hierarchical topology of buses that provide the compute engines with a shared global address space.

The process of creating such interconnects is labor-intensive and error-prone because the interface requirements of all connected blocks must be mutually satisfied.

The design productivity gains derived from the modularity of RISCV are bottlenecked by the need to integrate the cross product of processor variants, bus ordering behaviors, and slave device capabilities. This growing complexity has stimulated development of new tools and methodologies to enable the completion of complex and parameterized chip designs [8].

We present two tools used to create provably-correct interconnects in the Rocket Chip SoC generator [1].

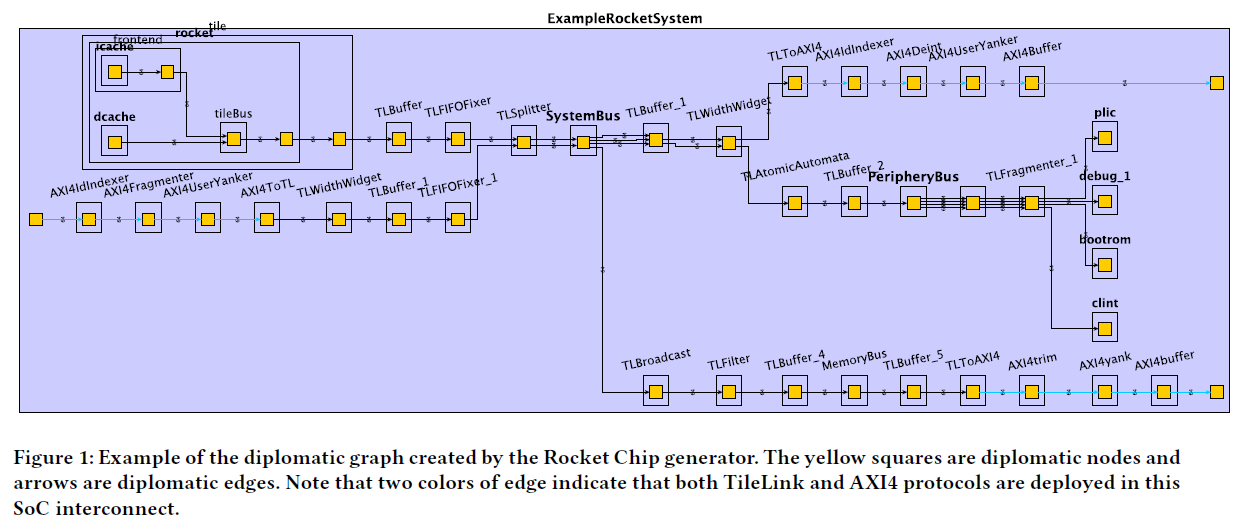

Our approach is centered around first constructing a graphical model of the properties

of the proposed interconnect design, and then using this model to reason as to whether the solution provides all required functionality and will exhibit correct behavior.

"Correct" in this case means (a)the generated design will be free from protocol-level deadlock, (b)is guaranteed to make forward progress, and that (c)the cross-product of masters' and slaves' operational requirements is satisfied.

Diplomacy is a framework for negotiating the parameterization of protocol implementations.

Given (a)a description of sets of interconnected master and slave devices, and (b)a bus protocol template,

Diplomacy cross-checks the requirements of all connected devices, negotiates free parameters, and supplies final parameter bindings to adapters and endpoints for use in their own hardware generation processes.

Beyond confirming the mutual compatibility of the system endpoints, Diplomacy enables them to specialize themselves based on knowledge about the capabilities of other endpoints included in a particular system.

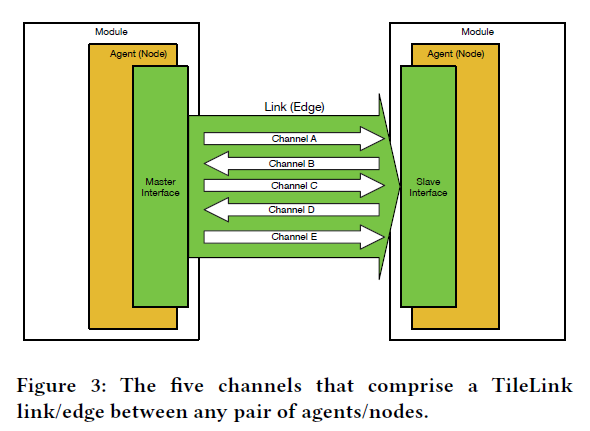

TileLink is a highly-parameterized chip-scale shared-memory interconnect protocol standard [5].

The protocol is hierarchically composable and guaranteed to deadlock-free at the transaction level[9]. The implementation of TileLink in the Rocket Chip generator exploits Diplomacy to supply a heterogeneous level of protocol conformance across the interconnect, specialized for the capabilities of devices connected to certain buses.

This paper discusses how various features of diplomatic TileLink have guided the design patterns we have adopted in the Rocket Chip generator.

(a)We avoid manually specifying any protocol parameters that can be inferred from a declarative description of the system interconnection network graph.

(b)We parameterize our generators to emit hardware based on their view of the rest of the system.

(c)We deploy a set of graph transformation patterns that make it easy to re-time links by inserting queues, that comprise thin single-purpose adapters, and that safely create hierarchies of interoperable components.

2. DIPLOMACY

3. TILELINK

4. DESIGN PATTERNS

4.1 DRYing Out Parameterization

4.2 Hardware Generation with A View

4.3 Correct By Composition

5. CONCLUSION

In this paper we have discussed how various features of diplomatic TileLink have guided the design patterns adopted in the Rocket Chip generator.

We avoid re-specifying any parameters that can be inferred from a declarative description of the system interconnect graph.

We parameterize our generators to emit hardware based on a diplomatically negotiated view of the system.

We deploy a set of safe graph transformation patterns that make it easy to re-time

links with queues, that compose more complicated adapters from single-purpose ones, and that inject hierarchies of composable components at standardized attachment points.

We see many forthcoming opportunities to deploy correct-by-construction

software development methods to other aspects of SoC hardware component integration.

Clock domains are one area where each mixed-in component could specify how it relates to the overall interconnect graph, and the correct clock and reset would be supplied to the second phase elaboration automatically.

Interrupts are another type of signal where we would like to avoid any explicit notion of cardinality and instead infer it from graphical structure.

Finally, we are working to develop endpoint generators that are protocol-independent, presenting generator authors with standard APIs that allow their device to be deployed regardless of the underlying interconnect protocol.

The Rocket Chip code base containing Diplomacy itself, all of our diplomatic bus protocol implementations, and a variety of TileLink-compatible cache, interconnect, and device generators, is open source and available as part of the Free Chips Project at

6. REFERENCES

略