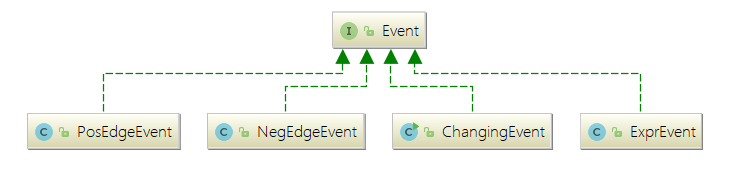

hardware modeling基于事件驱动模型,RTL中定义了多种事件。

jchdl 参考了Verilog中的事件类型。

一. PosEdgeEvent

上升沿事件。对应Verilog中的posedge关键字。

使用方式为:PosEdgeEvent.of(regA),意为:观察regA的值是否从0变为1,即发生上升沿事件。

二. NegEdgeEvent

下降沿事件。对应Verilog中的negedge关键字。

使用方式为:NegEdgeEvent.of(regA),意为:观察regA的值是否从1变为0,即发生下降沿事件。

三. ChangingEvent

值变化事件。对应Verilog敏感表中不带posedge/negedge的敏感项。

使用方式为:ChangingEvent.of(regA),意为:观察regA的值是否发生变化,如果发生变化,则触发事件。

四. ExprEvent

表达式的值发生变化的事件。(Verilog转化可能不正确,需要学习Verilog之后调整。)

比如:assign wireA = mem[addr];

其中mem是一个数组,addr是数组的索引值。而wireA的值,同时取决于这两个变量,即取决于表达式的值的变化。

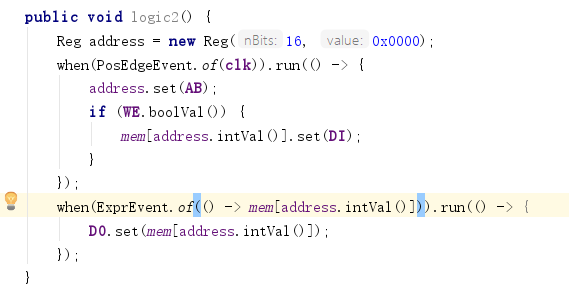

使用方法:ExprEvent.of(expr),其中expr参数为Expression对象,可以使用lambda表达式构建:

ExprEvent.of(() -> mem[addr])