观察Verilog代码可以发现,对逻辑的描述中都是assign和always代码块。这正对应了硬件电路中的一个个并行电路模块。

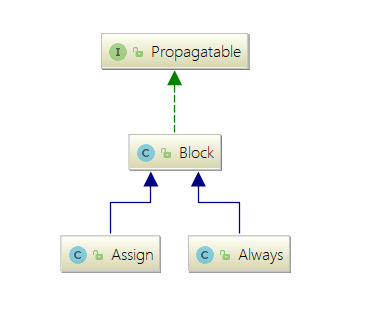

参考Verilog,jchdl支持Assign和Always两种block。

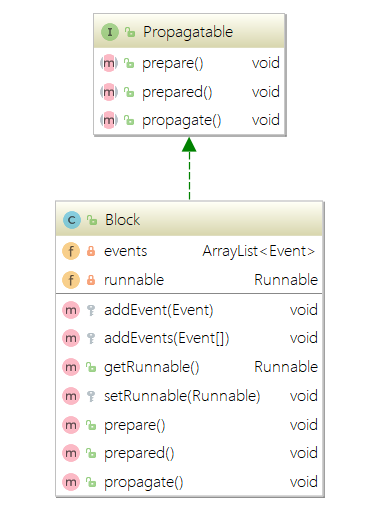

一. Block

Block依赖于一组事件,如果其中一个事件触发,则需要执行对应的逻辑(runnable),这个逻辑一般是为某个线或寄存器赋值。

Block不能直接使用,需要使用Assign和Always。

二. Assign

为线(Bit、Bits)赋值的Block.

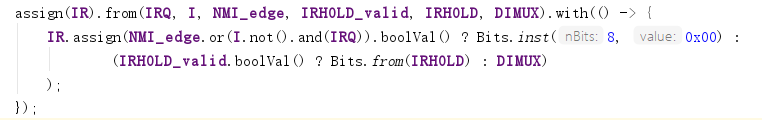

结合Module提供的辅助方法使用,Runnable使用lambda表达式:

意为:把IRQ, I, NMI_edge, IRHOLD_valid, IRHOLD, DIMUX的值,使用(with)runnable转换之后,赋值给IR。

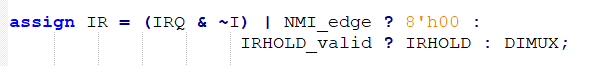

对应的Verilog代码为:

主要方法:

- from(Bitable...): 依赖的Bitables,即这些bitable值的变化,会触发Assign Block的执行;

- from(Expression):依赖的Expression,即这个Expression值的变化,会触发Assign Block的执行;

- with(Runnable):使用Runnable描述赋值逻辑;

三. Always

描述敏感表中事件驱动的逻辑的模型。

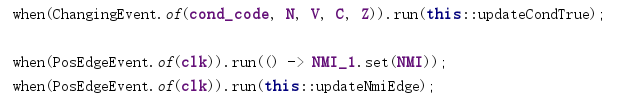

结合Module提供的辅助方法使用,Runnable使用lambda表达式:

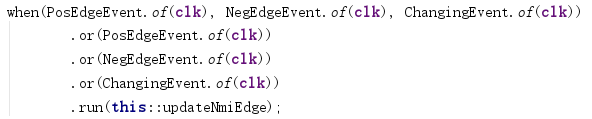

多个事件,可以都作为when的参数提供,也可以调用Always Block的or()方法:

这个比较灵活,建议都放到when函数里面,or暂时不支持转换为Verilog。