https://mp.weixin.qq.com/s/mH84421WDGRb7cuU5FEFIQ

Verilog的赋值很是复杂,包括:

1. Continuous assignment;

2. Procedural assignment:

a. Blocking Assignment;

b. Non-bocking Assignment(NBA);

但其实没有必要,理解起来也可以很简单;

比如Continuous assignment是针对wire而言,wire需要的是driven,而不是assign,驱动(driven)是物里

的概念,而赋值是编程的概念;

这个连续指的不是值的变化,而是assign这个动作。比如assign wireA = wireB,不是这一次把wireB的值赋值给wireA,而是以后wireA的值都跟随wireB的值的变化而变化。所以可以理解为driven和连接。也因此continous assignment只能针对wire使用。

Procedural Assignment针对寄存器使用,值的就是赋值,因为reg可以存值。因此称为过程性(Procedural),赋值之后就结束了。

那为什么还需要blocking和Non-blocking呢?

可能是要处理多个寄存器之间的赋值问题。

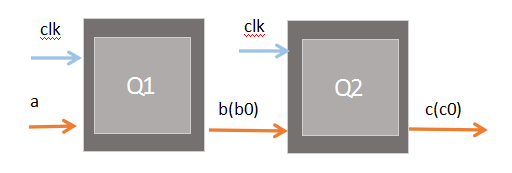

CASE 1(https://blog.csdn.net/chief_cf/article/details/52373831):

always@(posedge clk)

begin

b <= a;

c <= b;

end

这个的写法可以改成:

always@(posedge clk)

begin

c = b;

b = a;

end

具体综合成什么电路,就交给综合器。

CASE 2(值交换):

always@(posedge clk)

begin

b <= a;

a <= b;

end

我不清楚具体综合出的电路是什么样的,但是写法可以改成:

always@(posedge clk)

begin

tmp = b;

b = a;

a = tmp;

end

也不需要非阻塞赋值;

CASE 3:

always @(posedge clk)

begin

a <= u&v&w;

b <= x|y|z;

end

这种写法提倡拆分成两个always语句块,每个处理一个独立的逻辑:

always @(posedge clk)

begin

a = u&v&w;

end

always @(posedge clk)

begin

b = x|y|z;

end

什么意思呢?就是要化简建模的方法论(Methodology):

只需要处理wire和reg的assignment即可。

不需要为多个wire之间怎么assign,多个reg之间怎么assign再提供新的机制了。这样的Methodology最简单。

事实上,可以看到新出的建模方法,无论是SystemC还是Chisel,都没有Non-blocking Assignment的概念。

Verilog可以在Gate and Switch层进行建模,也可以在RTL层进行建模。

这个NBA应该属于RTL层的概念,因为他使用的是reg这个数据类型,而不是DFF这个结构。

RTL层是一个抽象层次,所以我觉得使用RTL进行建模时,应当尽量使用这个抽象层次的语法结构。

至于如何综合成最终的电路,则交给综合器去做。我认为综合器是可以把CASE 2中的reg tmp给优化掉的。

打一个比方:如果坐在汽车里面,就只需要踩油门就行了。没必要再从底盘上开两个洞,把脚伸下去用脚划拉,还要拖着车,反受其累。

当然,如果Verilog的RTL不是汽车,而是自行车,屁股坐在上面,还是要用脚踩,那就是另一回事了。这个意思是说,Verilog的RTL确实有必须要NBA来表达的模型。

如果没有NBA,那么Assignment只有两种:用于wire的continous assignment和用于reg的procedural assignment,相当好理解。增加了Non-Blocking Assignment之后就大大的复杂化了。

如果需要把DFF拆开看值的传递,则层次处在Gate and Switch层,这个时候考虑a和b值交换不需要临时变量是何时的。

如果在RTL层,DFF已经被抽象出来了,是一个简单的reg变量。就像物理题里面一个物体被抽象成了一个点,那他的长宽高就不需要再考虑了。