一、设计思想与验证方法

1、 设计定义

2、 设计输入

3、 分析和综合

4、 功能仿真—modelsim

5、 布局布线

6、 时序仿真—modelsim

7、 时序约束

8、 IO分配以及配置文件的生成

9、 配置(烧写FPGA)

10、在线调试

二、实验要求

两个的输入IO,a,b

输入按键按下,Led灯与a端口状态保持一致

按键释放时,Led灯与b端口保持一致

三、源码

module led_test(a,b,key_in,led_out); input a; //输入端口a input b; //输入端口b input key_in; //按键输入端口 output led_out; //led输出端口 //按下 led_out==a assign led_out= (key_in==0)? a:b ; endmodule

`timescale 1ns/1ps // 时间单位/时间精度 module led_test_tb; //激励信号定义,对应连接到待测试模块的输入端口 reg signal_a; reg signal_b; reg signal_c; //待检测信号定义(led_out),对应链接到输出端口 wire led; //例化待测试模块 led_test led_test0( .a(signal_a), .b(signal_b), .key_in(signal_c), .led_out(led) ); //产生激励 initial begin signal_a=0; signal_b=0; signal_c=0; #100 signal_a=0; signal_b=0; signal_c=1; #100 signal_a=0; signal_b=1; signal_c=0; #100 signal_a=0; signal_b=1; signal_c=1; #100 signal_a=1; signal_b=0; signal_c=0; #100 signal_a=1; signal_b=0; signal_c=1; #100 signal_a=1; signal_b=1; signal_c=0; #100 signal_a=1; signal_b=1; signal_c=1; #200 $stop; //系统函数,停止 end endmodule

四、软件具体操作步骤(Quartus II 13.0 / modelsim 装新版即可)

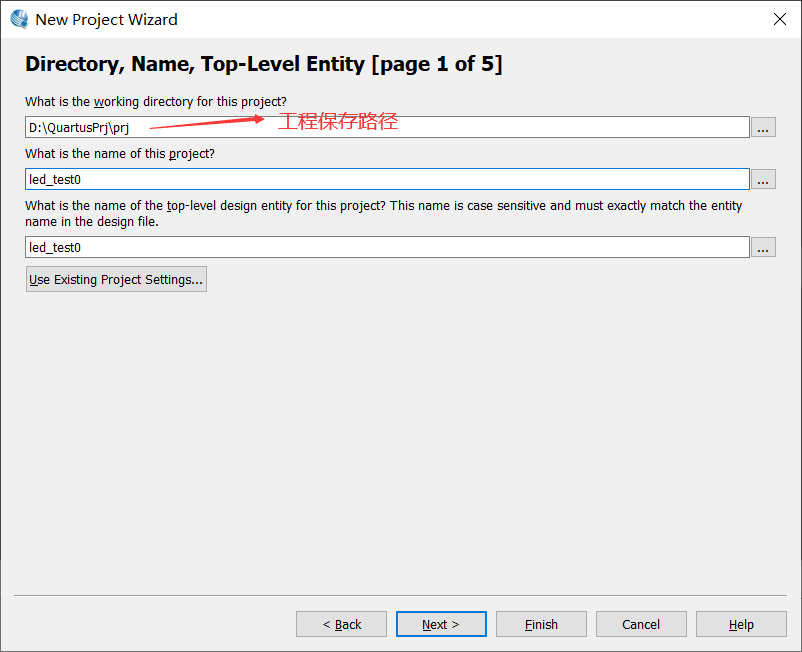

1.打开quartus 新建一个工程

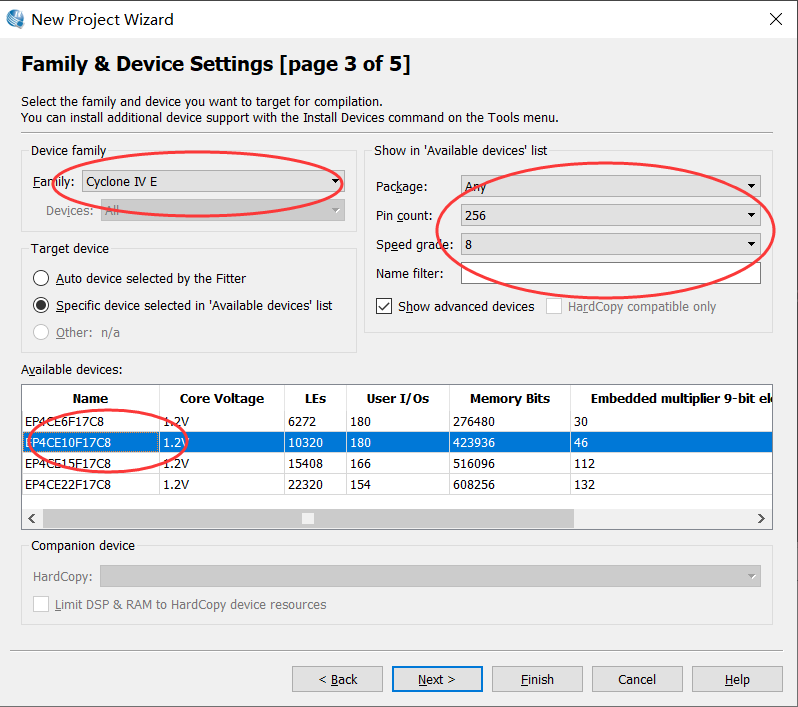

如果有现成的文件,添加就行了,没有的话直接next,选择开发板配置,next

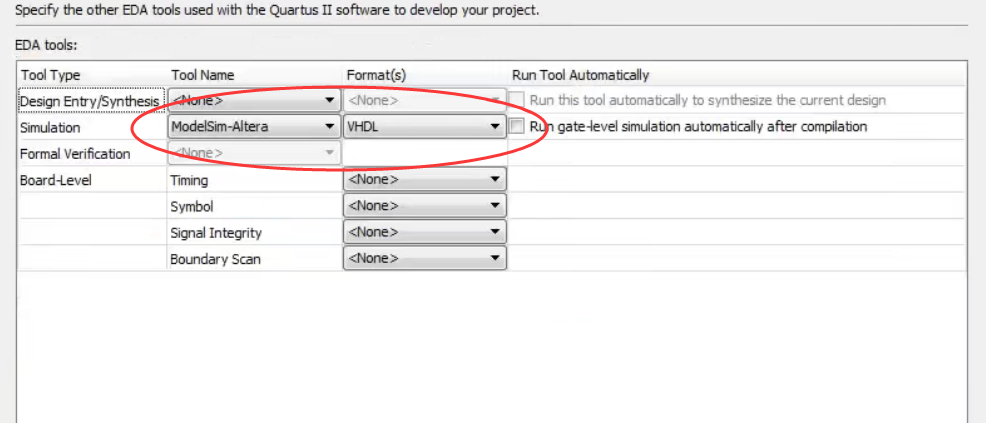

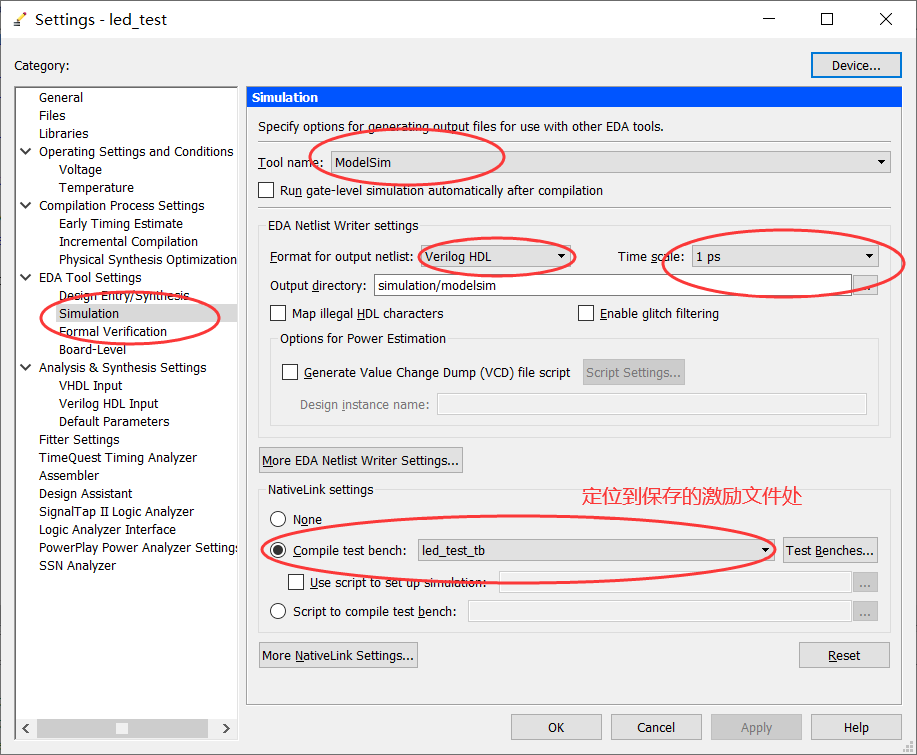

选择对应的仿真软件和语言(modelsim--Verilog),finish

2.新建两个verilog文件,设计文件+激励文件,ctrl+s 保存到本地

3.运行代码

分别对两个文件进行分析和综合,看是否有语法错误

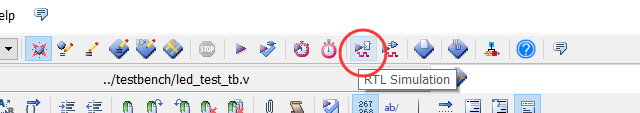

4.功能仿真--RTL simulation

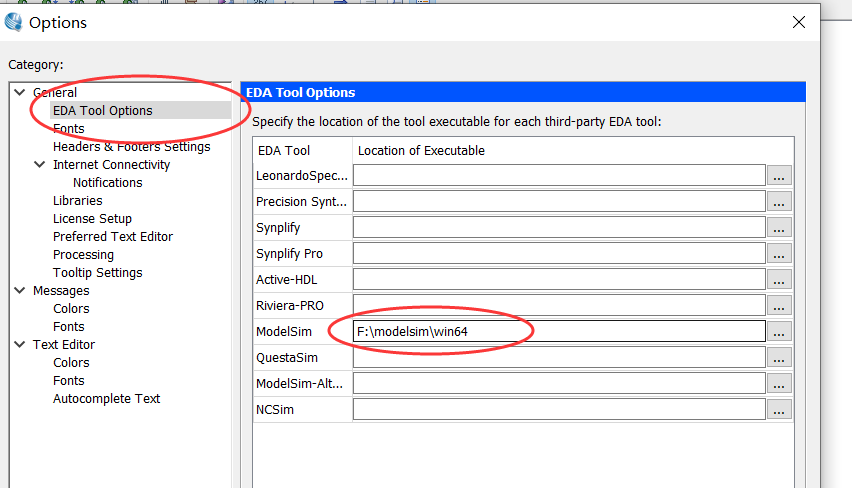

设置仿真软件路径,定位到仿真软件所在文件夹下,软件为modelsim,即如图

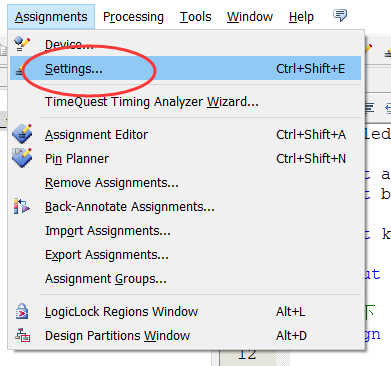

设置脚本,综合运行

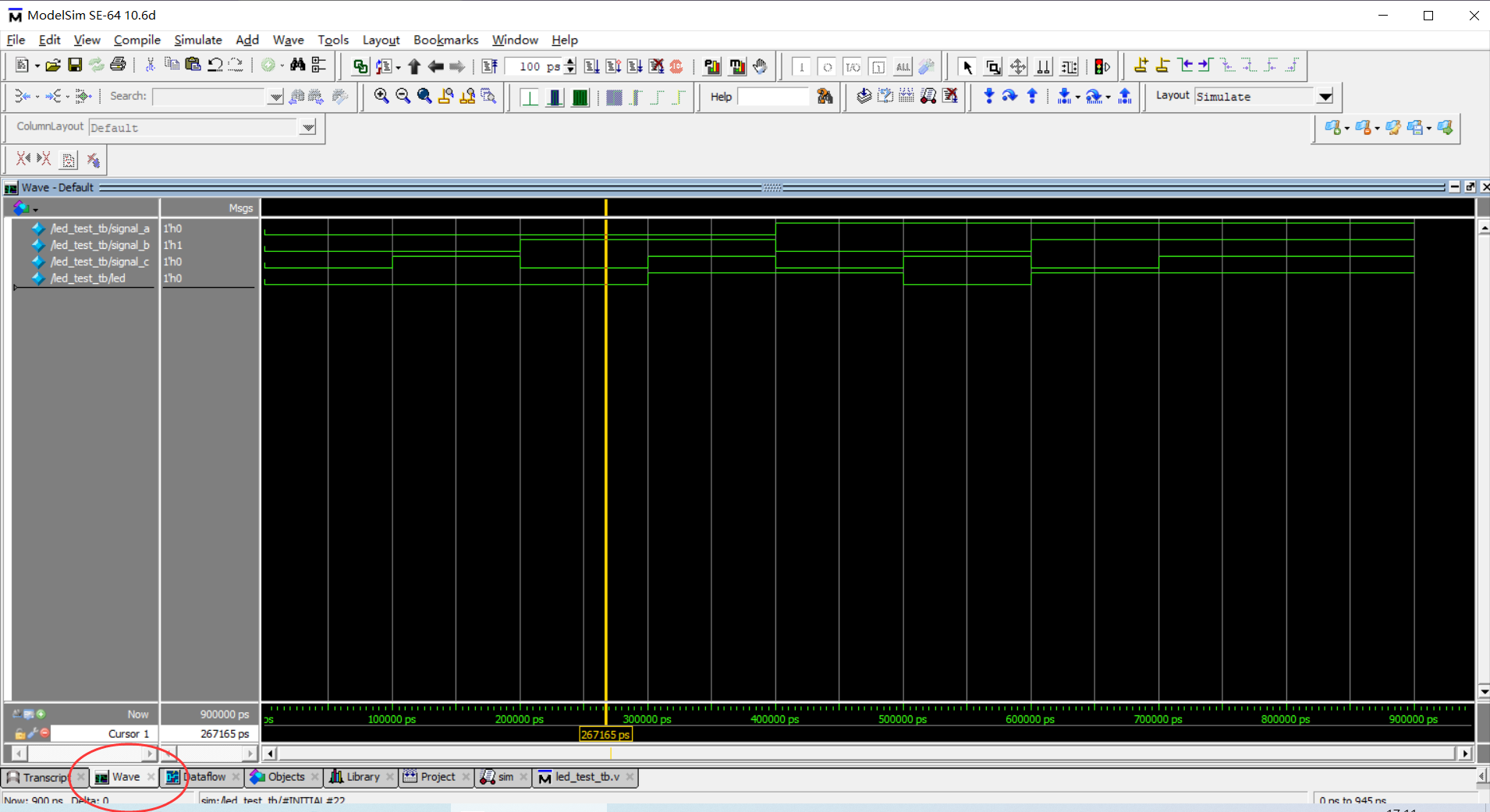

产生波形,按F键查看全局,如图,说明从功能上来说可实现,关闭仿真软件即可

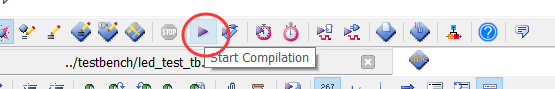

5.布局布线--start compilation

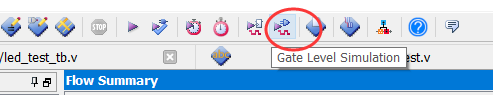

6.后仿真(时序仿真)直接选择最恶劣环境下运行--gate level simulation

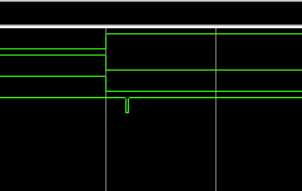

发现有误差脉冲(暂时忽略,后续学习再解决)

这里电平变化出现延时

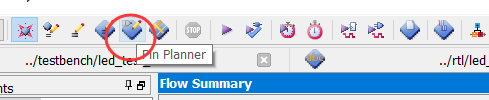

7.假设误差可忽略,进行IO分配(管脚分配)--pin planner

网上搜电路板对应的管脚,和信号对应即可

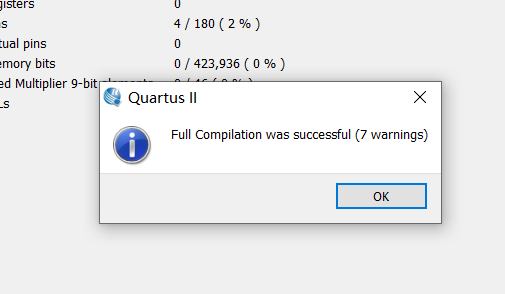

再进行一次全编译--start compilation,生效管脚分配

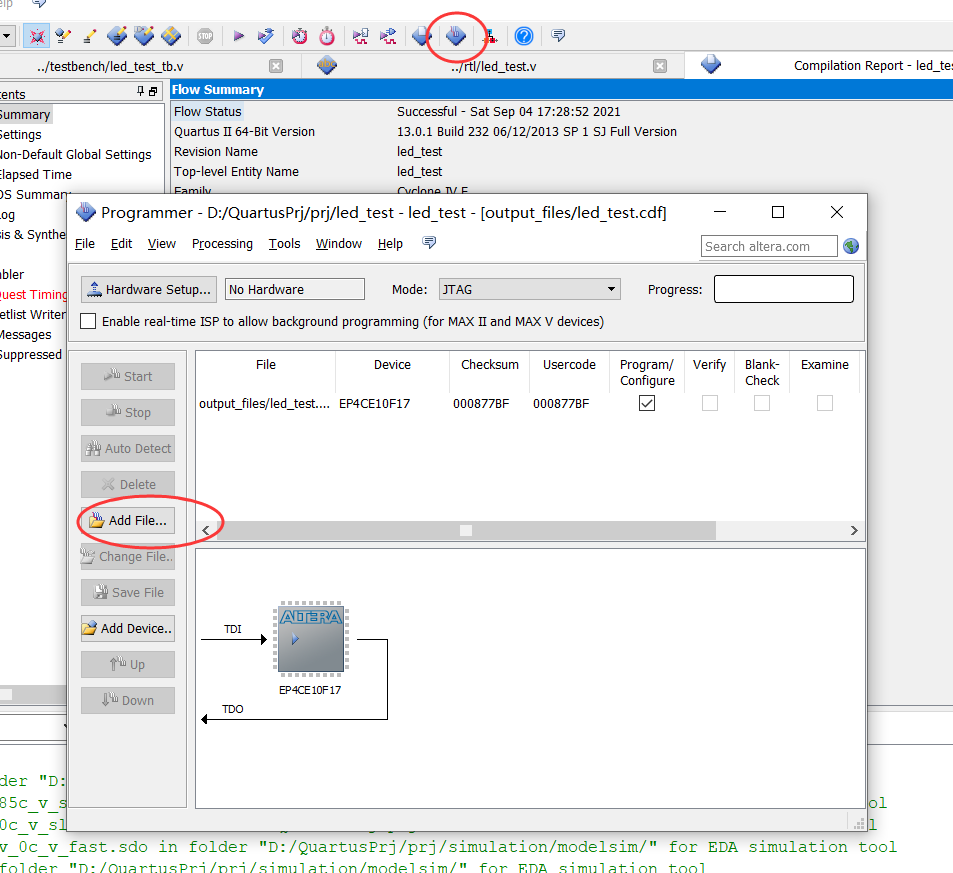

点击programmer进行下载,如果没有弹出框中没有文件,也可以手动添加sof文件

若没有生成sof文件,可能是软件破解有问题,重新破解一遍