1、验证一个设计的步骤:

生成输入激励,捕捉输出响应,决定对错和进度

2、连接设计和测试平台

信号连接:SystemVerilog已经扩展了传统的reg类型,可以像wire那样用来连接模块,它的新名字为logic,logic不能多驱动。

-缺点:使用信号连接极易出错。

接口:接口可以看作是一捆智能的连线,在接口中使用modport结构能够将信号分组并指定方向,使用时钟块可以指定同步信号相对于时钟的时序。将接口中的信号定义为logic,则可以直接被过程赋值语句驱动,wire类型只能被连续赋值语句驱动。

-优点:使得连接变得简洁不易出错,要增加一个信号时,在接口中只需要声明一次,不需要再更高层的模块层中声明。

3、接口中的双向信号用wire,单向信号用logic

4、module和program

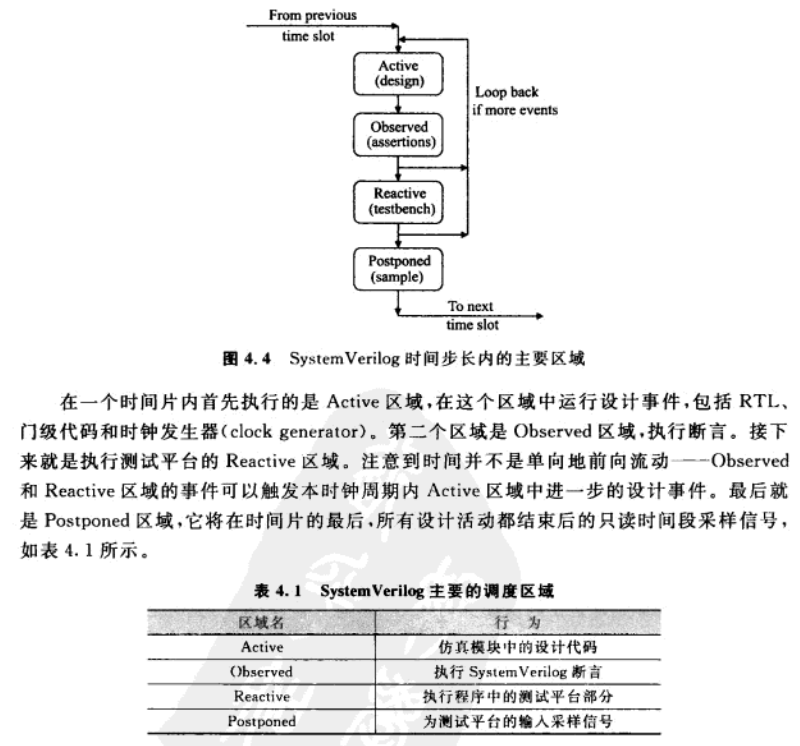

在模块module里描述设计,在program里搭建测试平台,再用接口把它们连接起来。程序块可以读写模块中的所有信号,可以调用模块中的所有例程,但是模块看不到程序块。这是因为测试平台需要访问和控制设计,但是涉及却独立于测试平台中的任何东西。程序块可以减少待测器件和测试平台之间的竞争状态:

5、接口采样和驱动

接口信号采样:当你从时钟块中读取一个信号的时候,你是在时钟沿之前得到采样值

接口信号驱动:当在modport中使用时钟块时,任何同步接口信号都必须加上接口名(arbif)和时钟块名(cb)的前缀,如arbif.cb.request

通过时钟块驱动接口信号:如果测试平台在时钟的有效沿驱动同步接口信号,那么其值会立即传递到设计中。这是因为时钟块的默认输出延时是 #0。如果测试平台在时钟有效沿之后驱动输出,那么该值直到时钟的下一个有效沿才会被捕获。在时钟块中应当使用同步驱动(synchronous drive),即“<=”来驱动信号。

6、示例

interface:

`timescale 1ns/1ns interface arb_if(input bit clk); logic [1:0] grant,request; logic rst; clocking cb @(posedge clk); output request; input grant; endclocking modport TEST (clocking cb, output rst); modport DUT (input request,rst, output grant); endinterface

module:

`timescale 1ns/1ns module arb(arb_if.DUT arbif); initial begin #7 arbif.grant <= 1; #10 arbif.grant <= 2; #8 arbif.grant <= 3; $display("@%0t:arbif.request=%b",$time,arbif.request); end endmodule

program:

`timescale 1ns/1ns program automatic test(arb_if.TEST arbif); initial begin #7 arbif.cb.request <= 3; //$display("@%0t:Drive req=3",$time); #10 arbif.cb.request <= 2; //$display("@%0t:Drive req=2",$time); #8 arbif.cb.request <= 1; //$display("@%0t:Drive req=1",$time); $display("@%0t:arbif.cb.grant = %b",$time,arbif.cb.grant); repeat (3) @arbif.cb; #50ns; end endprogram

top:

`timescale 1ns/1ns module top; bit clk; always #5 clk = !clk; arb_if arbif(clk); arb a1 (arbif.DUT); test t1 (arbif.TEST); endmodule

7、示例输出

# @25:arbif.request=11

# @25:arbif.cb.grant = 10

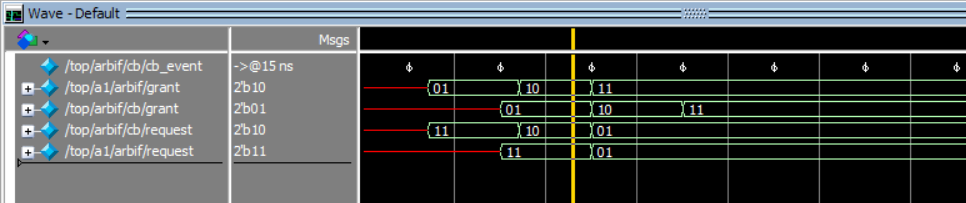

可以看到,arbif.cb.grant在时钟上升沿之前获得数值,当接口的输入信号恰好在时钟沿(25ns)变化(top.a1.arbif.grant:10-11)的时候,信号的新值在下一个时钟上升沿(35ns)传递给测试平台(top.arbif.cb.grant)。

如果测试平台在时钟的有效沿(25ns)驱动同步接口信号(top.arbif.cb.request: 10-01),那么其值会立即传递到设计(top.a1.arbif.request)中: arbif.request没有采到10数据,直接采到01数据.

总结来说就是,测试平台通过接口驱动设计是“立即”的,但是测试平台通过接口采样数据不是“立即”的

7、断言

分为立即断言、并发断言

`timescale 1ns/1ns program assert_test(); initial begin bit a; a <= 0; #10; a1:assert (a==1) else $error("customized error message"); end endprogram

# ** Error: customized error message

# Time: 10 ns Scope: assert_test.#ublk#168691044#3.a1 File: D:/MyFiles/code_and_projects/ModelSim/sv_test4.sv Line: 8

# ** Note: implicit $finish from program

# Time: 10 ns Iteration: 0 Instance: /assert_test

8、结论

(1)接口可以取代很多的信号连接,使代码更加容易维护和修改,还可以减少出错。

(2)程序块可以减少待测器件和测试平台之间的竞争状态。

(3)在接口中使用modport进行信号分组,使用时钟块使得测试平台能够相对于时钟正确地驱动和采样设计信号。