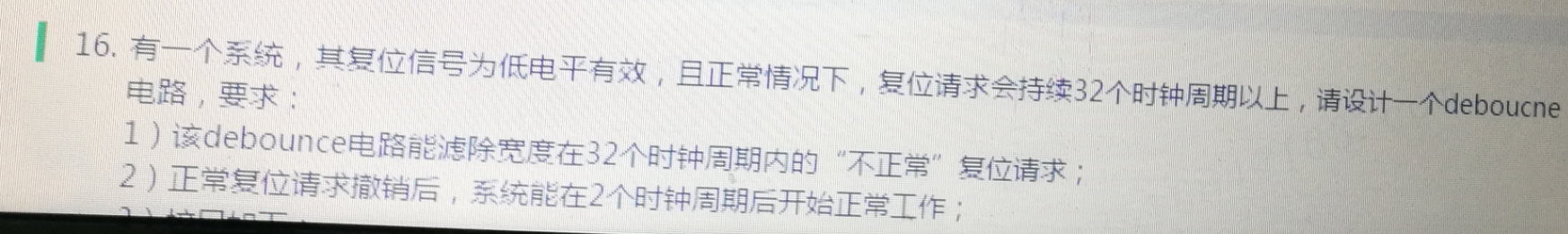

原题

题目理解

该题目有2个要求,首先是要对输入的rstn_i进行过滤,小于等于32个时钟周期的当作“不正常”复位请求;另外,正常复位请求撤销后,也就是有效的rstn_i恢复高电平后,rstn_o能够在2个时钟周期后恢复高电平。

代码思路

1、外围rstn_i作为异步信号,需要进行打2拍处理,缓解亚稳态;由于此处已经对rstn_i打了2拍,按照题目要求,正常复位撤销后,rstn_o能够在2个时钟周期后恢复高电平,因此rstn_o由低到高的跳变与rstn_reg2必须一致,assign rstn_o = (count==6'd32 && rstn_reg2==1'b0)? 1'b0 : 1'b1; 的判断条件有rstn_reg2==1'b0, 不加这个的话rstn_o在正常复位撤销后需要3个时钟周期后才能恢复高电平

2、设置一个计数器对打拍后的rstn_reg2进行统计,只要检测到高电平,计数清零,否则计数加1,直到32

代码

`timescale 1ns / 1ps

module rstn_allwinner(

input clk,

input rstn_i,

output rstn_o

);

reg rstn_reg1,rstn_reg2;

reg [5:0] count;

always @(posedge clk) begin

{rstn_reg1,rstn_reg2} <= {rstn_i,rstn_reg1};

end

always @(posedge clk) begin

if(rstn_reg2) count <= 6'd0;

else begin

if(count == 6'd32) count <= count;

else count <= count + 1'b1;

end

end

assign rstn_o = (count==6'd32 && rstn_reg2==1'b0)? 1'b0 : 1'b1;

endmodule

仿真波形

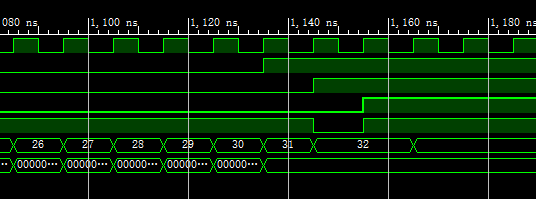

1、rstn_i持续31个周期,rstn_o无复位动作

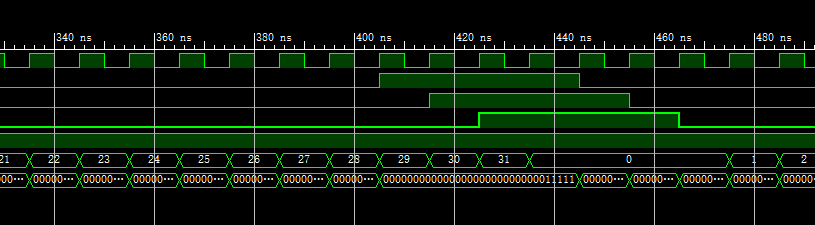

2、rstn_i持续32个周期,rstn_o仍无复位动作

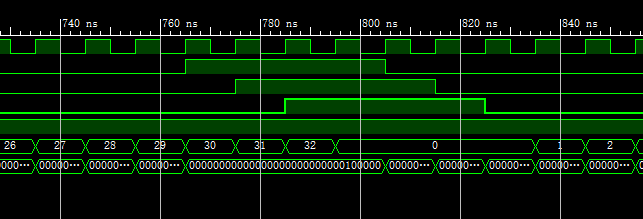

3、rstn_i持续33个周期,rstn_o产生复位动作