线网(net)作为Verilog语言中两种主要数据类型之一(变量数据类型和线网数据类型),主要用来模拟数字设计中连接多个不同模块或者模型的物理连线,因此线网是不存储数据的(除了trireg类型),仿真时线网上显示的数据由驱动该线网的驱动源决定的。如果线网没有被有效驱动,那么其上表现出来的数据是高阻态(除了trireg)。同时同一个模块中不允许对同一个线网进行多次声明。

在仿真验证的过程中经常会遇到未声明的标识符在仿真过程中有时会报出错误信息或者警告信息,但是有时又不会出现任何信息,那么在什么情况下会给出对未声明的标识符的相关错误或者警告信息呢?本文将以示例进行讨论。

针对未声明标识符在具体设计中出现的具体位置,我们进行了以下几方面的仿真验证:

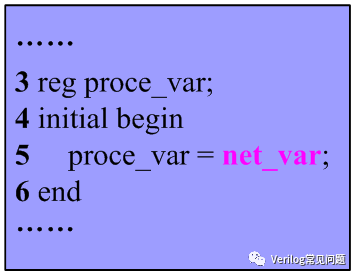

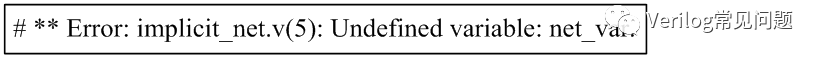

1.在过程性赋值语句中,未声明的标识符出现在表达式左侧或者右侧,示例如下:

编译结果如下:

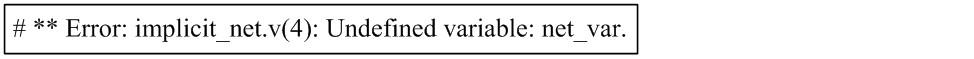

2.在连续赋值语句中,未声明标识符出现在表达式右侧,示例如下:

编译结果如下:

3.连续赋值语句中,未声明标识符出现在表达式左侧,示例如下:

编译过程未给出任何违例信息。

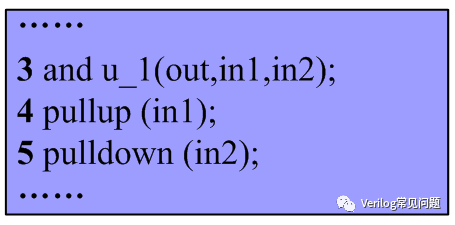

4.在模块的连接过程中,如果连接模块的线网没有进行声明,示例如下:

编译过程未给出任何违例信息。

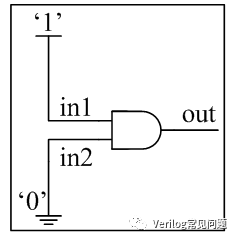

但是,连接模块的线网如果使用不当尽管在编译的过程中不会给出任何违例信息,但是将会导致逻辑功能的异常。如下例设计意图是将拉高的in1与拉低的in2进行“&”操作后输出值out,代码示例如上述第4条代码示例,电路结果示意图如下:

如果在编写代码的过程中,将连接and门的in1(spelled“in-one”)写错为inl(spelled“in-ell”),因为模块例化时未声明的线网将会隐含其已经声明,即编译仿真时将不会报错,但是实际上与门的in1并没有连接到高电平上,那么可想而知与门的输出必然不是期望的结果。

当然如果正确使用Verilog这种对于未声明的线网的隐性声明的特点,也会在某种程度上简化设计,特别是在较大的设计或者网表中。但是基于良好的设计风格,建议在设计的过程中凡是使用到的变量或者线网都要“事出有因”。

更多资讯,请关注个人公众号:芯光灿烂