一:纹波计数器

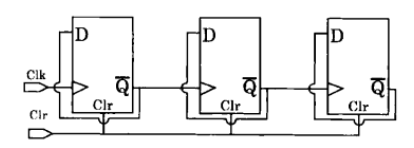

1:纹波计数器的面积最小,易于结构化实现。这种计数器的触发器是前一级输出数据的边沿作为时钟来驱动。前一级的输出连在后一级的时钟端,每当时钟的输入端口的数据产生了上升沿,输出就会翻转。这个计数器必须从一个确定的状态开始工作,这要求我们要对它复位,否则,计数器的翻转则没有意义。3比特的纹波计数器如下图所示,输出位Q[0],Q[1],Q[2](图中未标出)

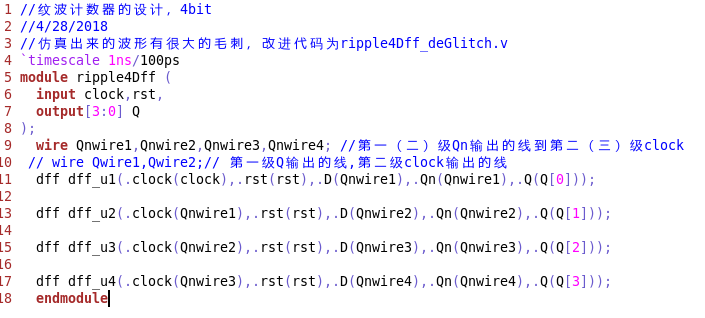

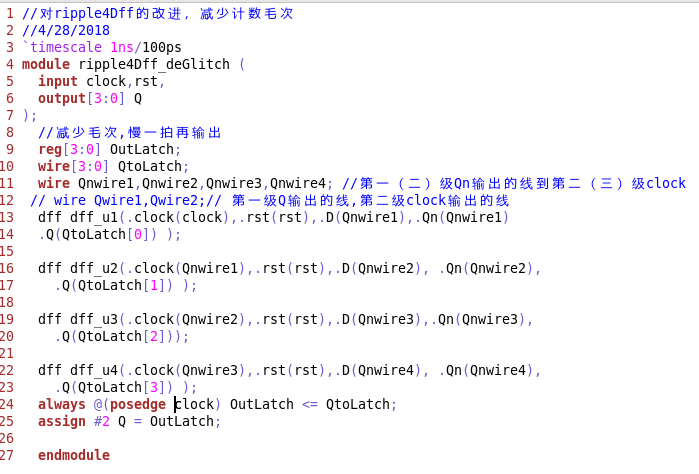

2:代码(4bit纹波计数器)

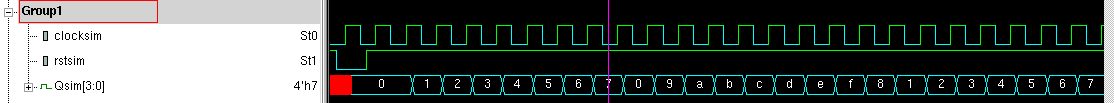

vcs dump的波形

可见,毛刺很大;这是因为纹波计数器中高阶触发器没有时钟,只有等到低阶触发器的输出变化后才能变化,所以当计数器的位宽增大时,这是个线性渐慢器件。在每个时钟上升沿之后,触发器的输出端会出现很多毛刺。然而,各阶的进位不会立刻由时钟传输下去,因此和同步计数器相比,功耗和噪声都减小了。

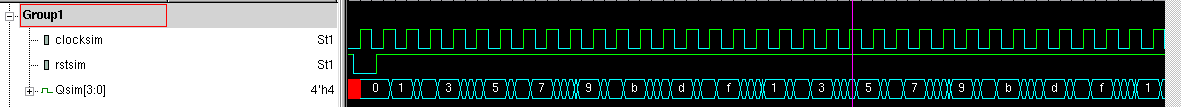

改进:慢一拍输出,使用锁存器将输出锁存一拍,再输出

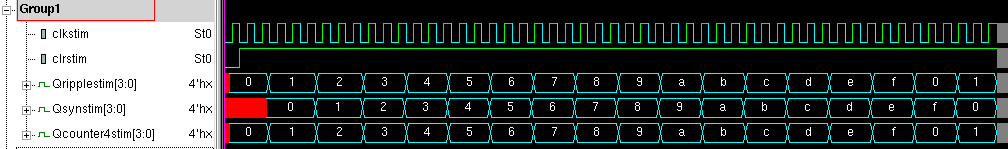

vcs dump的波形

可见,减少了毛刺,计数正常。

二:同步(超前进位)计数器

1:这类计数器增加了超前进位逻辑,在每个时钟有效沿对所有寄存器比特进行更新。

同步计数器偶尔会产生极大的瞬时功率,而这种尖峰功率会生成噪声。

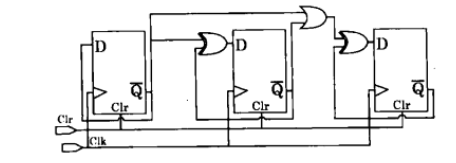

如下图,每个寄存单元的输入端口都是由1比特加法器(异或门)驱动;做设计的时候也应该遵循这个原则,组合逻辑后应该跟上寄存器以保证电路的时序。

时钟连在每个触发器的时钟端上,前面寄存器输出Q'端进行或操作,然后用异或门进行隔离,直到进位溢出该比特。

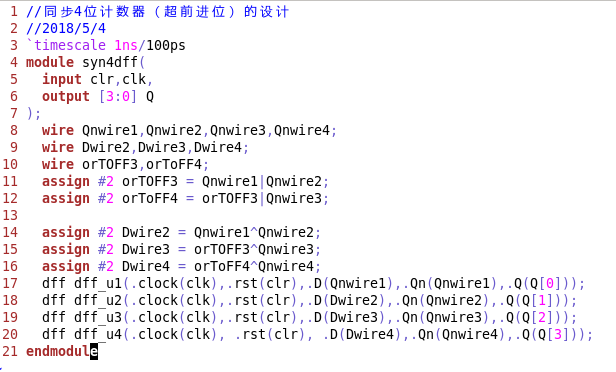

2:代码(4bit同步计数器)

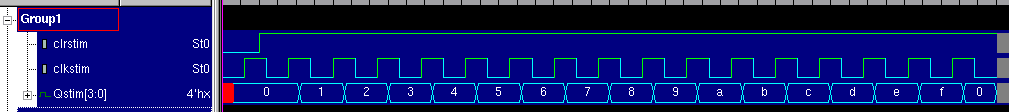

vcs dump波形

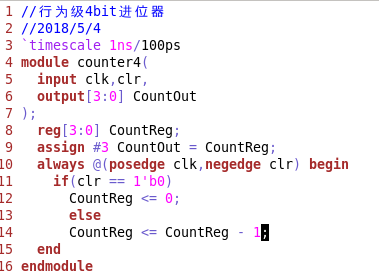

三:行为级计数器

1:4bit行为级计数器代码

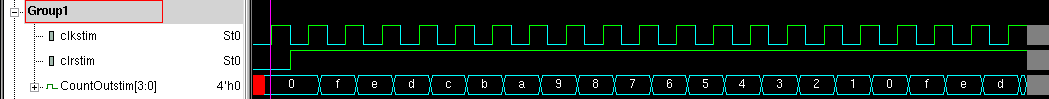

vcs dump波形

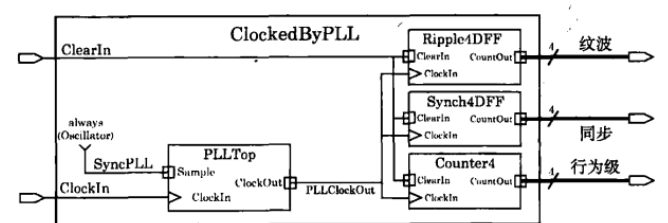

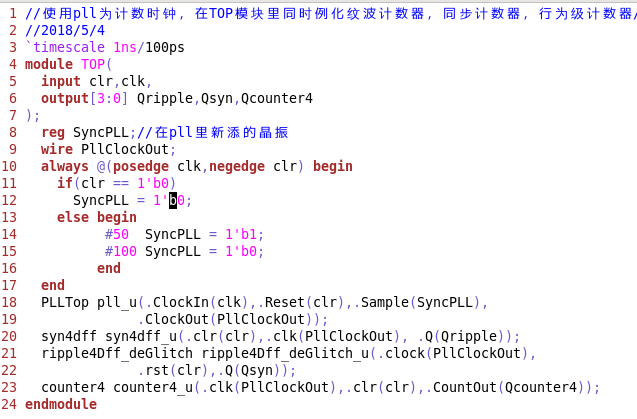

四:使用pll时钟,将以上三个计数器放在一起,看计数快慢

顶层文件代码

dump 波形

可见,同步计数器计数最慢