一、GPIO原理

1.GPIO介绍

程序员通过软件代码可以独立和动态地对每个 GPIO 进行控制,使其作为输入、输出或中断。

(1)通过一个加载指令,软件可以读取一个 GPIO 组内所有 GPIO 的值。

(2)通过一个保存指令,将数据写到一个 GPIO 组内的一个或多个 GPIO 。

(3)在 ZYNQ-7000 SOC 内,GPIO 模块的控制寄存器和状态寄存器采用存储器映射方式,它的基地址为 0xE000_A000。

(4)每个GPIO都提供了可编程的中断。通过软件程序代码可以实现:①读原始和屏蔽中断的状态;②可选的敏感性,包括电平敏感或边沿敏感。

2.MIO与EMIO的异同

MIO(multiuse I/O):多功能IO接口,属于Zynq的PS部分,Zynq7000 系列芯片有 54 个 MIO。它们分配在 GPIO 的 Bank0 和 Bank1 上,这些引脚可以用在GPIO、SPI、UART、TIMER、Ethernet、USB等功能上,每个引脚都同时具有多种功能,故叫多功能IO接口。这些 IO 与 PS 直接相连。不需要添加引脚约束,MIO 信号对 PL部分是透明的,不可见。所以对 MIO 的操作可以看作是纯 PS 的操作。GPIO 的控制和状态寄存器基地址为:0xE000_A000,我们 SDK 下软件操作底层都是对于内存地址空间的操作。

EMIO(extendable multiuse I/O):扩展MIO,依然属于Zynq的PS部分,只是连接到了PL上,再从PL的引脚连到芯片外面实现数据输入输出。Zynq7000 系列芯片有 64 个 EMIO,它们分配在 GPIO 的 Bank2 和 Bank3 上,当 MIO 不够用时,PS 可以通过驱动 EMIO 控制 PL 部分的引脚,EMIO 的使用相当于,是一个 PS + PL 的结合使用的例子。所以,EMIO 需要分配引脚以及编译综合生成 bit文件。

PS:

(1)由于总计有54个 MIO ,因此第1组 MIO 引脚限制为22位。

(2)尽管 MIO 和 EMIO 组之间存在功能差异,但是对每组 GPIO 的控制是相同的。

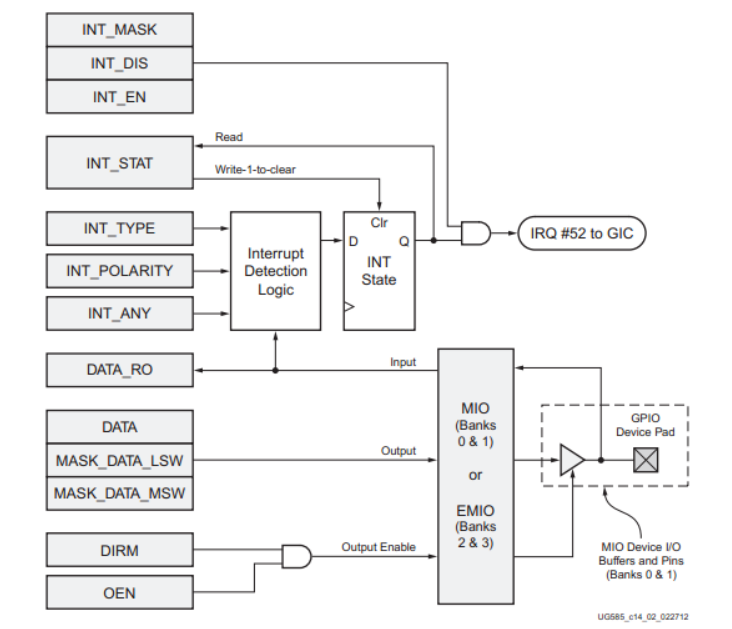

3.GPIO接口及功能

DATA_RO: 此寄存器使能软件观察 PIN 脚,当 GPIO 被配置成输出的时候,这个寄存器的值会反应输出的 PIN 脚情况。 DATA: 此寄存器控制输出到 GPIO 的值,读这个寄存器的值可以读到最后一次写入该寄存器的值。 MASK_DATA_LSW: 位操作寄存器,写入 GPIO 低 16bit 其他没有改变的位置保存原先的状态 MASK_DATA_MSW: 位操作寄存器,写入 GPIO 高 16bit 其他没有改变的位置保存原先的状态 DIRM: 此寄存器控制输出的开关,当 DIRM[x]==0 时候,禁止输出 OEN: 输出使能,当 OEN[x]==0 的时候输出关闭,PIN 脚处于三态因此,如果要读 IO 状态就得读 DATA_RO 的值,如果是对某一位进行操作就是写MASK_DATA_LSW/MASK_DATA_MSW

二、注意事项

相对于MIO,EMIO有几点要注意的地方:

1.EMIO 在 PL 部分,输入与 OEN 寄存器无关,当 DIRM 设置为 0 的时候设置为输入可以读 DATA_RO 寄存器获取数据。

2.输出不能设置成三态,当 DIRM 设置为 1 的时候为输出,写入 DATA 寄存器或者MASK_DATA_LSW/MASK_DATA_MSW 寄存器。

3.EMIOGPIOTN[x]=DIRM[x] & OEN[x],实现输出的控制。

三、配置上的区别

如果只是简单的使用,那MIO和EMIO在编程上没有太大区别,在配置上则有一些需要注意的地方。

1.MIO

ZYNQ配置时,在 MIO Configuration 选项卡对需要使用的MIO进行勾选即可。具体操作在前篇博客《ZYNQ笔记(2):PS端——Hello World !》 中已经详细说明。

2.EMIO

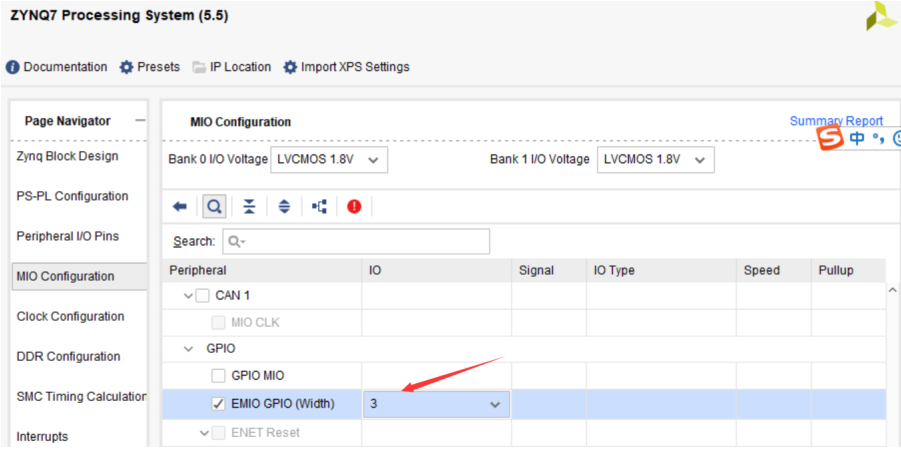

①ZYNQ配置时,在 MIO Configuration 选项卡,再看到 I/O Peripherals 中的 GPIO 一栏,勾选上其中的 EMIO 一栏,并选择 n 位引脚输出(最多可以选择 64 位)。

②ZYNQ配置完成后,ZYNQ系统多出一组引脚名为GPIO_0,这就是我们配置的EMIO,右击该引脚,选择 make external 把其引出。也可以对其更改名字。

③ZYNQ配置完成后,还需要对使用的EMIO引脚进行约束,即如PL端操作一样用XDC文件编写约束语句。

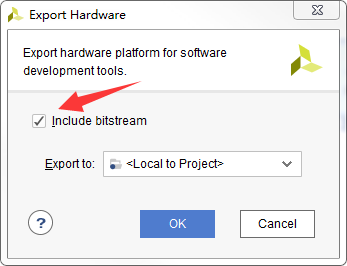

④配置完成后,必须生成bit流文件,并以此来加载SDK开发环境。

四、代码精讲

在 Xilinx 的 SDK 工具中,提供了对 GPIO 控制器进行操作的函数,这些 API 函数在 xgpiops.h 头文件中。

(1) XGpioPs_Config * XGpioPs_LookConfig(u16 DeviceID) 根据唯一的设备ID号DeviceID,该函数查找设备配置。根据该号,该函数返回一个配置表路口。

(2) u32 XGpioPs_CfgInitialize(XGpioPs * InstancePtr, XGpioPs_Config * ConfigPtr, u32 EffectiveAddr) 该函数用于初始化一个GPiO实例,包括初始化该实例的所有成员。

(3) void XGpioPs_SetDirectionPin(XGpioP * InstancePtr, u32 Pin, u32 Direction) 该函数为指定的引脚设置方向。

(4) void XGpioPs_SetOutputEnablePin(XGpioPs * InstancePtr, u32 Pin, u32 OpEnable) 该函数设置指定引脚的输出使能

(5) u32 XGpioPs_ReadPin(XGpioPs * InstancePtr, u32 Pin) 该函数从指定的引脚读取数据

(6) void XGpioPs_WritePin(XGpioPs * InstancePtr, u32 Pin, u32 Data) 该函数向指定的引脚写数据

参考资料:

[1]V3学院FPGA教程

[2]何宾, 张艳辉. Xilinx Zynq-7000嵌入式系统设计与实现[M]. 电子工业出版社, 2016.