IP核生成

Quartus生成DDR2 ip流程如下:

点击菜单栏的Tools->MegaWizard Plug-In Manager,弹出

选择IP类型,保持路径即文件名等,如下图

点击next,按下图设置:输入时钟50Mhz,DDR驱动时钟150Mhz,Full rate模式,位宽32Bit,器件选择MT47H64M16,与所使用的FPGA开发板一致。

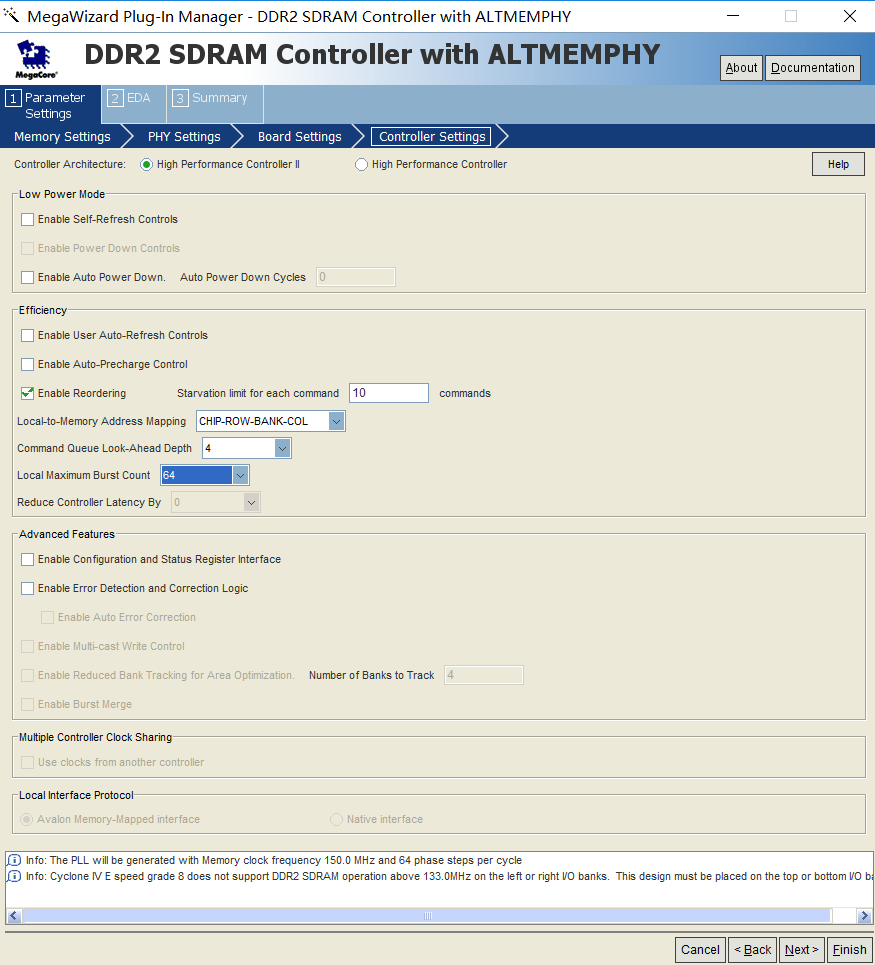

点next,选择默认即可

依旧默认

设置MaxBurstCount为64,

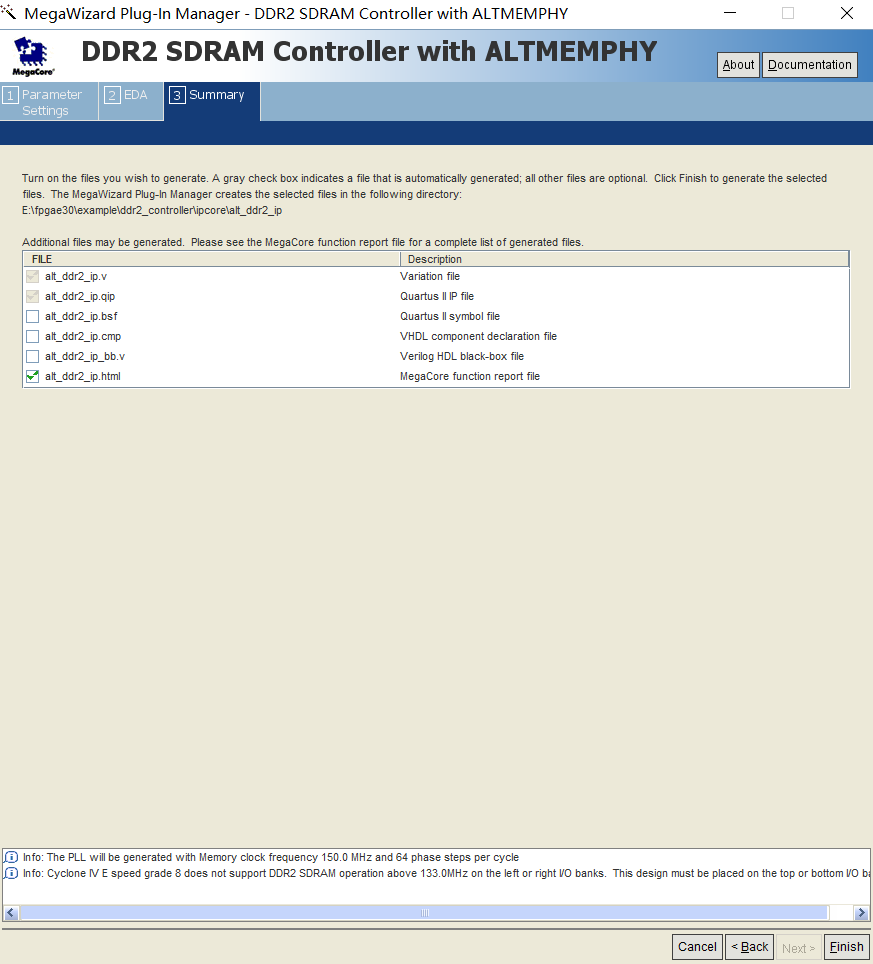

选择产生仿真模型

最后点击finish完成

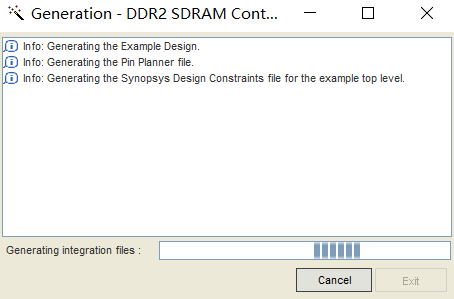

等待gereration

完成

以下是log信息

| Info: Generating the Example Design. Info: Generating the Pin Planner file. Info: Generating the Synopsys Design Constraints file for the example top level. Info: Generating the Synopsys Design Constraints file. Info: Generating the Timing Report script. Info: Generating the ALTPLL Megafunction instance. Info: Generating the ALTMEMPHY Megafunction instance. Info: Generating the Functional Simulation Model for ALTMEMPHY Info: Before compiling your variation in Quartus II, you should follow these steps: Info: - Enable TimeQuest under Settings, Timing Analysis Settings. Info: - Add the alt_ddr2_ip_phy_ddr_timing.sdc file to your Quartus II project. Info: - Add I/O Standard assignments by running the alt_ddr2_ip_pin_assignments.tcl script. Info: - Set the Default I/O standard to match the memory interface I/O standard setting. Info: - Turn on Optimize multi-corner timing in the Quartus II Fitter Settings. Info: - Please make sure that address/command pins are placed on the same edge as the CK/CK# pins. Info: - Set the top level entity of the project to alt_ddr2_ip_example_top. Info: See the User Guide for more details. |