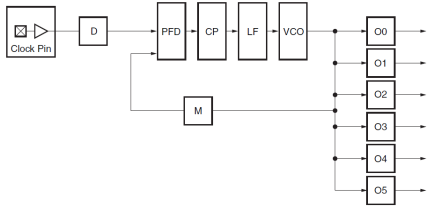

锁相环(PLL)主要用于频率综合,使用一个 PLL 可以从一个输入时钟信号生成多个时钟信号。 PLL 内部的功能框图如下图所示:

在ISE中新建一个PLL的IP核,设置四个输出时钟,分别为25MHz、50MHz、75MHz和100MHz,配置如图所示:

之后,再在程序中例化IP核,程序设计如下:

1 `timescale 1ns / 1ps 2 ////////////////////////////////////////////////////////////////////////////////// 3 // Company: 4 // Engineer: 5 // 6 // Create Date: 11:11:34 03/26/2018 7 // Design Name: 8 // Module Name: pll_test 9 // Project Name: 10 // Target Devices: 11 // Tool versions: 12 // Description: 13 // 14 // Dependencies: 15 // 16 // Revision: 17 // Revision 0.01 - File Created 18 // Additional Comments: 19 // 20 ////////////////////////////////////////////////////////////////////////////////// 21 module pll_test( 22 input clk, 23 input reset, 24 output pll_clk_1, 25 output pll_clk_2, 26 output pll_clk_3, 27 output pll_clk_4, 28 output locked 29 ); 30 31 pll_ip pll_ip_inst 32 ( 33 .CLK_IN1(clk), // IN 50Mhz 34 // Clock out ports 35 .CLK_OUT1(pll_clk_1), // OUT 25Mhz 36 .CLK_OUT2(pll_clk_2), // OUT 50Mhz 37 .CLK_OUT3(pll_clk_3), // OUT 75Mhz 38 .CLK_OUT4(pll_clk_4), // OUT 100Mhz 39 // Status and control signals 40 .RESET(reset),// IN 41 .LOCKED(locked)// OUT 42 ); 43 endmodule

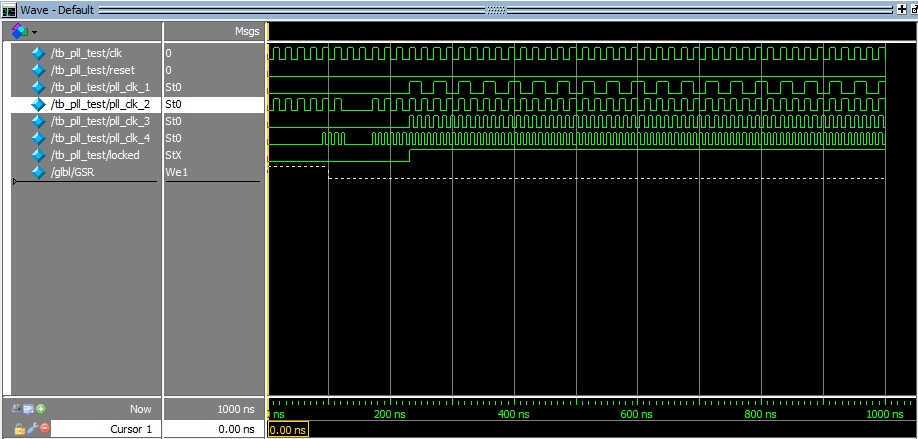

仿真结果;

可以看到,锁相环的IP核是高电平复位,当所有的输出时钟都稳定之后,locked信号拉高,这时之后的输出时钟可用。