什么是内存条

先来张图,有个直观的认识

内存条就是我们通常说的计算机的内存,也就是计算机的主存。我们通常所说电脑内存的大小,即是指内存条的总容量。它是计算机里的RAM的一种。是电脑必不可少的组成部分,CPU通过地址总线和数据总线跟它交互来实现数据的读写。CPU完全依赖内存条。所有外存上的内容必须通过内存才能发挥作用。

内存条的发展历史

诞生

起初,电脑所使用的内存是一块块的IC,我们必须把它们焊接到主机板上才能正常使用,一旦某一块内存IC坏了,必须焊下来才能更换,这实在是太费劲了。后来,电脑设计人员发明了模块化的条装内存,每一条上集成了多块内存IC,相应地,在主板上设计了内存插槽,这样,内存条就可随意拆卸了,从此,内存的维修和扩充都变得非常方便。

发展

内存芯片的状态一直沿用到286初期,鉴于它存在着无法拆卸更换的弊病,这对于计算机的发展造成了现实的阻碍。有鉴于此,内存条便应运而生了。将内存芯片焊接到事先设计好的印刷线路板上,而电脑主板上也改用内存插槽。这样就把内存难以安装更换的问题彻底解决了。

在80286主板发布之前,内存并没有被世人所重视,这个时候的内存是直接固化在主板上,而且容量只有64 ~256KB,对于当时PC所运行的工作程序来说,这种内存的性能以及容量足以满足当时软件程序的处理需要。不过随着软件程序和新一代80286硬件平台的出现,程序和硬件对内存性能提出了更高要求,为了提高速度并扩大容量,内存必须以独立的封装形式出现,因而诞生了“内存条”概念。

在80286主板刚推出的时候,内存条采用了SIMM(Single In-lineMemory Modules,单边接触内存模组)接口,容量为30pin、256kb,必须是由8 片数据位和1 片校验位组成1 个bank,正因如此,我们见到的30pin SIMM一般是四条一起使用。自1982年PC进入民用市场,搭配80286处理器的30pin SIMM 内存是内存领域的开山鼻祖。

随后,在1988 ~1990 年当中,PC 技术迎来另一个发展高峰,也就是386和486时代,此时CPU 已经向16bit 发展,所以30pin SIMM 内存再也无法满足需求,其较低的内存带宽已经成为急待解决的瓶颈,所以此时72pin SIMM 内存出现了,72pin SIMM支持32bit快速页模式内存,内存带宽得以大幅度提升。72pin SIMM内存单条容量一般为512KB ~2MB,而且仅要求两条同时使用,由于其与30pin SIMM 内存无法兼容,因此这个时候PC业界毅然将30pin SIMM 内存淘汰出局了。

EDO DRAM(Extended Date Out RAM,

IBM产,CANDA制造的EDO内存条

外扩充数据模式存储器)内存,这是1991 年到1995 年之间盛行的内存条,EDO-RAM同FP DRAM极其相似,它取消了扩展数据输出内存与传输内存两个存储周期之间的时间间隔,在把数据发送给CPU的同时去访问下一个页面,故而速度要比普通DRAM快15~30%。工作电压为一般为5V,带宽32bit,速度在40ns以上,其主要应用在当时的486及早期的Pentium电脑上。

在1991 年到1995 年中,让我们看到一个尴尬的情况,那就是这几年内存技术发展比较缓慢,几乎停滞不前,所以我们看到此时EDO RAM有72 pin和168 pin并存的情况,事实上EDO 内存也属于72pin SIMM 内存的范畴,不过它采用了全新的寻址方式。EDO 在成本和容量上有所突破,凭借着制作工艺的飞速发展,此时单条EDO 内存的容量已经达到4 ~16MB 。由于Pentium及更高级别的CPU数据总线宽度都是64bit甚至更高,所以EDO RAM与FPM RAM都必须成对使用。

自Intel Celeron系列以及AMD K6处理器以及相关的主板芯片组推出后,EDO DRAM内存性能再也无法满足需要了,内存技术必须彻底得到个革新才能满足新一代CPU架构的需求,此时内存开始进入比较经典的SDRAM时代。

第一代SDRAM 内存为PC66 规范,但很快由于Intel 和AMD的频率之争将CPU外频提升到了100MHz,所以PC66内存很快就被PC100内存取代,接着133MHz 外频的PIII以及K7时代的来临,PC133规范也以相同的方式进一步提升SDRAM 的整体性能,带宽提高到1GB/sec以上。由于SDRAM 的带宽为64bit,正好对应CPU 的64bit 数据总线宽度,因此它只需要一条内存便可工作,便捷性进一步提高。在性能方面,由于其输入输出信号保持与系统外频同步,因此速度明显超越EDO 内存。

不可否认的是,SDRAM 内存由早期的66MHz,发展后来的100MHz、133MHz,尽管没能彻底解决内存带宽的瓶颈问题,但此时CPU超频已经成为DIY用户永恒的话题,所以不少用户将品牌好的PC100品牌内存超频到133MHz使用以获得CPU超频成功,值得一提的是,为了方便一些超频用户需求,市场上出现了一些PC150、PC166规范的内存。

尽管SDRAM PC133内存的带宽可提高带宽到1064MB/S,加上Intel已经开始着手最新的Pentium 4计划,所以SDRAM PC133内存不能满足日后的发展需求,此时,Intel为了达到独占市场的目的,与Rambus联合在PC市场推广Rambus DRAM内存(称为RDRAM内存)。与SDRAM不同的是,其采用了新一代高速简单内存架构,基于一种类RISC(Reduced Instruction Set Computing,精简指令集计算机)理论,这个理论可以减少数据的复杂性,使得整个系统性能得到提高。

在AMD与Intel的竞争中,这个时候是属于频率竞备时代,所以这个时候CPU的主频在不断提升,Intel为了盖过AMD,推出高频PentiumⅢ以及Pentium 4 处理器,因此Rambus DRAM内存是被Intel看着是未来自己的竞争杀手锏,Rambus DRAM内存以高时钟频率来简化每个时钟周期的数据量,因此内存带宽相当出色,如PC 1066 1066 MHz 32 bits带宽可达到4.2G Byte/sec,Rambus DRAM曾一度被认为是Pentium 4 的绝配。

尽管如此,Rambus RDRAM 内存生不逢时,后来依然要被更高速度的DDR“掠夺”其宝座地位,在当时,PC600、PC700的Rambus RDRAM 内存因出现Intel820 芯片组“失误事件”、PC800 Rambus RDRAM因成本过高而让Pentium 4平台高高在上,无法获得大众用户拥戴,种种问题让Rambus RDRAM胎死腹中,Rambus曾希望具有更高频率的PC1066 规范RDRAM来力挽狂澜,但最终也是拜倒在DDR 内存面前。

DDR时代

DDR SDRAM(Dual DataRate SDRAM)简称DDR,

也就是“双倍速率SDRAM“的意思。DDR可以说是SDRAM的升级版本,DDR在时钟信号上升沿与下降沿各传输一次数据,这使得DDR的数据传输速度为传统SDRAM的两倍。由于仅多采用了下降缘信号,因此并不会造成能耗增加。至于定址与控制信号则与传统SDRAM相同,仅在时钟上升缘传输。

DDR 内存是作为一种在性能与成本之间折中的解决方案,其目的是迅速建立起牢固的市场空间,继而一步步在频率上高歌猛进,最终弥补内存带宽上的不足。第一代DDR200 规范并没有得到普及,第二代PC266 DDR SRAM(133MHz时钟×2倍数据传输=266MHz带宽)是由PC133 SDRAM内存所衍生出的,它将DDR 内存带向第一个高潮,另外还有不少赛扬和AMD K7处理器都在采用DDR266规格的内存,其后来的DDR333内存也属于一种过渡,而DDR400内存成为当下的主流平台选配,双通道DDR400内存已经成为800FSB处理器搭配的基本标准,随后的DDR533 规范则成为超频用户的选择对象。

DDR2时代

DDR2(Double Data Rate 2)SDRAM是由JEDEC(电子设备工程联合委员会)进行开发的新生代内存技术标准,它与上一代DDR内存技术标准最大的不同就是,虽然同是采用了在时钟的上升/下降延同时进行数据传输的基本方式,但DDR2内存却拥有两倍于上一代DDR内存预读取能力(即:4bit数据读预取)。换句话说,DDR2内存每个时钟能够以4倍外部总线的速度读/写数据,并且能够以内部控制总线4倍的速度运行。

此外,由于DDR2标准规定所有DDR2内存均采用FBGA封装形式,而不同于广泛应用的TSOP/TSOP-II封装形式,FBGA封装可以提供了更为良好的电气性能与散热性,为DDR2内存的稳定工作与未来频率的发展提供了坚实的基础。回想起DDR的发展历程,从第一代应用到个人电脑的DDR200经过DDR266、DDR333到今天的双通道DDR400技术,第一代DDR的发展也走到了技术的极限,已经很难通过常规办法提高内存的工作速度;随着Intel最新处理器技术的发展,前端总线对内存带宽的要求是越来越高,拥有更高更稳定运行频率的DDR2内存将是大势所趋。

随着CPU 性能不断提高,我们对内存性能的要求也逐步升级。不可否认,仅仅依高频率提升带宽的DDR迟早会力不从心,因此JEDEC 组织很早就开始酝酿DDR2 标准,加上LGA775接口的915/925以及最新的945等新平台开始对DDR2内存的支持,所以DDR2内存将开始演义内存领域的今天。

DDR2 能够在100MHz 的发信频率基础上提供每插脚最少400MB/s 的带宽,而且其接口将运行于1.8V 电压上,从而进一步降低发热量,以便提高频率。此外,DDR2 将融入CAS、OCD、ODT 等新性能指标和中断指令,提升内存带宽的利用率。从JEDEC组织者阐述的DDR2标准来看,针对PC等市场的DDR2内存将拥有400、533、667MHz等不同的时钟频率。高端的DDR2内存将拥有800、1000MHz两种频率。DDR-II内存将采用200-、220-、240-针脚的FBGA封装形式。最初的DDR2内存将采用0.13微米的生产工艺,内存颗粒的电压为1.8V,容量密度为512MB。

内存技术在2005年将会毫无悬念,SDRAM为代表的静态内存在五年内不会普及。QBM与RDRAM内存也难以挽回颓势,因此DDR与DDR2共存时代将是铁定的事实。

PC-100的“接班人”除了PC一133以外,VCM(VirXual Channel Memory)也是很重要的一员。VCM即“虚拟通道存储器”,这也是大多数较新的芯片组支持的一种内存标准,VCM内存主要根据由NEC公司开发的一种“缓存式DRAM”技术制造而成,它集成了“通道缓存”,由高速寄存器进行配置和控制。在实现高速数据传输的同时,VCM还维持着对传统SDRAM的高度兼容性,所以通常也把VCM内存称为VCM SDRAM。VCM与SDRAM的差别在于不论是否经过CPU处理的数据,都可先交于VCM进行处理,而普通的SDRAM就只能处理经CPU处理以后的数据,所以VCM要比SDRAM处理数据的速度快20%以上。可以支持VCM SDRAM的芯片组很多,包括:Intel的815E、VIA的694X等。

RDRAM

Intel在推出:PC-100后,由于技术的发展,PC-100内存的800MB/s带宽已经不能满足需求,而PC-133的带宽提高并不大(1064MB/s),同样不能满足日后的发展需求。Intel为了达到独占市场的目的,与Rambus公司联合在PC市场推广Rambus DRAM(DirectRambus DRAM),如图4-3所示。

Rambus DRAM是:Rambus公司最早提出的一种内存规格,采用了新一代高速简单内存架构,从而可以减少数据的复杂性,使得整个系统性能得到提高。Rambus使用400MHz的16bit总线,在一个时钟周期内,可以在上升沿和下降沿的同时传输数据,这样它的实际速度就为400MHz×2=800MHz,理论带宽为(16bit×2×400MHz/8)1.6GB/s,相当于PC-100的两倍。另外,Rambus也可以储存9bit字节,额外的一比特是属于保留比特,可能以后会作为:ECC(ErroI·Checking and Correction,错误检查修正)校验位。Rambus的时钟可以高达400MHz,而且仅使用了30条铜线连接内存控制器和RIMM(Rambus In-line MemoryModules,Rambus内嵌式内存模块),减少铜线的长度和数量就可以降低数据传输中的电磁干扰,从而快速地提高内存的工作频率。不过在高频率下,其发出的热量肯定会增加,因此第一款Rambus内存甚至需要自带散热风扇。

DDR3时代

DDR3相比起DDR2有更

低的工作电压,从DDR2的1.8V降落到1.5V,性能更好更为省电;DDR2的4bit预读升级为8bit预读。DDR3最高能够以2400Mhz的速度,由于最为快速的DDR2内存速度已经提升到800Mhz/1066Mhz的速度,因而首批DDR3内存模组将会从800Mhz的起跳。在Computex大展我们看到多个内存厂商展出1333Mhz的DDR3模组。

DDR3在DDR2基础上采用的新型设计:

1.8bit预取设计,而DDR2为4bit预取,这样DRAM内核的频率只有接口频率的1/8,DDR3-800的核心工作频率只有100MHz。

2.采用点对点的拓扑架构,以减轻地址/命令与控制总线的负担。

3.采用100nm以下的生产工艺,将工作电压从1.8V降至1.5V,增加异步重置(Reset)与ZQ校准功能。

DDR4时代

DDR4内存将会拥有两种规格。其中使用Single-endedSignaling信号的DDR4内存其传输速率已经被确认为1.6~3.2Gbps,而基于差分信号技术的DDR4内存其传输速率则将可以达到6.4Gbps。由于通过一个DRAM实现两种接口基本上是不可能的,因此DDR4内存将会同时存在基于传统SE信号和差分信号的两种规格产品。

根据多位半导体业界相关人员的介绍,DDR4内存将会是Single-endedSignaling( 传统SE信号)方式DifferentialSignaling( 差分信号技术 )方式并存。预计这两个标准将会推出不同的芯片产品,因此在DDR4内存时代我们将会看到两个互不兼容的内存产品

主要性能参数

评价内存条的性能指标一共有四个:

- 存储容量:即一根内存条可以容纳的二进制信息量,如常用的168线内存条的存储容量一般多为32兆、64兆和128兆。而DDRII3普遍为1GB到8GB。

- 存取速度(存储周期):即两次独立的存取操作之间所需的最短时间,又称为存储周期,半导体存储器的存取周期一般为60纳秒至100纳秒。

- 存储器的可靠性:存储器的可靠性用平均故障间隔时间来衡量,可以理解为两次故障之间的平均时间间隔。

- 性能价格比:性能主要包括存储器容量、存储周期和可靠性三项内容,性能价格比是一个综合性指标,对于不同的存储器有不同的要求。

- 奇偶性:为了保证内存存取数据的的准确性,有些内存条上有奇偶校验位,如3片或9片装的内存条。如果您对电脑运行的准确性要求很高,最好选择有奇偶校验功能的内存条。

认识内存条上的标签

这里只是拿一种内存条举例,不同厂商可能不一样

- 4GB---该内存条总容量

- 2RX8---由2排(面)组成,每排(面)八个内存颗粒(也就是存储芯片)

- PC3-10600S---代表DDR3,1333MHz的SO-DIMM

在80286时代,内存颗粒(Chip)是直接插在主板上的,叫做DIP(Dual In-line Package)。到了80386时代,换成1片焊有内存颗粒的电路板,叫做SIMM(Single-Inline Memory Module)。由阵脚形态变化成电路板带来了很多好处:模块化,安装便利等等,由此DIY市场才有可能产生。当时SIMM的位宽是32bit,即一个周期读取4个字节,到了奔腾时,位宽变为64bit,即8个字节,于是SIMM就顺势变为DIMM(Double-Inline Memory Module)。这种形态一直延续至今,也是内存条的基本形态。现在DIMM分为很多种:

RDIMM: 全称(Registered DIMM),寄存型模组,主要用在服务器上,为了增加内存的容量和稳定性分有ECC和无ECC两种,但市场上几乎都是ECC的。

UDIMM:全称(Unbuffered DIMM),无缓冲型模组,这是我们平时所用到的标准台式电脑DIMM,分有ECC和无ECC两种,一般是无ECC的。

SO-DIMM:全称(Small Outline DIMM),小外型DIMM,笔记本电脑中所使用的DIMM,分ECC和无ECC两种。

Mini-DIMM:DDR2时代新出现的模组类型,它是Registered DIMM的缩小版本,用于刀片式服务器等对体积要求苛刻的高端领域。

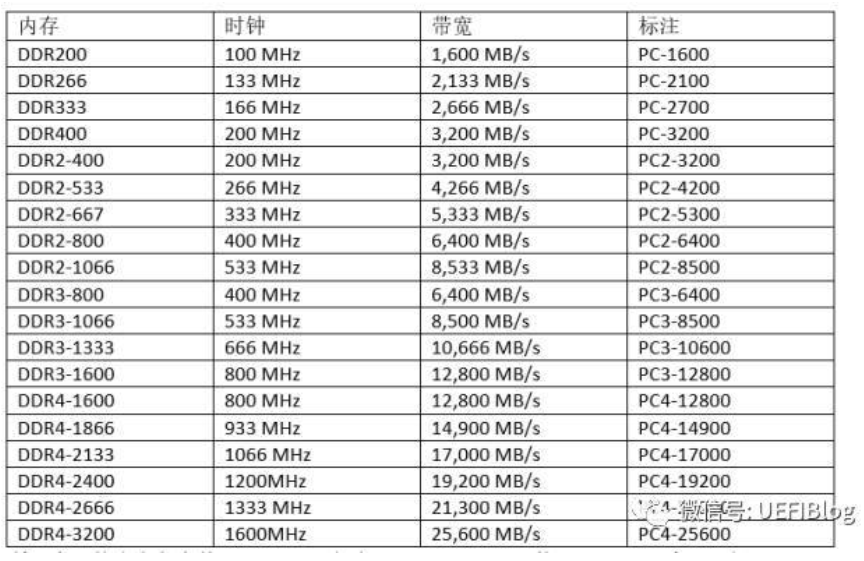

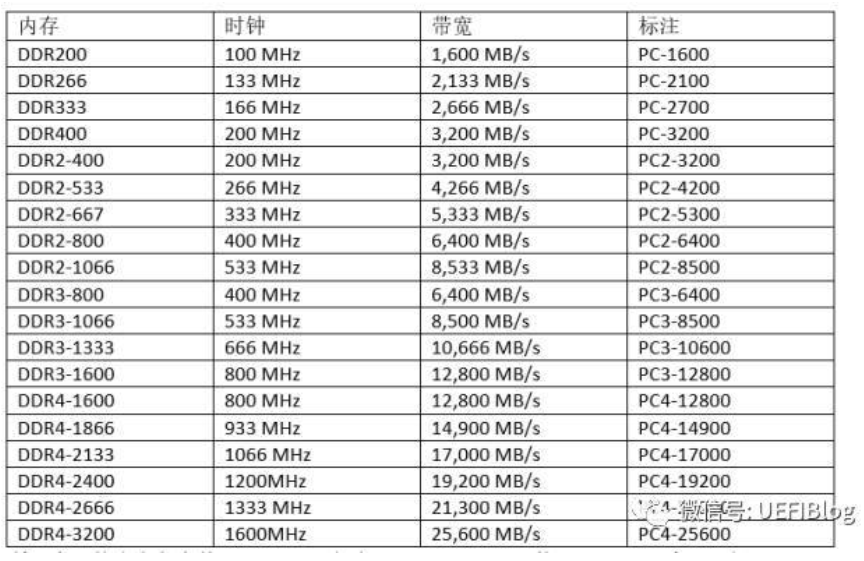

部分台式机DIMM厂商都会标注DDRx-yyy,x代表第几代,yyy代表数据传输率。而大部分的SO-DIMM和RDIMM等则标注PCx-zzzz,x还代表第几代,zzzz则代表最大带宽。因为DDR位宽为64位,8个字节,所以zzzz=yyy * 8,而yyy又是时钟的两倍。下面这张表是主要的各代DDR内存的速度:

-

9-10-F2 ---表示批次。前面09-10是产品设计日期为2009年10月

- 1134---代表出厂日期,指的是2011年第34周出厂的

参考:

https://www.cnblogs.com/tcicy/p/10087392.html

https://baike.baidu.com/item/%E5%86%85%E5%AD%98%E6%9D%A1/108389?fr=aladdin