一、如何访问

常见的如SDRAM、NOR、网卡等都是这样的接口。它们既有数据线也有地址线,并且地址线和数据线共用。这样的话地址线和数据线接有众多设备,正是因为每一个设备都有单独的片选引脚,访问它之前先设置片选引脚为低电平,从而保证其他片选引脚为高电平,才能只访问一个而不影响其他。

访问某个地址时,CPU发出地址信号给内存控制器,内存控制器根据该地址决定让哪一个片选引脚输出低电平,只要所发出的地址信号在想访问设备的地址范围(具体要看地址映射图中所分配的地址范围了)之内就可以访问到。

二、实例

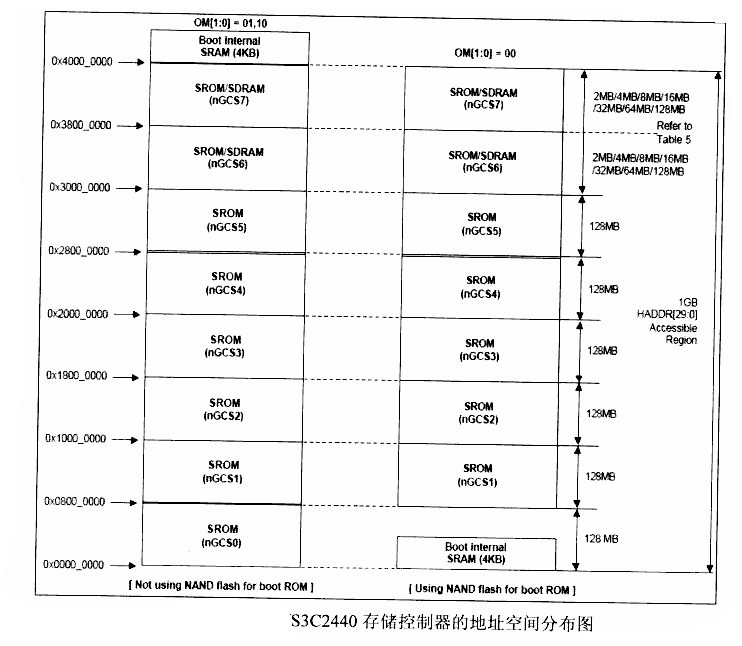

上述中每一个片选引脚所对应的地址空间称为一个BANK,不同的BANK大小在不同的SoC中是不同的。例如对于早期的S3C2440对外引出的27根地址线ADDRO~ADDR26的访问空间是I28MB(这里说的128M指的只是1BANK大小),CPU对外还引出了8片选信号nGCSO~nGCS7,对应于BANK0~BANK7,当访问BANKx的地址空间时,nGCSx引脚输出低电平用来选中外接的设备。这样,每个nGCSx对应128MB地址空间,8个nGCSx信号总共就对 应了1GB的地址空间。这8个BANK的地址空间如下图所示。其中左边对应不使用NANDFlash作为启动设备(单板上不接NAND_BOOT跳线)时的地址空间布局,右边对应使用NANDFlash作为启动设各(单板上接NAND_BOOT 跳线)时的地址空间布局。

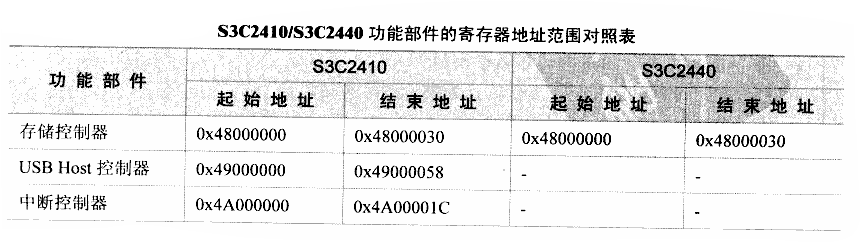

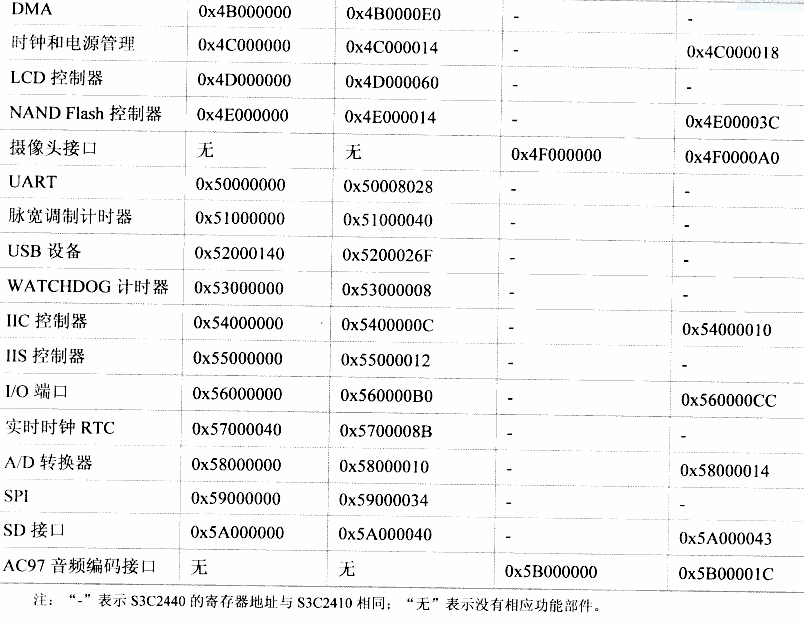

然而S3C2440作为32位的CPU(前27位作为地址线供外设使用。多外引出多少条地址线由内存控制器决定),可以使用的地址范围理论上达到4GB.除去上述用于连接外设的1GB外,还有一部分是CPU内部寄存器的地址,剩下的地址空间没有使用。S3C2440的寄存器地址范范围都处于0x4800000~0x5FFFFFFF,各功能部件的寄 存器大体相同,如下表所示。

三、那么对于不同位宽的外设,接线方式又是如何的呢?

我们可以看到很多开发板原理图上地址线接到16位的NOR flash时,地址线是从ADDR1开始的,ADDR0没有用,这是什么原因呢?因为CPU认为一个地址对应一个人字节;而NOR flash则认为一个地址对应二个字节(它的每一个地址单元为2个字节);因此假如CPU想访问地址3,那么对于NOR flash来说,是访问它的第1个地址单元。那么之间的这个矛盾怎么协调的呢?对于地址3,即00000011,只需要将00000011的从第二位开始接到NOR flash就可以了(把最低的那位空出来)。同理若CPU想访问地址2(000010),同样也可以访问到正确的NOR flash地址。这样保证接线正确后,读出这个16位的数据后供内存控制器会把他们分离出来给CPU。

四、内存控制器的设置