怎样添加ALTERA的元件库。今天总算可以了。

set LIBPATH D:/altera/90/quartus/eda/sim_lib

vlib sim_lib

vmap sim_lib sim_lib

#vlog -work sim_lib $LIBPATH/altera_mf.v

#vlog -work sim_lib $LIBPATH/altera_primitives.v

#vlog -work sim_lib $LIBPATH/sgate.v

#vlog -work sim_lib $LIBPATH/arriaii_atoms.v

#vlog -work sim_lib $LIBPATH/arriaii_hssi_atoms.v

#vlog -work sim_lib $LIBPATH/220model.v

#####################################################

# 建立一个工作库,

vlib work

vmap work work

# vlog是对verilog文件的编译

vlog E:/modelsim/test3/src/SRAM_TOP.v

vlog E:/modelsim/test3/Testbench/SRAM_TOP_tb.v

此步骤对应于Compile -> Compile All

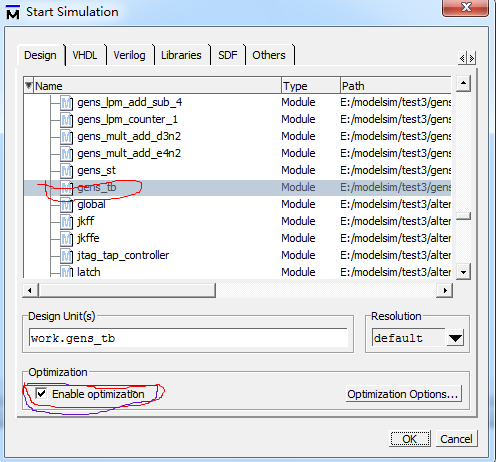

#vsim命令是开始仿真, -novopt表示不优化

vsim -novopt work.SRAM_TOP_tb

#此步骤对于于Start Simulation中在work库中选择脚本文件和把勾选的Enable Optimization去掉

#添加信号波形,也可以分别添加每一个信号,信号添加的次序是就wave窗口显示的次序,同时可以直接设置信号的类型是10进制,还

是无符号等。

add wave -dec /I_SRAM_TOP/*

add wave -noupdate -radix decimal /gens_tb/i_gens/fsin_o

#看到在这里我们添加的是testbench文件gens_tb中例化的i_gens文件中的fsin_o信号,并把它设置为10进制。

add wave -noupdate -radix decimal /gens_tb/i_gens/fcos_o

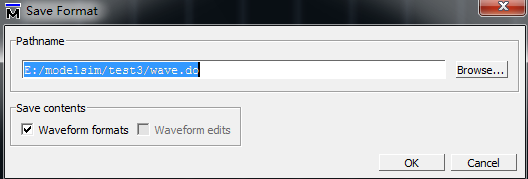

在wave波形窗口中点击保存会生成wave.do文件,里面会有在wave窗口中的设置命令。

run 200000 ns

在这里还有一个问题需要验证:在仿真IP时一般要添加库,如果库仿真好了,在编译时可以直接添加,那用tcl应怎样表示呢?

http://www.cnblogs.com/LJWJL/archive/2013/01/14/Simulation.html

关于几个交互的使用

if [ file exists work ] {

vdel -all

}

/*********************************************************************************/

1、设置路径

cd命令用于更改modelsim的路径,如果仿真正在执行cd命令无效;如果找开了一个工程,那cd命令会关闭当前的工程

语法:cd <dir>

eg:cd e:/fpga

/*********************************************************************************/

2、alias 显示和建立用户定义的别名,有点相当于c语言中的“宏定义”

Syntax

alias [<name> ["<cmds>"]]

当cmds为多组命令时用”;“分开,并且用双引号

eg: alias ld "dev_com;com;elab"

eg2:

alias dev_com {

if [ string match "*ModelSim*" [ vsim -version ] ] {

vlog "$QUARTUS_INSTALL_DIR/eda/sim_lib/altera_primitives.v" -work altera_ver

vlog "$QUARTUS_INSTALL_DIR/eda/sim_lib/220model.v" -work lpm_ver

vlog "$QUARTUS_INSTALL_DIR/eda/sim_lib/sgate.v" -work sgate_ver

vlog "$QUARTUS_INSTALL_DIR/eda/sim_lib/altera_mf.v" -work altera_mf_ver

vlog -sv "$QUARTUS_INSTALL_DIR/eda/sim_lib/mentor/altera_lnsim_for_vhdl.sv" -work altera_lnsim_ver

vlog "$QUARTUS_INSTALL_DIR/eda/sim_lib/mentor/cyclonev_atoms_ncrypt.v" -work cyclonev_ver

vlog "$QUARTUS_INSTALL_DIR/eda/sim_lib/mentor/cyclonev_hmi_atoms_ncrypt.v" -work cyclonev_ver

vlog "$QUARTUS_INSTALL_DIR/eda/sim_lib/mentor/cyclonev_atoms_for_vhdl.v" -work cyclonev_ver

vlog "$QUARTUS_INSTALL_DIR/eda/sim_lib/mentor/cyclonev_hssi_atoms_ncrypt.v" -work cyclonev_hssi_ver

vlog "$QUARTUS_INSTALL_DIR/eda/sim_lib/mentor/cyclonev_hssi_atoms_for_vhdl.v" -work cyclonev_hssi_ver

vlog "$QUARTUS_INSTALL_DIR/eda/sim_lib/mentor/cyclonev_pcie_hip_atoms_ncrypt.v" -work cyclonev_pcie_hip_ver

vlog "$QUARTUS_INSTALL_DIR/eda/sim_lib/mentor/cyclonev_pcie_hip_atoms_for_vhdl.v" -work cyclonev_pcie_hip_ver

vcom "$QUARTUS_INSTALL_DIR/eda/sim_lib/altera_syn_attributes.vhd" -work altera

vcom "$QUARTUS_INSTALL_DIR/eda/sim_lib/altera_standard_functions.vhd" -work altera

vcom "$QUARTUS_INSTALL_DIR/eda/sim_lib/alt_dspbuilder_package.vhd" -work altera

vcom "$QUARTUS_INSTALL_DIR/eda/sim_lib/altera_europa_support_lib.vhd" -work altera

vcom "$QUARTUS_INSTALL_DIR/eda/sim_lib/altera_primitives_components.vhd" -work altera

vcom "$QUARTUS_INSTALL_DIR/eda/sim_lib/altera_primitives.vhd" -work altera

vcom "$QUARTUS_INSTALL_DIR/eda/sim_lib/220pack.vhd" -work lpm

vcom "$QUARTUS_INSTALL_DIR/eda/sim_lib/220model.vhd" -work lpm

vcom "$QUARTUS_INSTALL_DIR/eda/sim_lib/sgate_pack.vhd" -work sgate

vcom "$QUARTUS_INSTALL_DIR/eda/sim_lib/sgate.vhd" -work sgate

vcom "$QUARTUS_INSTALL_DIR/eda/sim_lib/altera_mf_components.vhd" -work altera_mf

vcom "$QUARTUS_INSTALL_DIR/eda/sim_lib/altera_mf.vhd" -work altera_mf

vcom "$QUARTUS_INSTALL_DIR/eda/sim_lib/altera_lnsim_components.vhd" -work altera_lnsim

vcom "$QUARTUS_INSTALL_DIR/eda/sim_lib/cyclonev_atoms.vhd" -work cyclonev

vcom "$QUARTUS_INSTALL_DIR/eda/sim_lib/cyclonev_components.vhd" -work cyclonev

}

}

这样的话,在modelsim的命令窗输入dev_com,就会执行所有的编译文件命令。

/*********************************************************************************/

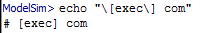

echo 在脚本框中输出指定的内容

Syntax

echo [<text_string>]

如上图,在modelsim的命令行中输入ech "\exec\] com" 就会输出 #[exec] com,其实就相关于matlab 中的output命令

/*********************************************************************************/

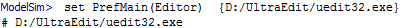

eidt

上面的命令用于设置modelsim的文件编辑器

Syntax

edit [<filename>]

[<filename>]用于指定要编辑文件的名字

/********************************************************************************/

proc ensure_lib { lib } { if ![file isdirectory $lib] { vlib $lib } }

个人理解:如果路径中不存在库,就指定ensure_lib用于建立库

vlib可以用于建立一个文件夹