3.2 主存储器

四、只读存储器(ROM)————>了解(考试也可能会考)

- 掩膜ROM(MROM)

- 行列选择线交叉处有 MOS 管为“1”

- 行列选择线交叉处无 MOS 管为“0”

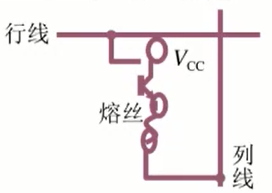

- PROM(一次性编程)

- 熔丝断为 0

- 熔丝未断为 1

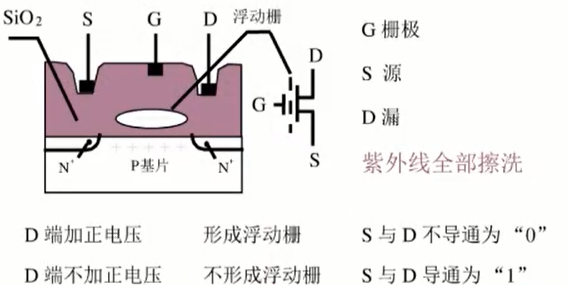

- EPROM(多次编程)

(1)N 型沟道浮动栅 MOS 电路

- EEPROM(多次性编程)

电可擦写、局部擦写、全部擦写

- Flash Memory(闪存型存储器)

就是SSD(固态硬盘),U盘之类的

| EPROM | 价格便宜,集成度高 |

|---|---|

| EEPROM | 电可擦洗重写 |

优点:比EEPROM 快,具有 RAM 功能

缺点:(1)一位的写的次数有限制;(2)当SSD挂了里面的数据没办法备份

五、存储器与CPU的连接(自主命题考画图的频率相当高)

1. 存储容量的扩展

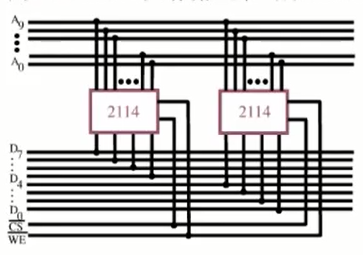

(1)位扩展(增加存储字长)——>增加床位

小例子:用多少片 1k × 4位存储芯片组成 1k × 8位的存储器

分析:1k = 210 (有10根地址线),8bit = 8根数据线

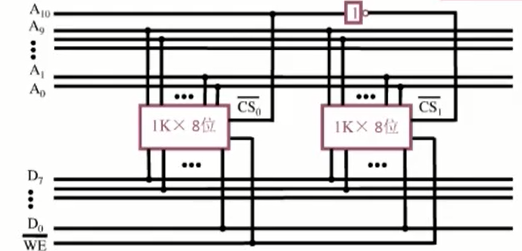

(2)字扩展(增加存储字的数量)——>增加房间数,去盖楼

小例子:用多少片 1k × 8位存储芯片组成 2k × 8位的存储器

分析:需要让A10地址线作为片选线

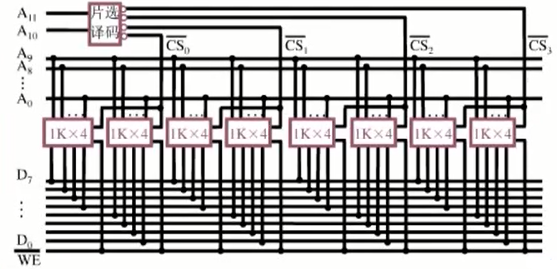

(3)字、位扩展

小例子:用多少片 1k × 4位 存储芯片组成 4k × 8位 的存储器

分析:其中的片选译码器用2-4译码器就可以。

2. 存储器与CPU连接

- 地址线的连接

- 数据线的连接

- 读/写命令线的连接

- 片选线的连接

- 合理选择存储芯片

- 其他:时序、负载

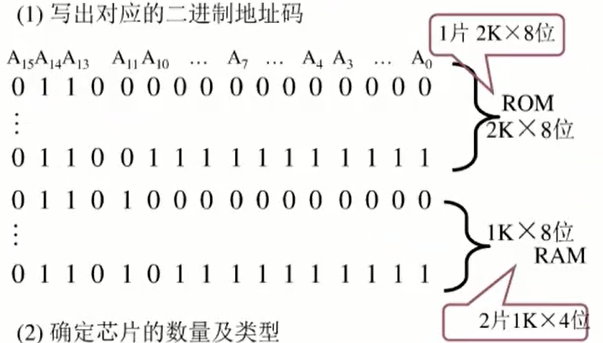

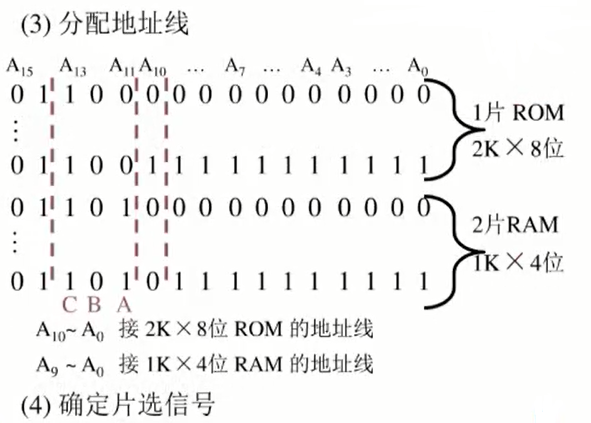

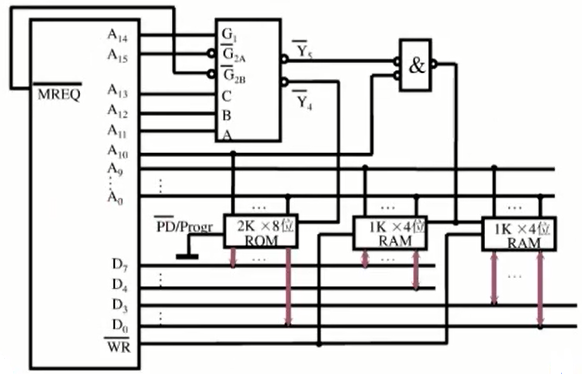

3. 试题

假设CPU有16跟地址引脚,8根数据引脚,并用MREQ作为访存控制信号(低电平有效),用WR作读/写控制信号(低电平为写,高电平为读)。现有下列存储芯片: 1k × 4位RAM、4k × 8位RAM、8k × 8位RAM、2k × 8位ROM、4k × 8位ROM、8k × 8位ROM,另外有74138译码器和各种门电路,满足以下

(1)主存地址空间分配:6000H ~ 67FFH 为系统程序区、6800H ~ 6BFFH 为用户程序区

(2)合理选用上述存储芯片,说明各选几片

(3)详细画出芯片片选逻辑

解析:系统程序区:ROM;用户程序区:RAM

下图为截图思路及答案