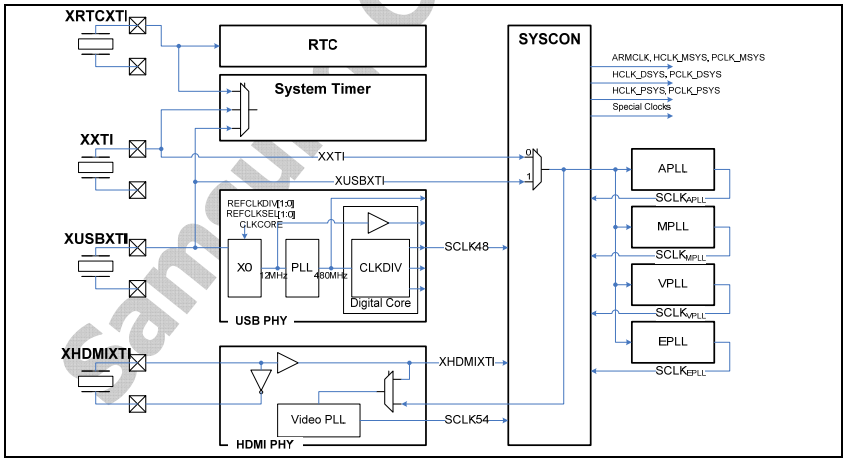

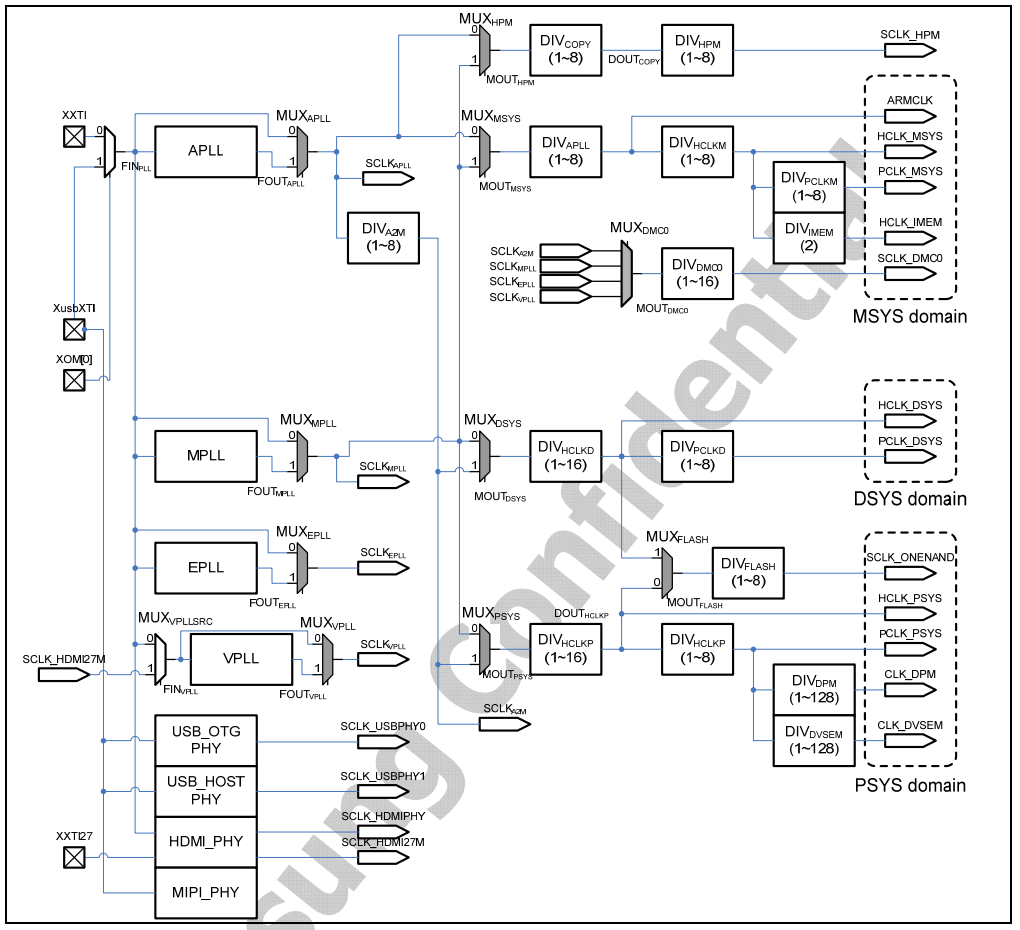

1、S5PV210的时钟获得:外部晶振+内部时钟发生器+内部PLL产生高频时钟+内部分频器分频

S5PV210外部有4个W晶振接口,可以根据需要来决定在哪里接晶振。接了晶振之后上电相应的模块就能产生振荡,产生原始时钟。原始时钟经过一系列的筛选开关进入相应的PLL电路生成倍频后的高频时钟。高频时钟再经过分频到达芯片内部各模块上。(有些模块,譬如串口内部还有进一步的分频器进行再次分频使用)

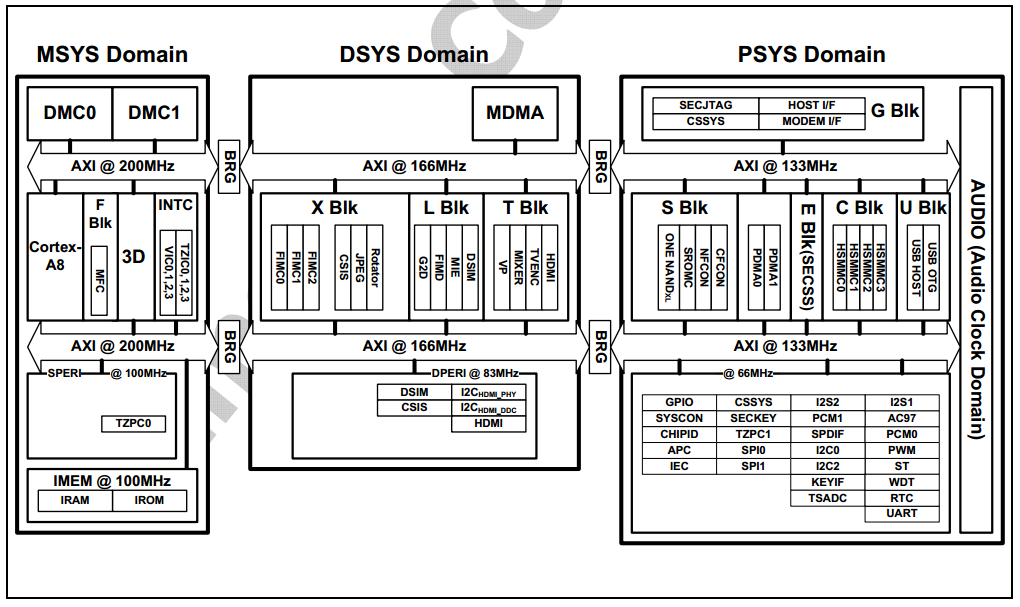

2、时钟域:MSYS、DSYS、PSYS

MSYS(main system):CPU(Cortex-A8内核)、DRAM控制器(DMC0和DMC1)、SRAM(IRAM&IROM)、INTC、SPERI(configuration inerface)······

ARMCLK: 给cpu内核工作的时钟,也就是所谓的主频。

HCLK_MSYS: MSYS域的高频时钟,给DMC0和DMC1使用

PCLK_MSYS: MSYS域的低频时钟

HCLK_IMEM:给iROM和iRAM(合称iMEM)使用

DSYS(display system): 都是和视频显示、编解码等有关的模块(FIMC、FIMD、JPEG)

HCLK_DSYS:DSYS域的高频时钟

PCLK_DSYS:DSYS域的低频时钟

PSYS(peripheral system): 和内部的各种外设时钟有关,譬如串口、SD接口、I2C、AC97、USB等

HCLK_PSYS:PSYS域的高频时钟

PCLK_PSYS:PSYS域的低频时钟

3、关于PLL(包括APLL MPLL EPLL VPLL)

APLL:Cortex-A8内核 MSYS域

MPLL&EPLL:DSYS PSYS

VPLL:Video视频相关模块

4、时钟设置的关键寄存器

xPLL_LOCK 控制PLL锁定周期

xPLL_CON 打开/关闭PLL电路,设置PLL的倍频参数,查看PLL锁定状态

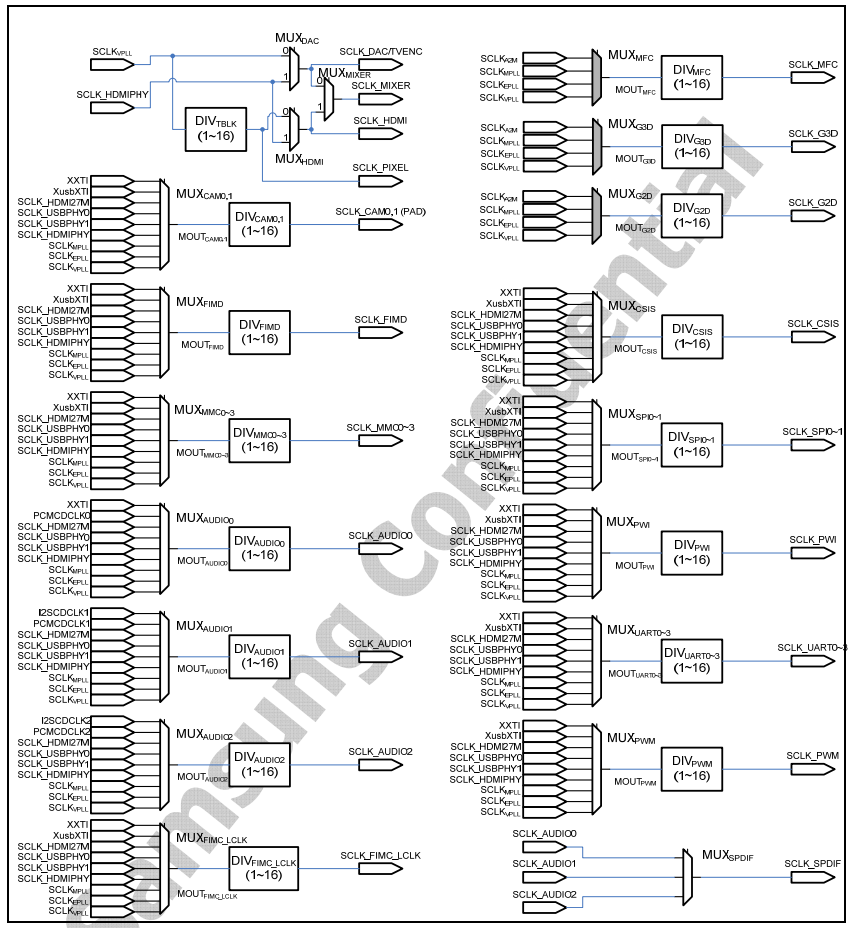

CLK_SRCn(n:0~6) 设置时钟来源,对应时钟框图中的MUX开关

CLK_SRC_MASK 决定MUX开关n选1后是否能继续通过

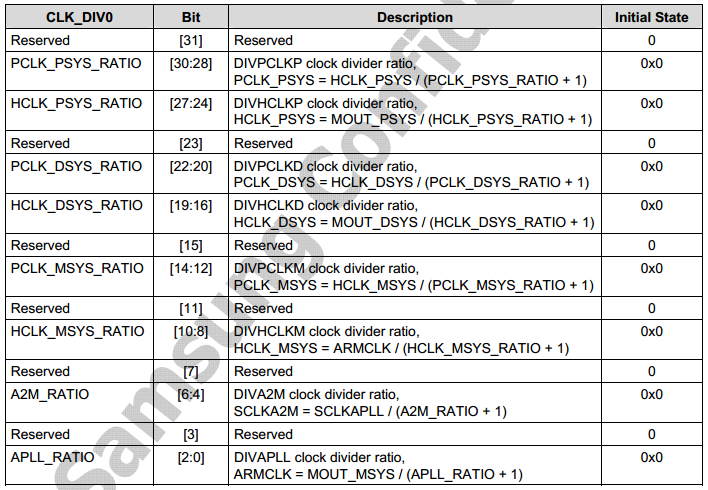

CLK_DIV 各模块的分频器参数配置

CLK_GATE_x 类似于CLK_SRC_MASK,对时钟进行开关控制

CLK_DIV_STATn、CLK_MUX_STATn 查看DIV和MUX的状态(已经完成还是在进行中)

5、代码设置时钟逻辑步骤:

(1)先选择不使用PLL。让外部24MHz原始时钟直接过去,绕过APLL那条路

1 ldr r0, =ELFIN_CLOCK_POWER_BASE 2 //设置各种时钟开关,暂时不使用PLL 3 ldr r1, =0x0 4 //CLK_SRC bit[0]就是APLL_SEL,(APLL_SEL:control MUXAPLL(0:FINPLL,1:FOUTAPLL)) 5 str r1, [r0, #CLK_SRC0_OFFSET]

(2)设置锁定时间。默认值为0x0FFF,保险起见我们设置为0xFFFF

//设置锁定时间,使用默认值即可 // 设置PLL后,时钟从Fin提升到目标频率时,需要一定的时间,即锁定时间 ldr r1, =0x0000FFFF str r1, [r0, #APLL_LOCK_OFFSET] str r1, [r0, #MPLL_LOCK_OFFSET]

(3)设置分频系统,由PLL出来的最高时钟如何分频得到各个分时钟

1 //设置分频 2 // 清bit[0~31] 3 ldr r1, [r0, #CLK_DIV0_OFFSET] 4 ldr r2, =CLK_DIV0_MASK 5 bic r1, r1, r2 6 ldr r2, =0x14131440 7 orr r1, r1, r2 8 str r1, [r0, #CLK_DIV0_OFFSET]

0x14131440的含义:

PCLK_PSYS = HCLK_PSYS / 2

HCLK_PSYS = MOUT_PSYS / 5

PCLK_DSYS = HCLK_DSYS / 2

HCLK_DSYS = MOUT_DSYS / 4

·······

HCLK_MSYS = ARMCLK / 5

ARMCLK = MOUT_MSYS / 1

(4)设置PLL,主要是设置PLL的倍频系统,决定由输入端24MHz的原始频率可以得到多大的输出频率。我们按照默认设置值设置输出为ARMCLK为1GHz

1 #define set_pll(mdiv, pdiv, sdiv) (1<<31 | mdiv<<16 | pdiv<<8 | sdiv) 2 #define APLL_VAL set_pll(APLL_MDIV,APLL_PDIV,APLL_SDIV) 3 #define MPLL_VAL set_pll(MPLL_MDIV,MPLL_PDIV,MPLL_SDIV) 4 5 //设置PLL 6 // FOUT = MDIV*FIN/(PDIV*2^(SDIV-1))=0x7d*24/(0x3*2^(1-1))=1000 MHz 7 ldr r1, =APLL_VAL 8 str r1, [r0, #APLL_CON0_OFFSET] 9 // FOUT = MDIV*FIN/(PDIV*2^SDIV)=0x29b*24/(0xc*2^1)= 667 MHz 10 ldr r1, =MPLL_VAL 11 str r1, [r0, #MPLL_CON_OFFSET]

(5)打开PLL。前面4步已经设置好了所有的开关和分频系数,该步骤打开PLL后PLL开始工作,锁定频率后输出,然后经过分频得到各个频率。

1 //设置各种时钟开关,使用PLL 2 ldr r1, [r0, #CLK_SRC0_OFFSET] 3 ldr r2, =0x10001111 4 orr r1, r1, r2 5 str r1, [r0, #CLK_SRC0_OFFSET]

6、汇编代码

1 // 时钟控制器基地址 2 #define ELFIN_CLOCK_POWER_BASE 0xE0100000 3 4 // 时钟相关的寄存器相对时钟控制器基地址的偏移值 5 #define APLL_LOCK_OFFSET 0x00 6 #define MPLL_LOCK_OFFSET 0x08 7 8 #define APLL_CON0_OFFSET 0x100 9 #define APLL_CON1_OFFSET 0x104 10 #define MPLL_CON_OFFSET 0x108 11 12 #define CLK_SRC0_OFFSET 0x200 13 #define CLK_SRC1_OFFSET 0x204 14 #define CLK_SRC2_OFFSET 0x208 15 #define CLK_SRC3_OFFSET 0x20c 16 #define CLK_SRC4_OFFSET 0x210 17 #define CLK_SRC5_OFFSET 0x214 18 #define CLK_SRC6_OFFSET 0x218 19 #define CLK_SRC_MASK0_OFFSET 0x280 20 #define CLK_SRC_MASK1_OFFSET 0x284 21 22 #define CLK_DIV0_OFFSET 0x300 23 #define CLK_DIV1_OFFSET 0x304 24 #define CLK_DIV2_OFFSET 0x308 25 #define CLK_DIV3_OFFSET 0x30c 26 #define CLK_DIV4_OFFSET 0x310 27 #define CLK_DIV5_OFFSET 0x314 28 #define CLK_DIV6_OFFSET 0x318 29 #define CLK_DIV7_OFFSET 0x31c 30 31 #define CLK_DIV0_MASK 0x7fffffff 32 33 // M、P、S的配置值都是查数据手册中典型时钟配置值的推荐配置得来的。 34 #define APLL_MDIV 0x7d // 125 35 #define APLL_PDIV 0x3 36 #define APLL_SDIV 0x1 37 38 #define MPLL_MDIV 0x29b // 667 39 #define MPLL_PDIV 0xc 40 #define MPLL_SDIV 0x1 41 42 #define set_pll(mdiv, pdiv, sdiv) (1<<31 | mdiv<<16 | pdiv<<8 | sdiv) 43 #define APLL_VAL set_pll(APLL_MDIV,APLL_PDIV,APLL_SDIV) 44 #define MPLL_VAL set_pll(MPLL_MDIV,MPLL_PDIV,MPLL_SDIV) 45 46 .global clock_init 47 clock_init: 48 ldr r0, =ELFIN_CLOCK_POWER_BASE 49 50 // 1 设置各种时钟开关,暂时不使用PLL 51 ldr r1, =0x0 52 //CLK_SRC bit[0]就是APLL_SEL,(APLL_SEL:control MUXAPLL(0:FINPLL,1:FOUTAPLL)) 53 str r1, [r0, #CLK_SRC0_OFFSET] 54 55 // 2 设置锁定时间,使用默认值即可 56 // 设置PLL后,时钟从Fin提升到目标频率时,需要一定的时间,即锁定时间 57 ldr r1, =0x0000FFFF 58 str r1, [r0, #APLL_LOCK_OFFSET] 59 str r1, [r0, #MPLL_LOCK_OFFSET] 60 61 // 3 设置分频 62 // 清bit[0~31] 63 ldr r1, [r0, #CLK_DIV0_OFFSET] 64 ldr r2, =CLK_DIV0_MASK 65 bic r1, r1, r2 66 ldr r2, =0x14131440 67 orr r1, r1, r2 68 str r1, [r0, #CLK_DIV0_OFFSET] 69 70 // 4 设置PLL 71 // FOUT = MDIV*FIN/(PDIV*2^(SDIV-1))=0x7d*24/(0x3*2^(1-1))=1000 MHz 72 ldr r1, =APLL_VAL 73 str r1, [r0, #APLL_CON0_OFFSET] 74 // FOUT = MDIV*FIN/(PDIV*2^SDIV)=0x29b*24/(0xc*2^1)= 667 MHz 75 ldr r1, =MPLL_VAL 76 str r1, [r0, #MPLL_CON_OFFSET] 77 78 // 5 设置各种时钟开关,使用PLL 79 ldr r1, [r0, #CLK_SRC0_OFFSET] 80 ldr r2, =0x10001111 81 orr r1, r1, r2 82 str r1, [r0, #CLK_SRC0_OFFSET] 83 84 mov pc, lr

7、C语言代码

1 // 时钟控制器基地址 2 #define ELFIN_CLOCK_POWER_BASE 0xE0100000 3 4 // 时钟相关的寄存器相对时钟控制器基地址的偏移值 5 #define APLL_LOCK_OFFSET 0x00 6 #define MPLL_LOCK_OFFSET 0x08 7 8 #define APLL_CON0_OFFSET 0x100 9 #define APLL_CON1_OFFSET 0x104 10 #define MPLL_CON_OFFSET 0x108 11 12 #define CLK_SRC0_OFFSET 0x200 13 #define CLK_SRC1_OFFSET 0x204 14 #define CLK_SRC2_OFFSET 0x208 15 #define CLK_SRC3_OFFSET 0x20c 16 #define CLK_SRC4_OFFSET 0x210 17 #define CLK_SRC5_OFFSET 0x214 18 #define CLK_SRC6_OFFSET 0x218 19 #define CLK_SRC_MASK0_OFFSET 0x280 20 #define CLK_SRC_MASK1_OFFSET 0x284 21 22 #define CLK_DIV0_OFFSET 0x300 23 #define CLK_DIV1_OFFSET 0x304 24 #define CLK_DIV2_OFFSET 0x308 25 #define CLK_DIV3_OFFSET 0x30c 26 #define CLK_DIV4_OFFSET 0x310 27 #define CLK_DIV5_OFFSET 0x314 28 #define CLK_DIV6_OFFSET 0x318 29 #define CLK_DIV7_OFFSET 0x31c 30 31 #define CLK_DIV0_MASK 0x7fffffff 32 33 // M、P、S的配置值都是查数据手册中典型时钟配置值的推荐配置得来的。 34 #define APLL_MDIV 0x7d // 125 35 #define APLL_PDIV 0x3 36 #define APLL_SDIV 0x1 37 38 #define MPLL_MDIV 0x29b // 667 39 #define MPLL_PDIV 0xc 40 #define MPLL_SDIV 0x1 41 42 #define set_pll(mdiv, pdiv, sdiv) (1<<31 | mdiv<<16 | pdiv<<8 | sdiv) 43 #define APLL_VAL set_pll(APLL_MDIV,APLL_PDIV,APLL_SDIV) 44 #define MPLL_VAL set_pll(MPLL_MDIV,MPLL_PDIV,MPLL_SDIV) 45 46 47 #define REG_CLK_SRC0 (ELFIN_CLOCK_POWER_BASE + CLK_SRC0_OFFSET) 48 #define REG_APLL_LOCK (ELFIN_CLOCK_POWER_BASE + APLL_LOCK_OFFSET) 49 #define REG_MPLL_LOCK (ELFIN_CLOCK_POWER_BASE + MPLL_LOCK_OFFSET) 50 #define REG_CLK_DIV0 (ELFIN_CLOCK_POWER_BASE + CLK_DIV0_OFFSET) 51 #define REG_APLL_CON0 (ELFIN_CLOCK_POWER_BASE + APLL_CON0_OFFSET) 52 #define REG_MPLL_CON (ELFIN_CLOCK_POWER_BASE + MPLL_CON_OFFSET) 53 54 #define rREG_CLK_SRC0 (*(volatile unsigned int *)REG_CLK_SRC0) 55 #define rREG_APLL_LOCK (*(volatile unsigned int *)REG_APLL_LOCK) 56 #define rREG_MPLL_LOCK (*(volatile unsigned int *)REG_MPLL_LOCK) 57 #define rREG_CLK_DIV0 (*(volatile unsigned int *)REG_CLK_DIV0) 58 #define rREG_APLL_CON0 (*(volatile unsigned int *)REG_APLL_CON0) 59 #define rREG_MPLL_CON (*(volatile unsigned int *)REG_MPLL_CON) 60 61 62 void clock_init(void) 63 { 64 // 1 设置各种时钟开关,暂时不使用PLL 65 rREG_CLK_SRC0 = 0x0; 66 67 // 2 设置锁定时间,使用默认值即可 68 // 设置PLL后,时钟从Fin提升到目标频率时,需要一定的时间,即锁定时间 69 rREG_APLL_LOCK = 0x0000ffff; 70 rREG_MPLL_LOCK = 0x0000ffff; 71 72 // 3 设置分频 73 // 清bit[0~31] 74 rREG_CLK_DIV0 = 0x14131440; 75 76 // 4 设置PLL 77 // FOUT = MDIV*FIN/(PDIV*2^(SDIV-1))=0x7d*24/(0x3*2^(1-1))=1000 MHz 78 rREG_APLL_CON0 = APLL_VAL; 79 // FOUT = MDIV*FIN/(PDIV*2^SDIV)=0x29b*24/(0xc*2^1)= 667 MHz 80 rREG_MPLL_CON = MPLL_VAL; 81 82 // 5 设置各种时钟开关,使用PLL 83 rREG_CLK_SRC0 = 0x10001111; 84 }