如果你不想翻阅资料就关注我吧,我替你安排!

1. 什么时候读取CSEL

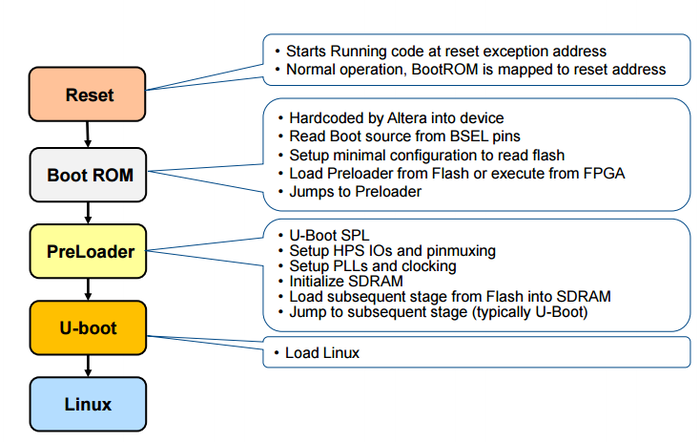

大多数人在设计SoC FPGA板子的SD卡image的时候都是参考的 Intel这个教程https://rocketboards.org/foswiki/Documentation/EmbeddedLinuxBeginnerSGuide ,但在这个Boot Flow里面没有标注什么时候去读取CSEL的值,只提到读取BSEL的值:

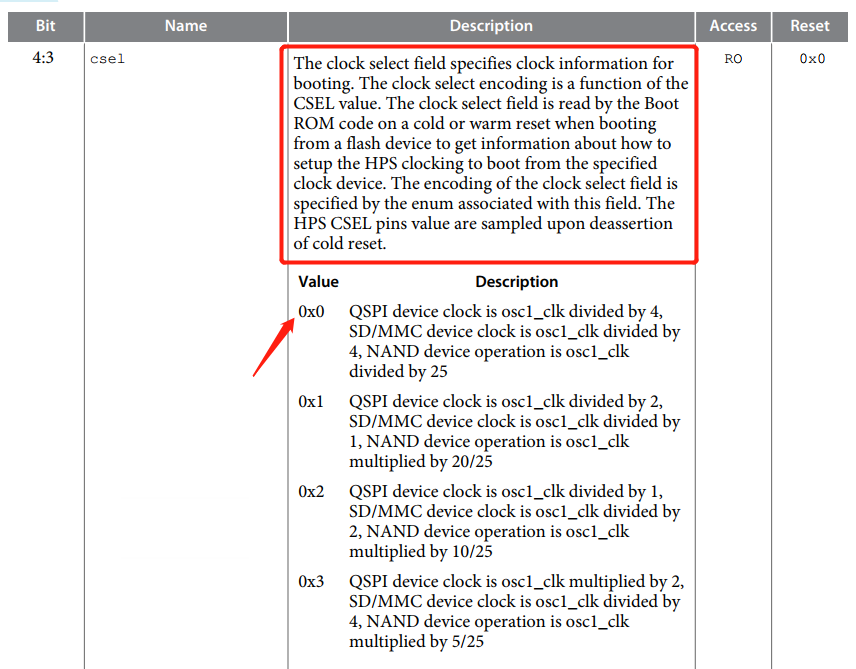

其实在Intel的手册DE0-Nano-SoC_v.1.3.0_HWrevD0_SystemCD\Datasheet\FPGA\cyclone_5_datasheet.pdf里面有提到是Boot ROM code 去读取CSEL的:

那为啥这个Boot Flow里面没有标注读取CSEL?别急,咱接着往下看。

2. CSEL代表什么

让我们先看看CSEL代表什么吧。

继续参考Intel的手册DE0-Nano-SoC_v.1.3.0_HWrevD0_SystemCD\Datasheet\FPGA\cyclone_5_datasheet.pdf我们就知道CSEL代表什么了:

CSEL(时钟选择字段[4:0])指定了boot 时的钟信息。 在冷复位或热复位时,Boot ROM代码读取CSEL,以获取关于如何设置HPS时钟以从指定的时钟设备启动的信息(比如CSEL的值决定了如何去配置main PLL 和 peripheral PLL)。 HPS CSEL引脚值在冷复位时采样 。

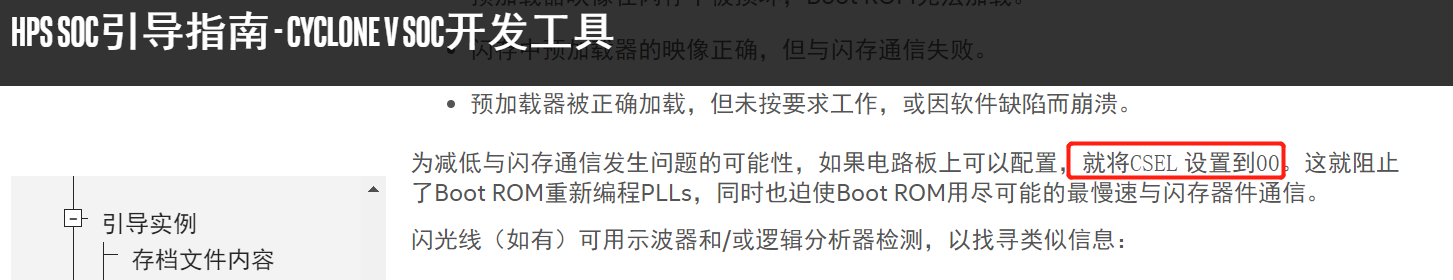

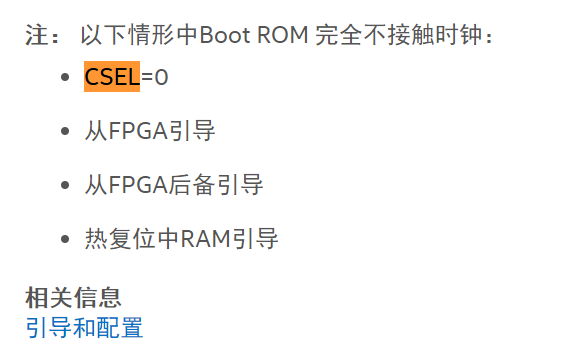

然后我参考了Intel的资料:

https://www.intel.cn/content/www/cn/zh/programmable/documentation/lro1404103165481.html#lro1418623810125

该资料提到如果将CSEL设置为00则可以阻止Boot ROM重新编程PLLs:

3. DE0-Nano-SoC的CSEL设置

那对应到我们手头的DE0-Nano- SoC板子,CSEL 是怎么设置的呢?

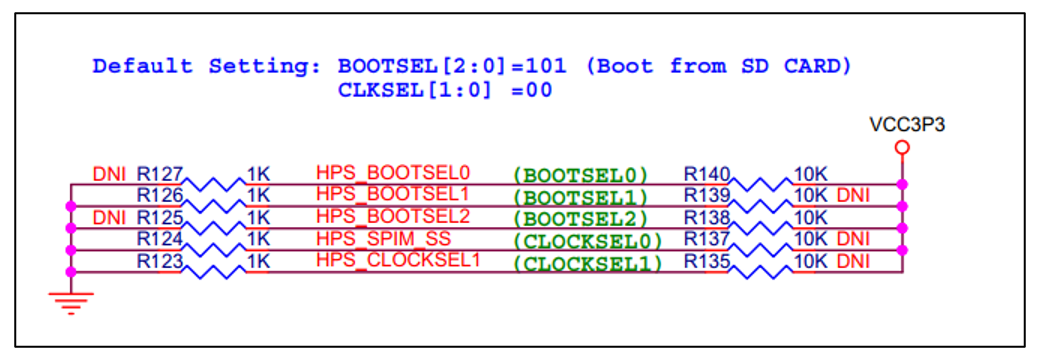

在DE0-Nano- SoC_v.1.3.0_HWrevD0_SystemCD\Schematic\de0-nano-soc.pdf 电路图文档里面可以看到CSEL被硬件编码到00:

到此,我们终于知道为啥这个Boot Flow 里面没有CSEL的原因了:因为设置为00 以后,Boot ROM无需重新编程PLLs。