流水灯想实现的功能:四个led灯依次点亮,形成“流水”的效果。

实现过程:

1、逻辑设计,Verilog编写。

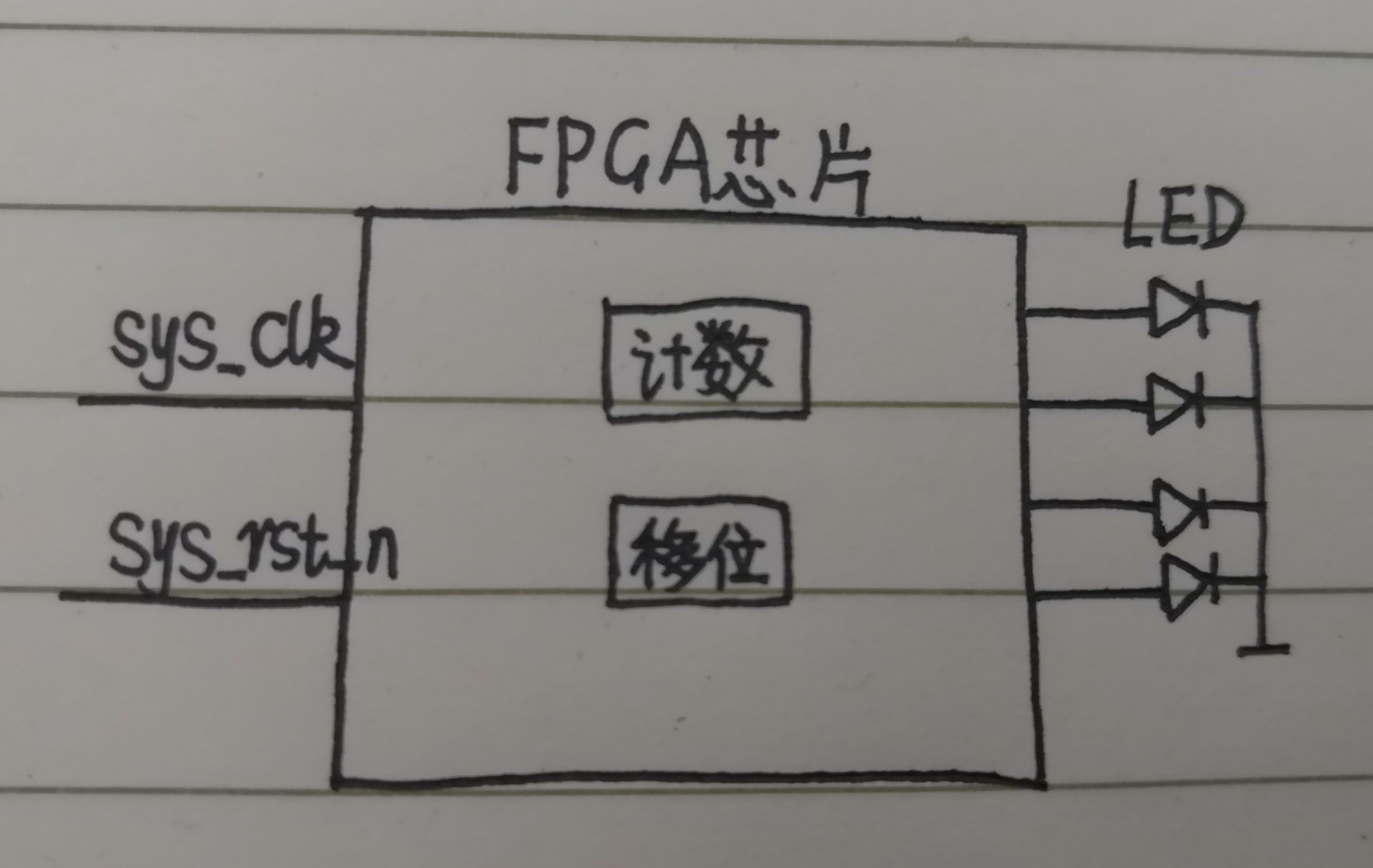

因此要写一个模块flow_led,并在这个模块中实现计数和移位这两个功能。

这个模块input有两个引脚,sys_clk、sys_rst_n;这个模块output有四个引脚,led0、led1、led2、led3。

计数功能:这里需要计数0.2秒。需要芯片时钟的个数counter:

F=50MHz,T=1/F=0.2*10-7s

counter=0.2/0.2*10-7=107=1001 1000 1001 0110 1000 0000

所以定义reg [23:0]counter,107的二进制格式是24位

always @(posedge sys_clk or negedge sys_rst_n) begin

if (!sys_rst_n)

counter <= 24'd0;

else if (counter < 24'd1000_0000)

counter <= counter + 1'b1;

else

counter <= 24'd0;

end

移位功能:计数0.2秒后就移位一次。

always @(posedge sys_clk or negedge sys_rst_n) begin

if (!sys_rst_n)

led <= 4'b0001;

else if(counter == 24'd1000_0000)

led[3:0] <= {led[2:0],led[3]};

else

led <= led;

end

根据原理图,led高电平点亮,所以复位时候可以知道,一直就要一盏灯在亮。

2、确定引脚。

从原理图中可看出,sys_clk接芯片引脚E1;sys_rst_n接芯片引脚M1。Led0、led1、led2、led3依次接芯片引脚D11、C11、E10、F9。

3、编译成功,烧写到开发板,实现功能。

4、仿真。

利用Modelsim软件进行仿真:

①定义时间单位和时间精度

②module 功能_tb;

③定义端口:reg 输入;wire 输出;(这里定义是reg型还是wire型与输入、输出无关)

④初始化输入:initial begin

………..

………..

end

⑤代码例化:

功能 u_功能(

…………………

);

⑥endmodule

我这里在开发板上为了肉眼看到灯的切换,所以时间为每隔0.2秒才发生变化。但是这个时间在仿真时太长了,因此调整为0.2*10-6秒,这样方便在仿真的时候能看出led灯的变化。

那么修改之后就是每十个时钟,led就会移位一次。

经上述说,在开发板和modelsim都实现具体的效果,流水灯实战结束。