写分频就是写计数器。

二分频:指把频率分成两部分。比如50MHz的频率,二分频后就是25MHz。由公式T=1/f可知,时钟变为原来的两倍。

综合代码如下:

module shizhan(

input sys_clk,

input sys_rst_n,

output reg dri_clk

);

always @(posedge sys_clk or negedge sys_rst_n)begin

if(!sys_rst_n)

dri_clk<=1'b0;

else

dri_clk<=~dri_clk;

end

endmodule

tb代码如下:

`timescale 1ns/1ns

module shizhan_tb;

reg sys_clk;

reg sys_rst_n;

wire dri_clk;

initial begin

sys_clk<=1'b0;

sys_rst_n<=1'b0;

#10 sys_rst_n<=1'b1;

end

always #10 sys_clk<=~sys_clk;

shizhan u_shizhan(

.sys_clk (sys_clk),

.sys_rst_n (sys_rst_n),

.dri_clk (dri_clk)

);

endmodule

实战结果如下:

三分频

综合代码如下:

module clk(

input sys_clk,

input sys_rst_n,

output dri_clk

);

reg [2:0]cnt;

reg dri_clk1;

reg dri_clk2;

always @(posedge sys_clk or negedge sys_rst_n)begin

if(!sys_rst_n)

cnt<=3'b0;

else if(cnt<2)

cnt<=cnt+1;

else

cnt<=3'b0;

end

always @(posedge sys_clk or negedge sys_rst_n)begin

if(!sys_rst_n)begin

dri_clk1<=1'b0;

end

else if(cnt==0)begin

dri_clk1<=~dri_clk1;

end

else if(cnt==1)begin

dri_clk1<=~dri_clk1;

end

else

dri_clk1<=dri_clk1;

end

always @(negedge sys_clk or negedge sys_rst_n)begin

if(!sys_rst_n)

dri_clk2<=1'b0;

else

dri_clk2<=dri_clk1;

end

assign dri_clk=dri_clk1|dri_clk2;

endmodule

tb仿真代码如下:(ps:这个仿真程序跟二分频一样的,就是名字改成了clk_tb)

`timescale 1ns/1ns

module clk_tb;

reg sys_clk;

reg sys_rst_n;

wire dri_clk;

initial begin

sys_clk<=1'b0;

sys_rst_n<=1'b0;

#10 sys_rst_n<=1'b1;

end

always #10 sys_clk<=~sys_clk;

clk u_clk(

.sys_clk (sys_clk),

.sys_rst_n (sys_rst_n),

.dri_clk (dri_clk)

);

endmodule

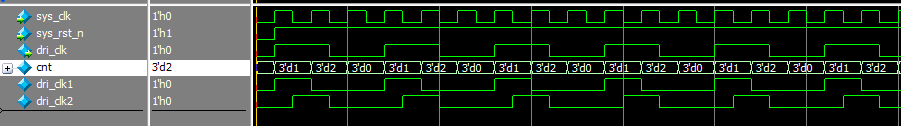

实战结果:

同理,五分频实现如下:

综合代码如下:

module clk(

input sys_clk,

input sys_rst_n,

output dri_clk

);

reg [2:0]cnt;

reg dri_clk1;

reg dri_clk2;

always @(posedge sys_clk or negedge sys_rst_n)begin

if(!sys_rst_n)

cnt<=3'b0;

else if(cnt<4)

cnt<=cnt+1;

else

cnt<=3'b0;

end

always @(posedge sys_clk or negedge sys_rst_n)begin

if(!sys_rst_n)begin

dri_clk1<=1'b0;

end

else if(cnt==2)begin

dri_clk1<=~dri_clk1;

end

else if(cnt==4)begin

dri_clk1<=~dri_clk1;

end

else

dri_clk1<=dri_clk1;

end

always @(negedge sys_clk or negedge sys_rst_n)begin

if(!sys_rst_n)

dri_clk2<=1'b0;

else

dri_clk2<=dri_clk1;

end

assign dri_clk=dri_clk1|dri_clk2;

endmodule

仿真代码同三分频一样。

实验结果: