- 分得到析四个状态:

S1: 主干道(绿灯亮) ,支干道(亮红灯);--40S

S1: 主干道 (黄灯亮) ,支干道(亮红灯);--4S

S1: 主干道 (亮红灯),支干道(绿灯亮);--20S

S1: 主干道 (亮红灯),支干道(黄灯亮);--4S

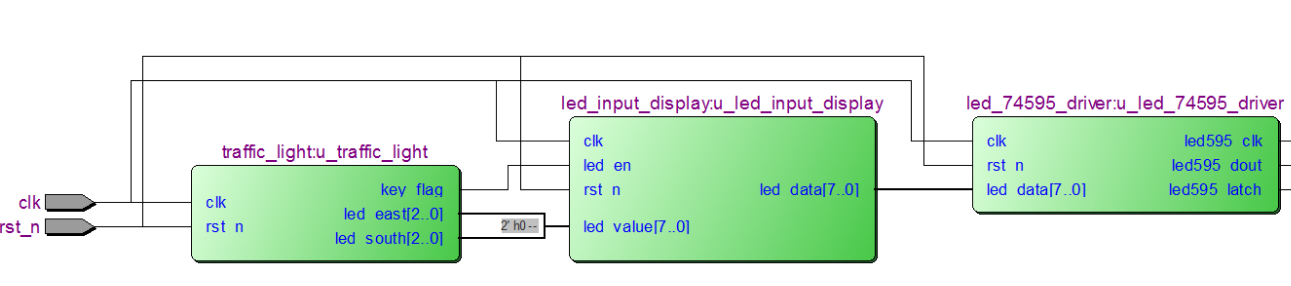

代码:包括四部分:traffic_ligh_top(顶层例化)、traffic_light(交通灯控制部分)、led_input_display(把(交通灯控制部分的)数据打一拍(再送给74595))、led_74595_driver(串转并-进行显示)

仿真:代码及波形显示

- 代码编写

//---------------------------------------------------------------------------------------

- RTL Viewer

- traffic_ligh_top(顶层例化)

1 /*----------------------------------------------------------------------- 2 Author : WHaoL 3 Technology blogs : http://www.cnblogs.com/luckySuperman/ 4 : http://blog.chinaaet.com/eWorld 5 Email Address : liangwenhao0603@163.com 6 Filename : traffic_ligh_top.v 7 Data : 2016-09-26 8 Description : 9 modification history : 10 Data By Version Change Description 11 ========================================================================= 12 16/9/26 WHaoL 1.0 Original 13 =======================================================================*/ 14 `timescale 1ns/1ns 15 module traffic_ligh_top 16 ( 17 input clk, 18 input rst_n, 19 20 //matrix keyboard interface 21 22 23 output led595_clk, 24 output led595_dout, 25 output led595_latch 26 ); 27 28 29 wire [2:0] led_east; 30 wire [2:0] led_south; 31 32 wire key_flag; 33 //------------------------------------- 34 traffic_light u_traffic_light 35 ( 36 .clk(clk), //时钟 50MHz 37 .rst_n(rst_n), //复位 低电平有效 38 39 // south north east west 40 //.e_light(e_light), // 东方向 指示灯 41 //w_light, //西方向 指示灯 42 43 //.s_light(s_light), //南方向 指示灯 44 //n_light, //北方向 指示灯 45 .led_east(led_east), 46 //.led_wast(led_wast), 47 48 .led_south(led_south), 49 //.led_nouth(led_nouth) 50 .key_flag(key_flag) 51 ); 52 53 //--------------------------------- 54 //led data input with enable signal. 55 wire [7:0] led_data; 56 led_input_display 57 #( 58 .LED_WIDTH (8) 59 ) 60 u_led_input_display 61 ( 62 //global 63 .clk (clk), 64 .rst_n (rst_n), 65 66 //user interface 67 .led_en (key_flag), 68 .led_value ({led_east[2:0],2'b00,led_south[2:0]}), 69 70 //led interface 71 .led_data (led_data) 72 ); 73 74 //------------------------------------------- 75 led_74595_driver u_led_74595_driver 76 ( 77 //global clock 78 .clk (clk),//50MHz 79 .rst_n (rst_n), 80 81 //user led output 82 .led_data (led_data), 83 .led595_clk (led595_clk), 84 .led595_dout (led595_dout), 85 .led595_latch (led595_latch) 86 ); 87 88 endmodule

- traffic_light(交通灯控制部分)

1 `timescale 1ns/1ns 2 module traffic_light 3 ( 4 clk, 5 rst_n, 6 7 key_flag, 8 9 led_east, 10 //led_wast, 11 12 led_south 13 //led_nouth 14 15 ); 16 parameter TIME_1S = 50_000_000; 17 18 input clk; 19 input rst_n; 20 21 output [2:0] led_east; 22 //output [2:0] led_wast; 23 output [2:0] led_south; 24 //output [2:0] led_nouth; 25 output key_flag; 26 27 reg [2:0] led_east; 28 //reg [2:0] led_wast; 29 reg [2:0] led_south; 30 //reg [2:0] led_nouth; 31 32 reg key_flag; 33 34 35 reg [29:0] cnt; 36 reg [7:0] cnt_l; 37 38 //--------------------------------------------------------- 39 //led_east 40 always@(posedge clk or negedge rst_n) 41 begin 42 if(!rst_n) 43 led_east <= 3'b001;//G 44 else if((cnt_l == 39)&&(cnt == TIME_1S-1'b1)) 45 led_east <= 3'b010;//Y 46 else if((cnt_l == 43)&&(cnt == TIME_1S-1'b1)) 47 led_east <= 3'b100;//R 48 else if((cnt_l == 67)&&(cnt == TIME_1S-1'b1)) 49 led_east <= 3'b001;//G 50 else 51 led_east <= led_east; 52 end 53 54 //--------------------------------------------------------- 55 //wast 56 //always@(posedge clk or negedge rst_n) 57 //begin 58 // if(!rst_n) 59 // led_wast <= 3'b001; 60 // else if((cnt_l == 39)&&(cnt == TIME_1S-1'b1)) 61 // led_wast <= 3'b010; 62 // else if((cnt_l == 43)&&(cnt == TIME_1S-1'b1)) 63 // led_wast <= 3'b100; 64 // else if((cnt_l == 67)&&(cnt == TIME_1S-1'b1)) 65 // led_wast <= 3'b001; 66 // else 67 // led_wast <= led_wast; 68 //end 69 //---------------------------------------------------------///////////////////////////////////// 70 //led_south 71 always@(posedge clk or negedge rst_n) 72 begin 73 if(!rst_n) 74 led_south <= 3'b100;//R 75 else if((cnt_l == 43)&&(cnt == TIME_1S-1'b1)) 76 led_south <= 3'b001;//G 77 else if((cnt_l == 63)&&(cnt == TIME_1S-1'b1)) 78 led_south <= 3'b010;//Y 79 else if((cnt_l == 67)&&(cnt == TIME_1S-1'b1)) 80 led_south <= 3'b100;//R 81 else 82 led_south <= led_south; 83 end 84 //--------------------------------------------------------- 85 //led_nouth 86 //always@(posedge clk or negedge rst_n) 87 //begin 88 // if(!rst_n) 89 // led_nouth <= 3'b100;//R 90 // else if((cnt_l == 43)&&(cnt == TIME_1S-1'b1)) 91 // led_nouth <= 3'b001;//G 92 // else if((cnt_l == 63)&&(cnt == TIME_1S-1'b1)) 93 // led_nouth <= 3'b010;//Y 94 // else if((cnt_l == 67)&&(cnt == TIME_1S-1'b1)) 95 // led_nouth <= 3'b100;//R 96 // else 97 // led_nouth <= led_nouth; 98 //end 99 //---------------------------------------------------------- 100 always@(posedge clk or negedge rst_n) 101 begin 102 if(!rst_n) 103 cnt <= 0; 104 else if(cnt==(TIME_1S-1'b1)) 105 cnt <= 0; 106 else 107 cnt <= cnt+1'b1; 108 end 109 110 always@(posedge clk or negedge rst_n) 111 begin 112 if(!rst_n) 113 cnt_l <= 0; 114 else if((cnt==(TIME_1S-1'b1))&&(cnt_l==8'd67)) 115 cnt_l <= 0; 116 else if(cnt==(TIME_1S-1'b1)) 117 cnt_l <= cnt_l+1'b1; 118 else 119 cnt_l <= cnt_l; 120 end 121 122 //---------------------------------------------------------------------------- 123 //wire key_trigger = ((cnt==TIME_1S-1'b1)&&((cnt_l==8'd39)||(cnt_l==8'd43)||(cnt_l==8'd67)||(cnt_l==8'd63))) ? 1'b1 : 1'b0; 124 125 wire key_trigger = (cnt==(TIME_1S-1'b1)) ? 1'b1 : 1'b0; 126 //--------------------------------- 127 //Lag 1 clock for valid read enable 128 always@(posedge clk or negedge rst_n) 129 begin 130 if(!rst_n) 131 key_flag <= 0; 132 else 133 key_flag <= key_trigger; 134 end 135 136 endmodule

- led_input_display(把(交通灯控制部分的)数据打一拍(送给74595))

1 `timescale 1ns/1ns 2 module led_input_display 3 #( 4 parameter LED_WIDTH = 8 5 ) 6 ( 7 //global clock 8 input clk, 9 input rst_n, 10 11 //user interface 12 input led_en, 13 input [LED_WIDTH-1:0] led_value, 14 15 //led interface 16 output reg [LED_WIDTH-1:0] led_data 17 ); 18 19 //-------------------------------------- 20 always@(posedge clk or negedge rst_n) 21 begin 22 if(!rst_n) 23 led_data <= 8'b001_00_100; 24 else if(led_en) 25 led_data <= led_value; 26 else 27 led_data <= led_data; 28 end 29 30 endmodule

- led_74595_driver(串转并-进行显示)

1 `timescale 1ns/1ns 2 module led_74595_driver 3 ( 4 //global clock 5 input clk,//50MHz 6 input rst_n, 7 8 //user led output 9 input [7:0] led_data, 10 11 output led595_clk, 12 output led595_dout, 13 output led595_latch 14 ); 15 //----------------------------- 16 //update display when led_data is update 17 //generate led_data_r and update_flag 18 reg [7:0] led_data_r; 19 reg update_flag; 20 always@(posedge clk or negedge rst_n) 21 begin 22 if(!rst_n) 23 begin 24 led_data_r <= 0; 25 update_flag <= 1; 26 end 27 else 28 begin 29 led_data_r <= led_data; 30 update_flag <= (led_data_r == led_data)?1'b1:1'b0; 31 end 32 end 33 //------------------------------ 34 //74HC595 clk delay for enough setup time 35 // generate shift_flag and shift_clk 36 localparam DELAY_CNT = 3'd7; 37 reg shift_state; 38 reg [2:0] delay_cnt; 39 always@(posedge clk or negedge rst_n) 40 begin 41 if(!rst_n) 42 delay_cnt <= 0; 43 else if(shift_state == 1'b1) 44 delay_cnt <= (delay_cnt < DELAY_CNT) ? (delay_cnt+1'b1):3'd0; 45 else 46 delay_cnt <= 0; 47 end 48 wire shift_clk = (delay_cnt > DELAY_CNT/2) ? 1'b1 : 1'b0; 49 wire shift_flag = (delay_cnt == DELAY_CNT) ? 1'b1 : 1'b0; 50 //---------------------------------------- 51 //74HC595 shift data output state 52 reg [3:0] led_cnt; 53 always@(posedge clk or negedge rst_n) 54 begin 55 if(!rst_n) 56 begin 57 shift_state <= 0; 58 led_cnt <= 0; 59 end 60 else 61 begin 62 case(shift_state) 63 0: begin 64 led_cnt <= 0; 65 if(update_flag) 66 shift_state <= 1'b1; 67 else 68 shift_state <= 0; 69 end 70 1: begin 71 if(shift_flag) 72 begin 73 if(led_cnt < 4'd8) 74 begin 75 led_cnt <= led_cnt + 1'b1; 76 shift_state <= 1'd1; 77 end 78 else 79 begin 80 led_cnt <= 0; 81 shift_state <= 0; 82 end 83 end 84 else 85 begin 86 led_cnt <= led_cnt; 87 shift_state <= shift_state; 88 end 89 end 90 endcase 91 end 92 end 93 assign led595_dout = (led_cnt < 4'd8&&shift_state == 1'b1) ? led_data[3'd7-led_cnt]: 1'b0; 94 assign led595_clk = (led_cnt < 4'd8&&shift_state == 1'b1) ? shift_clk : 1'b0; 95 assign led595_latch = (led_cnt ==4'd8&&shift_state == 1'b1) ? 1'b1 : 1'b0; 96 97 98 endmodule

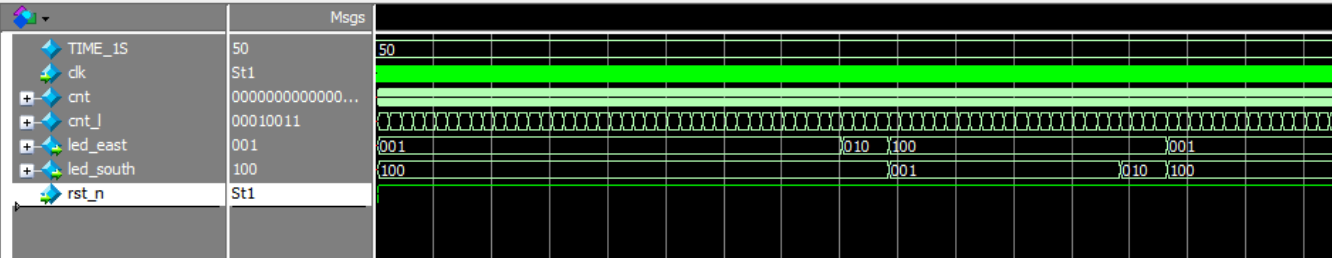

- 仿真

//-----------------------------------------------------------------------------------------

- 仿真代码--第一部分 --traffic_light

1 `timescale 1ns/1ns 2 module traffic_light 3 ( 4 clk, 5 rst_n, 6 7 //key_flagï¼ 8 led_east, 9 //led_wast, 10 11 led_south 12 //led_nouth 13 14 ); 15 parameter TIME_1S = 50; 16 17 input clk; 18 input rst_n; 19 20 output [2:0] led_east; 21 //output [2:0] led_wast; 22 output [2:0] led_south; 23 //output [2:0] led_nouth; 24 //output key_flag; 25 26 reg [2:0] led_east; 27 //reg [2:0] led_wast; 28 reg [2:0] led_south; 29 //reg [2:0] led_nouth; 30 31 //reg key_flag; 32 33 34 reg [29:0] cnt; 35 reg [7:0] cnt_l; 36 37 //--------------------------------------------------------- 38 //led_east 39 always@(posedge clk or negedge rst_n) 40 begin 41 if(!rst_n) 42 led_east <= 3'b001;//G 43 else if((cnt_l == 39)&&(cnt == TIME_1S-1'b1)) 44 led_east <= 3'b010;//Y 45 else if((cnt_l == 43)&&(cnt == TIME_1S-1'b1)) 46 led_east <= 3'b100;//R 47 else if((cnt_l == 67)&&(cnt == TIME_1S-1'b1)) 48 led_east <= 3'b001;//G 49 else 50 led_east <= led_east; 51 end 52 53 //--------------------------------------------------------- 54 //wast 55 //always@(posedge clk or negedge rst_n) 56 //begin 57 // if(!rst_n) 58 // led_wast <= 3'b001; 59 // else if((cnt_l == 39)&&(cnt == TIME_1S-1'b1)) 60 // led_wast <= 3'b010; 61 // else if((cnt_l == 43)&&(cnt == TIME_1S-1'b1)) 62 // led_wast <= 3'b100; 63 // else if((cnt_l == 67)&&(cnt == TIME_1S-1'b1)) 64 // led_wast <= 3'b001; 65 // else 66 // led_wast <= led_wast; 67 //end 68 //---------------------------------------------------------///////////////////////////////////// 69 //led_south 70 always@(posedge clk or negedge rst_n) 71 begin 72 if(!rst_n) 73 led_south <= 3'b100;//R 74 else if((cnt_l == 43)&&(cnt == TIME_1S-1'b1)) 75 led_south <= 3'b001;//G 76 else if((cnt_l == 63)&&(cnt == TIME_1S-1'b1)) 77 led_south <= 3'b010;//Y 78 else if((cnt_l == 67)&&(cnt == TIME_1S-1'b1)) 79 led_south <= 3'b100;//R 80 else 81 led_south <= led_south; 82 end 83 //--------------------------------------------------------- 84 //led_nouth 85 //always@(posedge clk or negedge rst_n) 86 //begin 87 // if(!rst_n) 88 // led_nouth <= 3'b100;//R 89 // else if((cnt_l == 43)&&(cnt == TIME_1S-1'b1)) 90 // led_nouth <= 3'b001;//G 91 // else if((cnt_l == 63)&&(cnt == TIME_1S-1'b1)) 92 // led_nouth <= 3'b010;//Y 93 // else if((cnt_l == 67)&&(cnt == TIME_1S-1'b1)) 94 // led_nouth <= 3'b100;//R 95 // else 96 // led_nouth <= led_nouth; 97 //end 98 //---------------------------------------------------------- 99 always@(posedge clk or negedge rst_n) 100 begin 101 if(!rst_n) 102 cnt <= 0; 103 else if(cnt==(TIME_1S-1'b1)) 104 cnt <= 0; 105 else 106 cnt <= cnt+1'b1; 107 end 108 109 always@(posedge clk or negedge rst_n) 110 begin 111 if(!rst_n) 112 cnt_l <= 0; 113 else if((cnt==(TIME_1S-1'b1))&&(cnt_l==8'd67)) 114 cnt_l <= 0; 115 else if(cnt==(TIME_1S-1'b1)) 116 cnt_l <= cnt_l+1'b1; 117 else 118 cnt_l <= cnt_l; 119 end 120 121 //---------------------------------------------------------------------------- 122 //wire key_trigger = ((cnt==TIME_1S-1'b1)&&((cnt_l==8'd39)||(cnt_l==8'd43)||(cnt_l==8'd67)||(cnt_l==8'd63))) ? 1'b1 : 1'b0; 123 124 //wire key_trigger = (cnt==(TIME_1S-1'b1)) ? 1'b1 : 1'b0; 125 //--------------------------------- 126 //Lag 1 clock for valid read enable 127 //always@(posedge clk or negedge rst_n) 128 //begin 129 // if(!rst_n) 130 // key_flag <= 0; 131 // else 132 // key_flag <= key_trigger; 133 //end 134 135 endmodule

- 仿真代码--第二部分 --traffic_light_tb

1 `timescale 1ns/1ns 2 module traffic_light_tb; 3 4 //------------------------------------------ 5 //clock generate module 6 reg clk; 7 reg rst_n; 8 localparam PERIOD = 20; //50MHz 9 initial 10 begin 11 clk = 0; 12 forever #(PERIOD/2) 13 clk = ~clk; 14 end 15 16 task task_reset; 17 begin 18 rst_n = 0; 19 repeat(2) @(negedge clk); 20 rst_n = 1; 21 end 22 endtask 23 //------------------------------------------ 24 wire [2:0] led_east; 25 wire [2:0] led_south; 26 traffic_light u_traffic_light 27 ( 28 .clk(clk), 29 .rst_n(rst_n), 30 31 .led_east(led_east), 32 .led_south(led_south) 33 ); 34 35 //--------------------------------------- 36 //system initialization 37 task task_sysinit; 38 begin 39 // e_light = 3'b100; //?? R 40 // s_light = 3'b001; //?? G 41 end 42 endtask 43 44 45 //---------------------------------------- 46 //testbench of the RTL 47 initial 48 begin 49 50 #200; 51 52 task_sysinit; 53 task_reset; 54 55 end 56 57 endmodule

- 仿真时序图