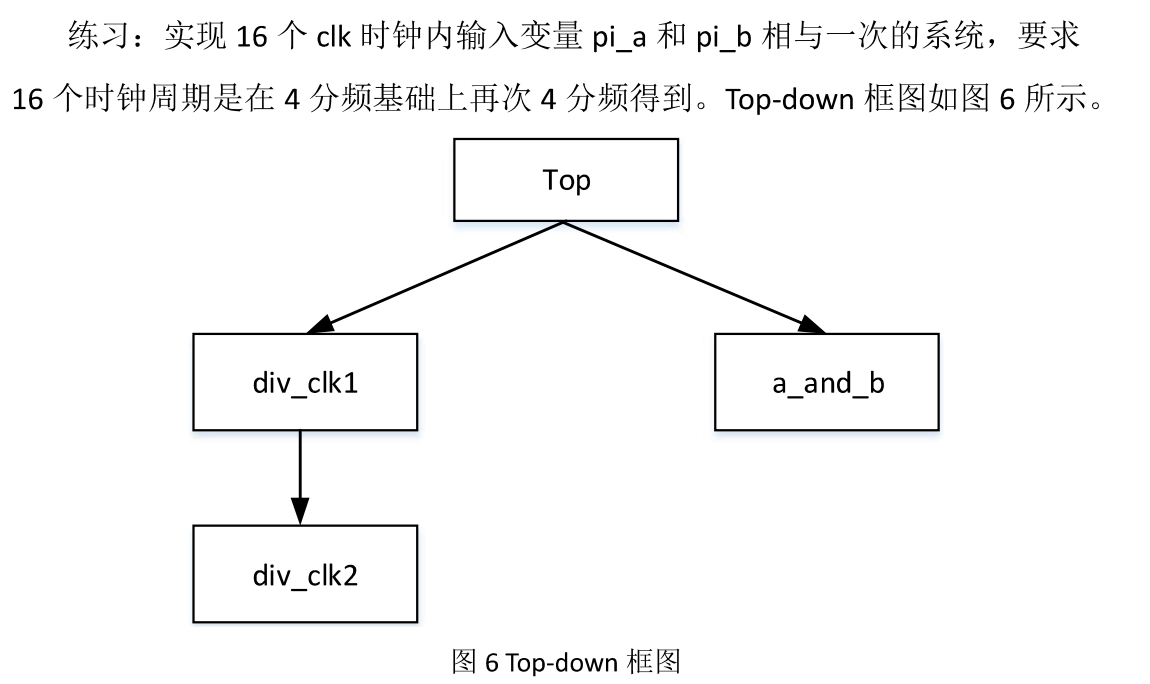

一设计功能:(一)用两个分频模块,实现16分频,且让输入a 和b在16个系统时钟内,相与一次。

|

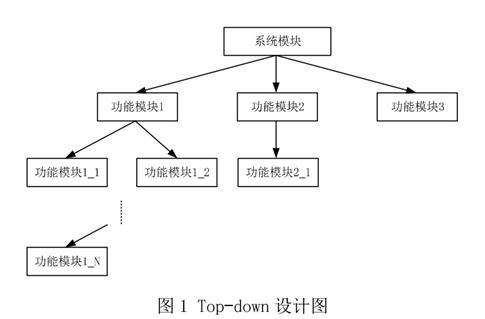

(二)模块化设计思想(结构化思维)

拆分,即把一个系统划分成多个功能模块,控制模块,组合模块。然后从功能模块开始,循序渐进一个个设计好,再把所有的模块连接起来,实现系统功能。

|

二设计输入

(一)顶层模块:定义输入输出端口,实现各个模块的连接通过例化

|

//顶层模块 module top( input wire Clk, input wire Rst_n, input wire a, input wire b, output wire c );

wire p_flag;//connect po_flag0 to pi_flag0 wire flag;//connect po_flag to pi_flag //例化 div_clk2 div_clk2m0( .clk(Clk), .rst_n(Rst_n), .po_flag0(p_flag) );

div_clk1 div_clk1m0( .clk(Clk), .rst_n(Rst_n), .pi_flag0(p_flag), .po_flag(flag)

);

a_and_b a_and_bm0( . clk(Clk), . rst_n(Rst_n), . pi_flag(flag), . pi_a(a), . pi_b(b), . po_c(c) );

endmodule |

(二)分频模块:两个分频模块实现16分频

|

//分频模块2实现四分频并输出一个分频标志信号 module div_clk2( input wire clk, input wire rst_n, output reg po_flag0 ); wire rst; reg [1:0] div_cnt; assign rst = ~rst_n;

//div cnt

always @(posedge clk)begin if(rst == 1'b1 )begin div_cnt <= 'd0; end else if (div_cnt == 'd3) begin div_cnt <= 'd0; end else div_cnt <= div_cnt + 1'b1;

end

//po_flag0 always @(posedge clk) begin if (rst == 1'b1 ) begin po_flag0<= 1'b0; end else if(div_cnt== 'd2)begin po_flag0 <= 1'b1; end else begin po_flag0 <= 1'b0; end end endmodule //分频模块1在分频模块2的基础上,实现16分频并输出对应的分频标志信号 module div_clk1( input wire clk, input wire rst_n, input wire pi_flag0, output reg po_flag

); wire rst; assign rst = ~rst_n;

//div_cnt under the pi_flag0 reg [1:0]div_cnt; always@(posedge clk) if(rst) div_cnt<=0; else if(div_cnt==2'd3) div_cnt<=0; else if(pi_flag0) div_cnt<=div_cnt+1'b1; else div_cnt<=div_cnt;

//po_flag always@(posedge clk) if(rst) po_flag<=0; else if(div_cnt==2'd3 & pi_flag0)//lack & pi_flag0 is error po_flag<=1'b1; else po_flag<=0; endmodule |

(三)相与模块

|

//相与模块,在16分频的标志信号下,相与 module a_and_b( input wire clk, input wire rst_n, input wire pi_flag, input wire pi_a, input wire pi_b, output reg po_c ); wire rst; assign rst = ~rst_n; always@(posedge clk) if(rst==1'b1) po_c<=1'b0; else if(pi_flag==1'b1) po_c<=pi_a & pi_b; else po_c<=0;

endmodule |

三总结

(一)常见疑问及答案

1.在不同模块的信号,通过传输线连在一起,那这些信号会有延时嘛(即变化实际不一样)?

实际上,在不同模块的同一信号如po_flag, pi_flag,flag,他们通过flag信号连在一起,是同时变化的。

2.在什么情况下存在延时?

存在延时一个时钟的会是在时序逻辑的always里,如下面的赋值语句中

|

else if(div_cnt== 'd2)begin po_flag <= 1'b1; po_flag在仿真中,实际为高电平在分频计数值为3. else if (pi_flag == 1'b1) begin po_c <= pi_a & pi_b; end 而在相与模块里,发生相与操作是在po_flag为高后,再延迟一个时钟,故相与在分频计数值为2后,延迟了两个时钟周期, |

3.注意下面这句易出错

else if(div_cnt==2'd3 & pi_flag0)//lack & pi_flag0 is error

po_flag<=1'b1;

若缺少后面的与条件,会持续四个时钟周期,由于div_cnt每四个时钟更新。

(二)设计注意点

1.sublime列编辑:shift+鼠标右键。

2.赛灵思要求为同步复位,故开发板是异步复位,则程序设计为

wire rst;

assign rst = ~rst_n;

3.在例化,模块的接口是输入,可以连接wire或reg型变量。但模块的接口是输出,必须连接wire型。

4.基本语法准则:即always赋值的输出信号,只能为reg型。而assign赋值的输出信号,只能为wire型。

(三)仿真

|

`timescale 1ns/1ns `define clk_period 20 module top_tb(); reg clk; reg rst_n; reg a; reg b; wire c; top top_m0( .Clk(clk), .Rst_n(rst_n), .a(a), .b(b), .c(c) );

initial clk =1; always#(`clk_period/2) clk = ~clk; initial begin rst_n =0; a=0; b=0; #(`clk_period*2); rst_n =1; #(`clk_period*40); rst_n = 0; #(`clk_period*12); $stop;

end always#(`clk_period*2) a = {$random}; always#(`clk_period*2) b= {$random};

endmodule //波形: |