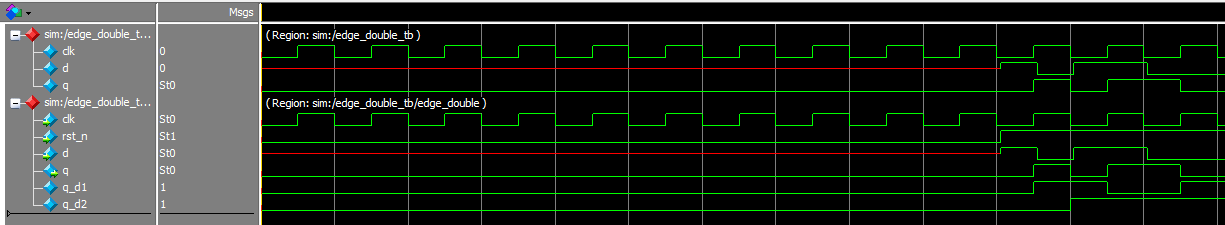

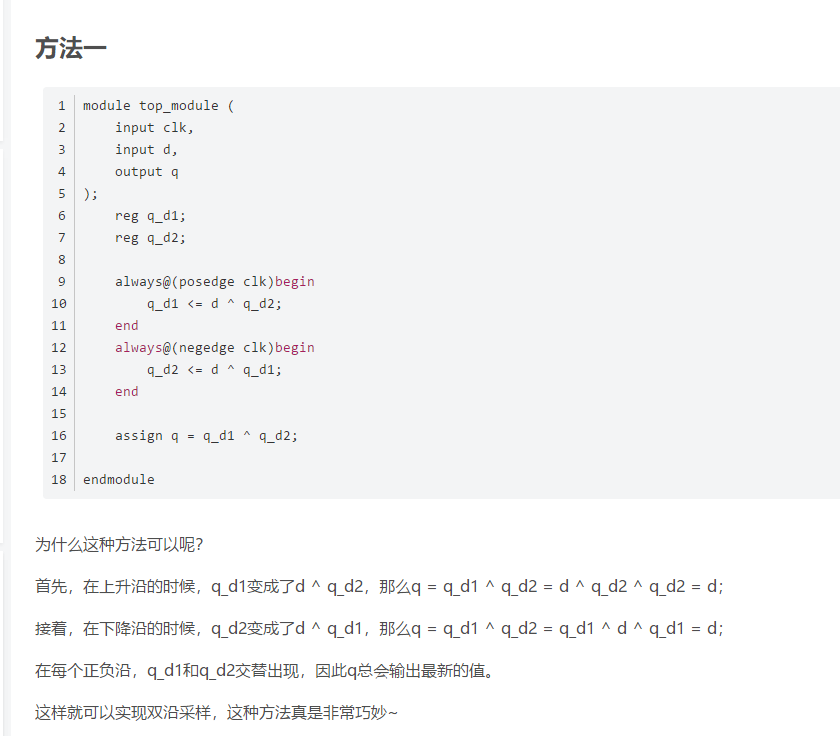

代码:实际设计时要加上复位信号,保证寄存器有初值。

module edge_double( clk, rst_n, d, q ); input clk; input rst_n; input d; output q; reg q_d1; reg q_d2; always@(posedge clk or negedge rst_n) if(!rst_n) q_d1<=0; else q_d1<=d^q_d2; always@(negedge clk or negedge rst_n) if(!rst_n) q_d2<=0; else q_d2<=d^q_d1; assign q=q_d1^q_d2; endmodule