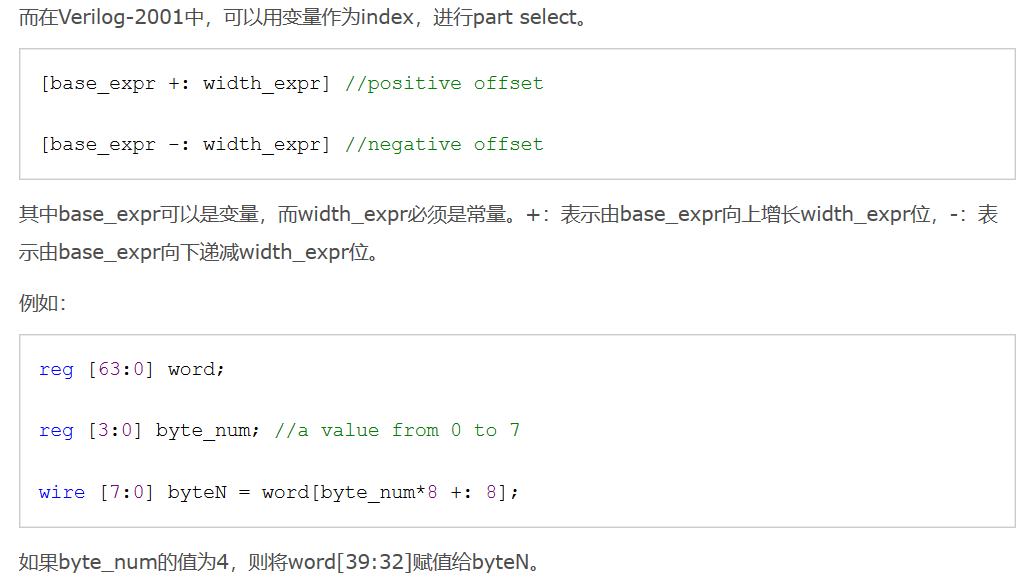

- 利用的是2001中 bit slicing 特性。

给我的感觉是:verilog不会去计算 sel4+3 和 sel4 之间的差值。所以在上面一道题的时候,由于是选择1位出来(且sel是8位,位数是固定的!但值可变),所以没有问题。

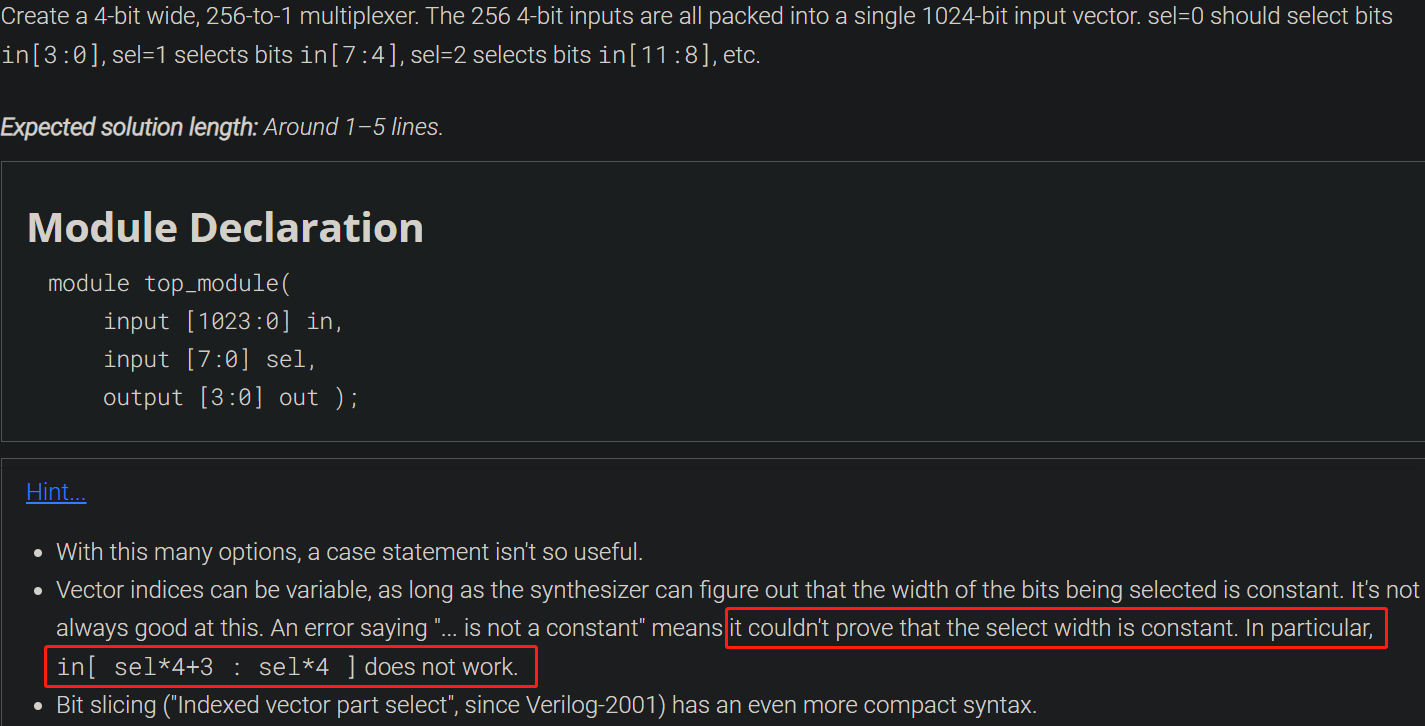

针对上述的说法,其实这道题有两种解决方法:①利用 bit slicing 特性;②依然利用选择位sel是固定的位数去挑出某一位,然后再拼接起来就好。

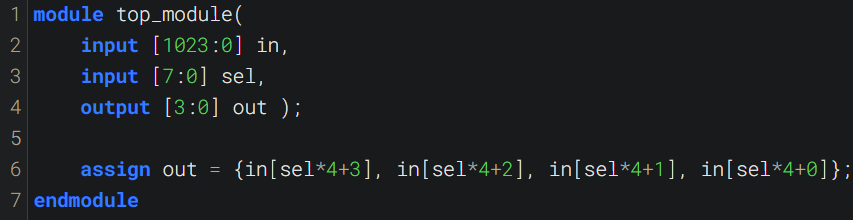

如下图所示:

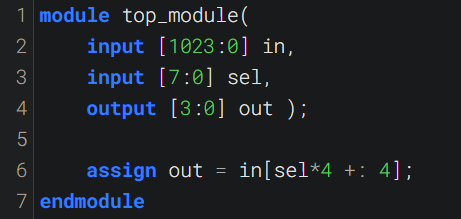

①

module top_module(

input [1023:0] in,

input [7:0] sel,

output [3:0] out );

assign out = in[sel*4 +: 4];

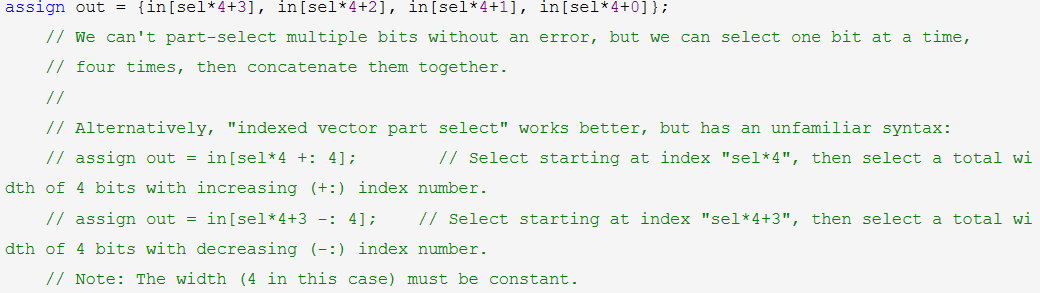

endmodule②

in[sel4+0] : (sel4+0 位数是固定的:8位,但值是可变的)&&(只选这一位出来)

module top_module(

input [1023:0] in,

input [7:0] sel,

output [3:0] out );

assign out = {in[sel*4+3], in[sel*4+2], in[sel*4+1], in[sel*4+0]};

endmodule