1. 实验简介

本实验练习使用AN9767模块,实验中使用的模块是采用ANALOG DEVICES公司的AD9767芯片,支持独立双通道、14位、125MSPS的数模转换。在教程中介绍了利用该模块与FPGA开发板相连输出双通道14位的三角波,然后通过示波器查看把输出的三角波的波形。

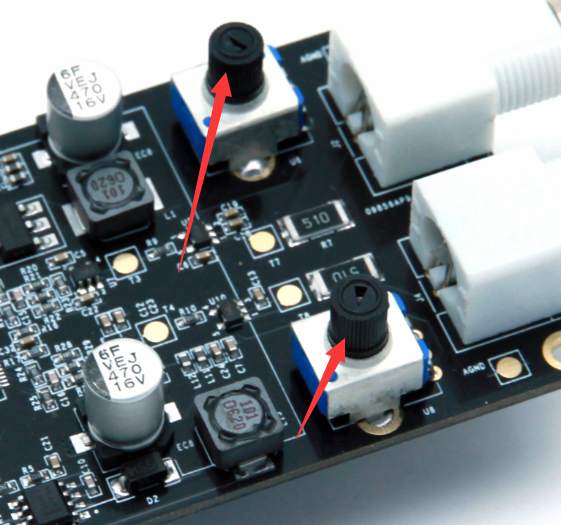

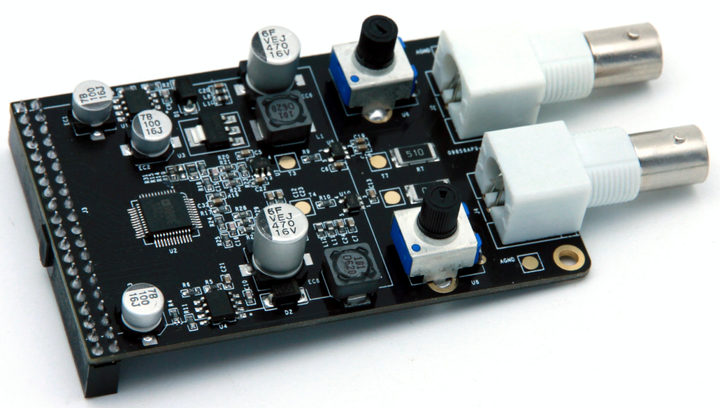

AN9767模块实物照片如下:

AN9767模块正面图

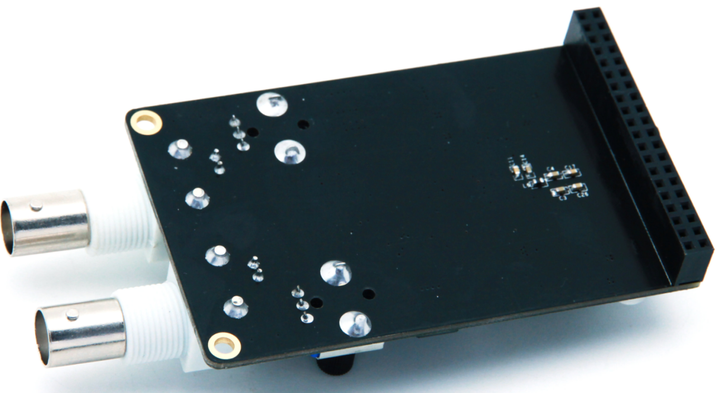

AN9767模块正面图 AN9767模块背面图

AN9767模块背面图

AN9767双通道DA模块的详细参数:

- DA转换芯片:AD9767;

- 通道数:2通道;

- DA转换位数:14bit;

- DA更新速率:125 MSPS;

- 输出电压范围:-5V~+5V;

- 模块PCB层数:4层,独立的电源层和GND层;

- 模块接口:40针2.54mm间距排座,方向向下;

- 工作温度:-40°~85° 模块使用芯片均满足工业级温度范围

- 输出接口:2路BNC模拟输出接口(用BNC线可以直接连接到示波器);

2. 实验原理

AN9767模块实验原理见《AD9767双通道正弦波产生例程》中相关章节内容,这里不再重复。

ALINX:【紫光同创国产FPGA教程】【第二十章】AD9767双通道正弦波产生例程

3. 程序设计

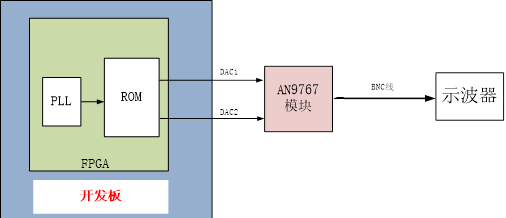

例程中提供了AN9767模块的DA测试程序,通过AN9767模块来实现三角波信号的输出。

三角波测试程序是通过在FPGA中产生一个计数模块,然后把计数模块的数据输出给AN9767模块进行数模的转换,从而得到三角波的模拟信号。三角波测试程序的示意图如下:

双通道三角波发生程序

`timescale1ns/1ps

//////////////////////////////////////////////////////////////////////////////////

//Two tri wave outputs -10V ~ +10V

//////////////////////////////////////////////////////////////////////////////////

module ad9767_test

(

input sys_clk,// input clock 50Mhz

output da1_clk,//AD9767 CH1 clock

output da1_wrt,//AD9767 CH1 enable

output[13:0] da1_data,//AD9767 CH1 data output

output da2_clk,//AD9767 CH2 clock

output da2_wrt,//AD9767 CH2 enable

output[13:0] da2_data //AD9767 CH2 data output

);

reg[15:0] trig_data;

wire clk_125M;

assign da1_clk=clk_125M;

assign da1_wrt=clk_125M;

assign da1_data=trig_data;

assign da2_clk=clk_125M;

assign da2_wrt=clk_125M;

assign da2_data=trig_data;

//DA output sin waveform

always@(negedge clk_125M)

begin

if(trig_data ==14'h3fff)

trig_data <=0;

else

trig_data <= trig_data +1'b1;

end

PLL PLL_inst

(// Clock in ports

.clk_in1 (sys_clk ),// IN

// Clock out ports

.clk_out1 (),// OUT

.clk_out2 (clk_125M ),// OUT

// Status and control signals

.reset (1'b0),// IN

.locked ()

);

endmodule

程序中通过一个PLL IP来产生125M的DA输出时钟,同时利用计数模块产生三角波的数据,并同时输出到通道1和通道2的DA数据线上。

4. 实验现象

1)将AN9767模块插入开发板的 J8扩展口,注意1脚对齐,不要插错、插偏,不能带电操作。

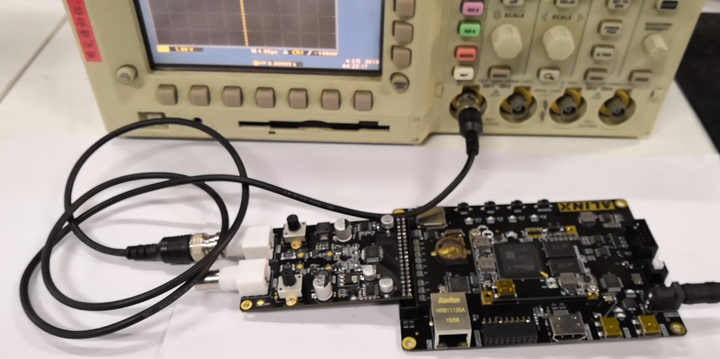

2)用我们提供的BNC线连接AN9767的输出到示波器 的输入如下图,然后开发板上电,下载程序就可以从示波器上观察从DA模块输出的模拟信号的波形了。

AN9767与开发板连接图

AN9767与开发板连接图

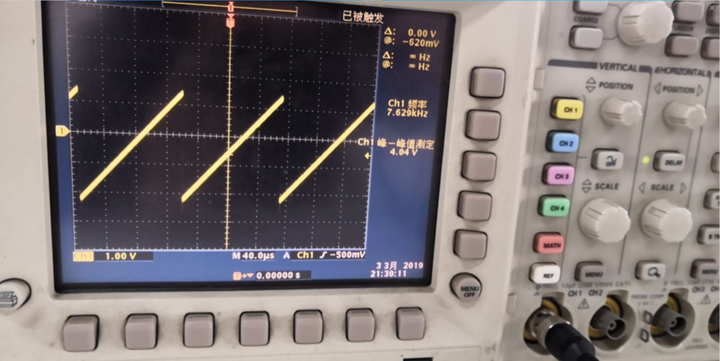

3)示波器上看到的三角波如下:

4) 用户也可以通过调节AN9767模块上的可调电阻来改变2个通道输出波形的幅度。