1、组合逻辑的竞争冒险

组合逻辑:任何时刻电路的稳定输出,仅仅取决于该时刻各个输入变量的取值。

组合逻辑的竞争冒险:当输入信号同事变化时,组合逻辑必然产生毛刺。

解决方法:用时序逻辑,每次寄存器的输出结果取决于上一个时钟的寄存器的值,不会产生毛刺。

2、寄存器reg可以用在时序逻辑也可以用在组合逻辑

时序逻辑就是平时写的clk触发

组合逻辑例如always@(b) out1 =~ b;

触发器具有记忆性原因:普通的门电路输出信号只取决于当前输入信号,无记忆性,但是触发器

的输出还和之前的状态有关,比如JK触发器:Qn+1 = JQn_ + K_Qn

3、时序,组合逻辑,阻塞与非阻塞区别

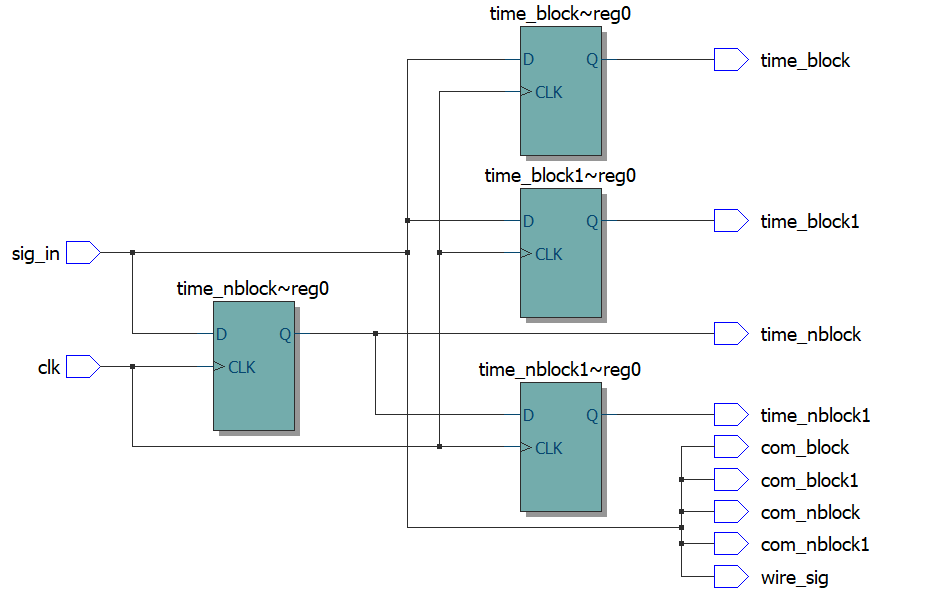

//time 非阻塞 always @(posedge clk) begin time_nblock <= sig_in; time_nblock1 <= time_nblock; end //time 阻塞 always @(posedge clk) begin time_block = sig_in; time_block1 = time_block; end //combine 非阻塞 always @(*) begin com_nblock <= sig_in; com_nblock1 <= com_nblock; end //combine 阻塞 always @(*) begin com_block = sig_in; com_block1 = com_block; end assign wire_sig = sig_in;

综合出来的电路

时序电路,会生成D触发器,根据电路可以看出阻塞赋值和非阻塞赋值,一个always块结束之后,阻塞赋值结果都是一样的,但是非阻塞

赋值的话,是同事变化的,time_nblock得到sig的同时,time_nblock1也得到time_nblock之前得值。

阻塞赋值从电路上看,非阻塞和阻塞都是一样得,modelsim仿真也是这么个情况。

一般来说,时序逻辑用非阻塞赋值,组合逻辑用阻塞赋值。

4、与门

assign q = (al == 1) ? d : 0;

5、亚稳态

亚稳态定义:在进行fpga设计时,往往只关心“0”和"1"两种状态。然而在工程实践中,除了”0“、”1“外还有其他状态,亚稳态就是其中之一。

亚稳态是指触发器或锁存器无法在某个规定时间段内达到一个可确认的状态[1]。当一个触发器进入亚稳态时,既无法预测该单元的输出电平,

也无法预测何时输出才能稳定在某个正确的电平上。在亚稳态期间,触发器输出一些中间级电平,甚至可能处于振荡状态,并且这种无用的输

出电平可以沿信号通道上的各个触发器级联式传播下去。亚稳态是异步数字电路设计中的固有现象,但是由于其偶发性和温度敏感性的特点,

在产品前期测试过程中很难发现。

亚稳态产生的原因:1、时序不满足,例如不满足建立时间和保持时间。

2、不同时钟域接口

例如当数据刚传过来的时候,clkb恰好来了一个上升沿

亚稳态的解决方法:1、单比特信号打两拍寄存器,我看网上亚稳态有一个震荡周期,如果震荡周期大于一个时钟的话那么一级缓存之后仍然会有亚稳态

现象,所以两级缓存就比较靠谱了。

2、多比特信号 fifo