嵌套向量中断控制器(NVIC )

简介

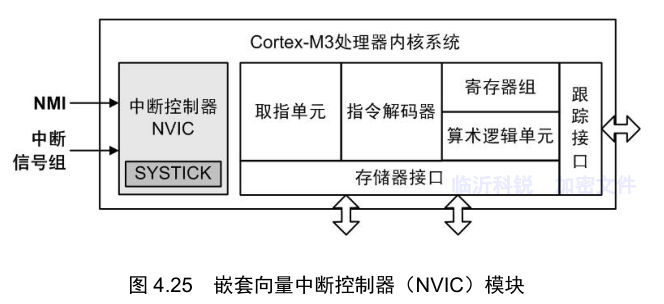

嵌套向量中断控制器(NVIC)是 Cortex-M3 处理器的一个内部器件,它与 CPU 内核紧密

耦合,共同完成对中断的响应,降低了中断延时,使得最新发生的中断可以得到高效处理。

NVIC 的寄存器以存储器映射的方式来访问,除了包含控制寄存器和中断控制逻辑之外,

NVIC 还包含 SysTick 定时器和调试控制模块。

LPC178x/177x系列Cortex-M3处理器支持41个嵌套向量中断和32个可编程的中断优先级。

此外,NVIC 还支持一个不可屏蔽中断(NMI)输入。

NVIC 的访问地址是 0xE000 E000,所有 NVIC 的中断控制/状态寄存器都只能在特权级下

访问。但有一个例外——软件触发中断寄存器可以在用户级下访问以产生软件中断。所有的中

断控制/状态寄存器均可按字/半字/字节的方式进行访问,特殊功能寄存器只能通过 MRS、MSR

或 CPS 指令来访问。

特性

LPC178x/177x 系列 Cortex-M3 处理器 NVIC 模块特性如下:

嵌套向量中断控制器,是 ARM Cortex-M3 不可或缺的组成部件;

与内核紧密联系的中断控制器,可支持低中断延时;

可对系统异常和外设中断进行控制;

LPC178x/177x 的 NVIC 支持 41 个向量中断;

32 个可编程的中断优先级级别,具有硬件优先级屏蔽;

可重复定位的向量表;

不可屏蔽的中断;

软件中断功能。

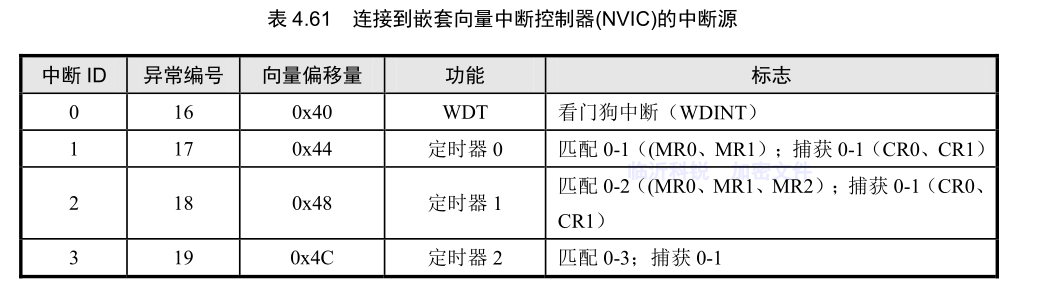

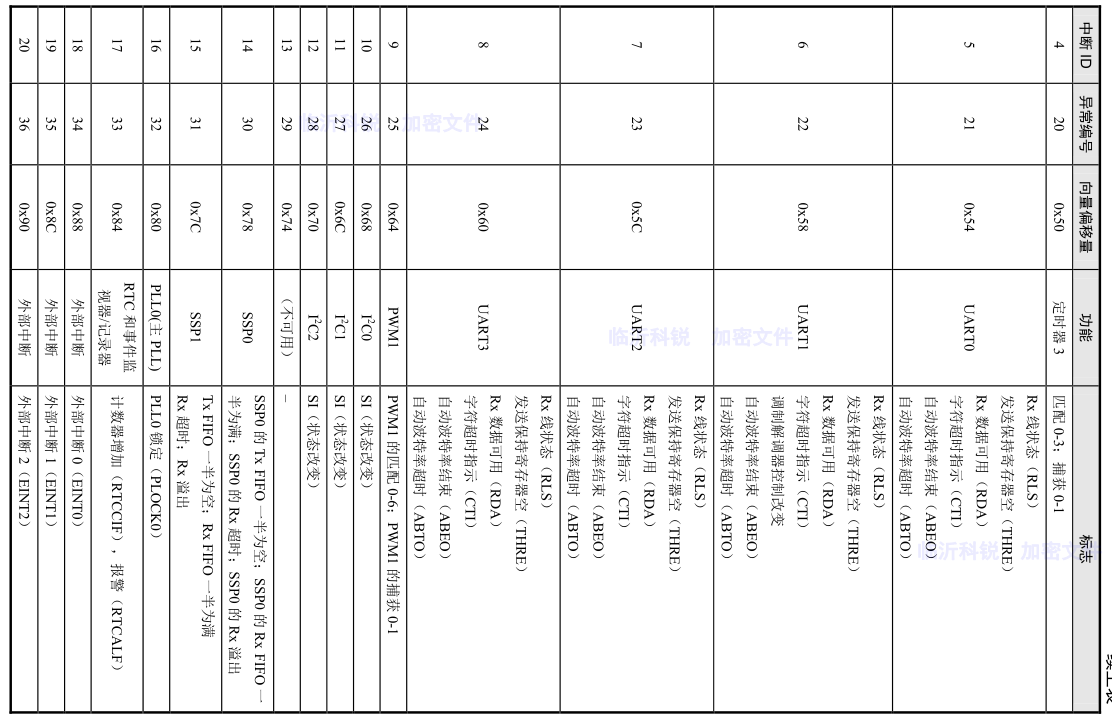

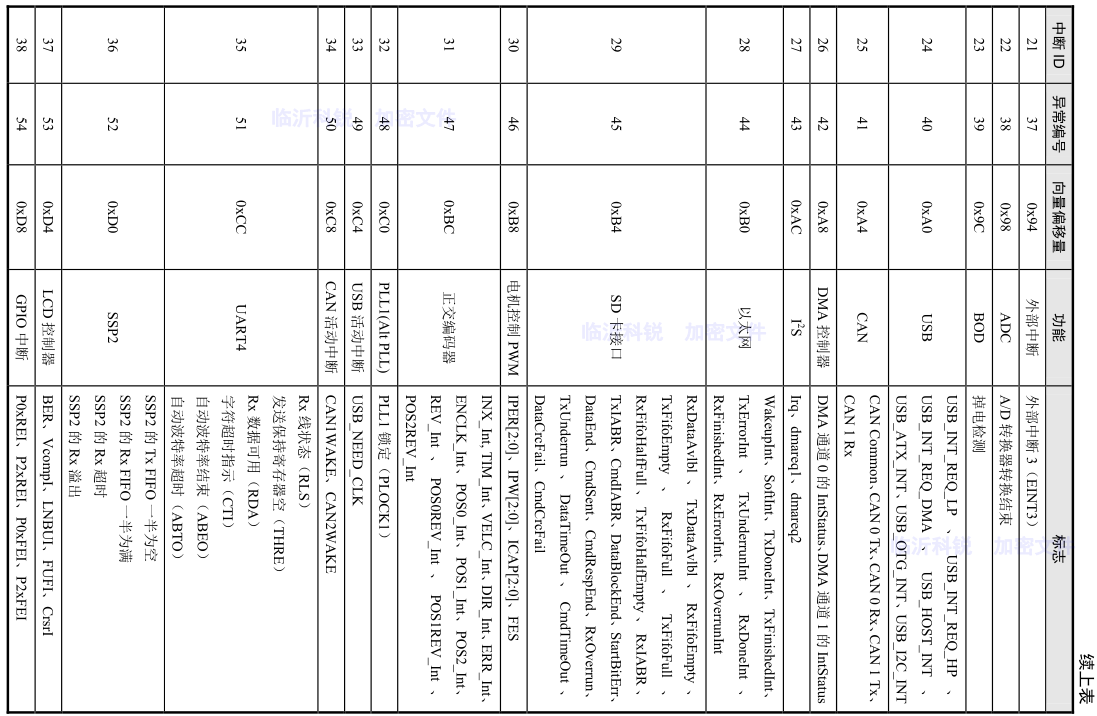

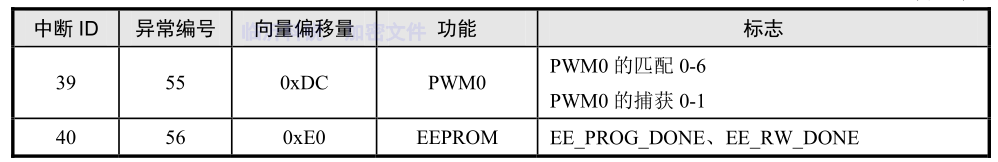

中断源

表 4.61 列出了每一个外设所对应的中断源。每个外围设备可以有一条或几条中断线连接到

NVIC,多个中断源也可共用一条中断线。

此外,NVIC 还可处理不可屏蔽的中断(NMI)。为了能令 NMI 从外部信号中进行操作,

必须要把 NMI 功能连接到相关的器件引脚(P2[10] / EINT0n / NMI)上。接入时,引脚为逻辑

1,即可处理 NMI 操作。

寄存器描述

中断信号可划分为外设中断和系统异常两类,NVIC 寄

存器组主要包含控制寄存器、状态寄存器、挂起设置/清除寄存器、使能/除能寄存器、优先级

设置寄存器、活动状态寄存器和特殊功能寄存器。

每个中断在 NVIC 中都有若干相关寄存器:

使能与除能寄存器;

挂起设置与清除寄存器;

优先级寄存器;

活动状态寄存器。

另外,下列寄存器对中断处理也有一定的影响:

异常屏蔽寄存器(PRIMASK、FAULTMASK 和 BASEPRI)

向量表偏移量寄存器;

软件触发中断寄存器;

优先级分组寄存器。

中断的使能与除能

Cortex-M3 中断的使能与除能采用独立的寄存器进行控制。若使能一个中断,需向 ISER 寄

存器对应位写“1”;而若除能一个中断,则需向 ICER 寄存器对应位写“1”。向 ISER/ICER 寄

存器写“0”无效。

ISER/ICER 是 32 位可读/写访问的寄存器,每一位控制一个中断的使能/除能。寄存器位描

述如表 4.62 所列。LPC178x/177x 系列 Cortex-M3 芯片支持 41 个嵌套中断,则只需用到

ISER0/ICER0 与 ISER1/ICER1 两对寄存器。

由于前 16 个异常编号已经分配给系统异常,故而外设中断的起始异常编号是 16。

操作示例

对定时器 0 和外部中断 0 中断进行使能和除能操作。定时器 0 中断 ID TIMER0_IRQn=1,

外部中断 0 中断 ID EINT0_IRQn=18。

NVIC->ISER0 = (1 << ((uint32_t)(TIMER0_IRQn) & 0x1F)); /* 使能 Timer0 中断 */

NVIC->ISER0 = (1 << ((uint32_t)(EINT0_IRQn) & 0x1F)); /* 使能 EINT0 中断 */

NVIC->ICER0 = (1 << ((uint32_t)(TIMER0_IRQn) & 0x1F)); /* 除能 TIMER0 中断 */

NVIC->ICER0 = (1 << ((uint32_t)(EINT0_IRQn) & 0x1F)); /* 除能 EINT0 中断 */中断的挂起与清除

当中断发生时,若有以下一种或多种情况发生,则中断不能立即得到响应,将被挂起。

处理器正在处理高优先级的异常;

处理器正在处理同一优先级的异常;

该中断被屏蔽。

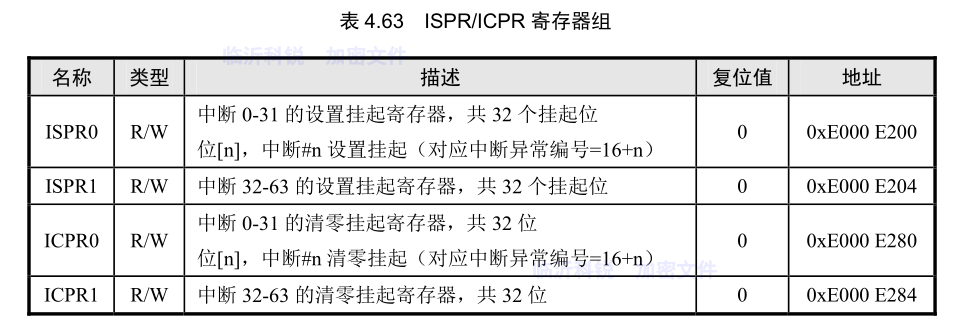

中断的挂起状态可以通过“中断设置挂起寄存器(ISPR)”和“中断挂起清除寄存器(ICPR)”

来访问。

ISPR/ICPR 与 ISER/ICER 寄存器组类似,共有 8 对,见表 4.63 所列。其用法与 ISER/ICER

寄存器完全相同。可通过修改该寄存器来挂起中断或清除一个已挂起的中断。

用户可通过修改 ISPR 寄存器挂起中断,也可通过修改 ICPR 寄存器清除中断的挂起状态。

操作示例

对外部中断 0 和定时器 0 中断进行挂起和清除操作。

NVIC->ISPR0 = (1 << ((uint32_t)(TIMER0_IRQn) & 0x1F)); /* 手动挂起 Timer0 中断 */

NVIC->ISPR0 = (1 << ((uint32_t)(EINT0_IRQn) & 0x1F)); /* 手动挂起 EINT0 中断 */

NVIC->ICPR0 = (1 << ((uint32_t)(TIMER0_IRQn) & 0x1F)); /* 清除 TIMER0 中断挂起状态 */

NVIC->ICPR0 = (1 << ((uint32_t)(EINT0_IRQn) & 0x1F)); /* 清除 EINT0 中断挂起状态 */优先级

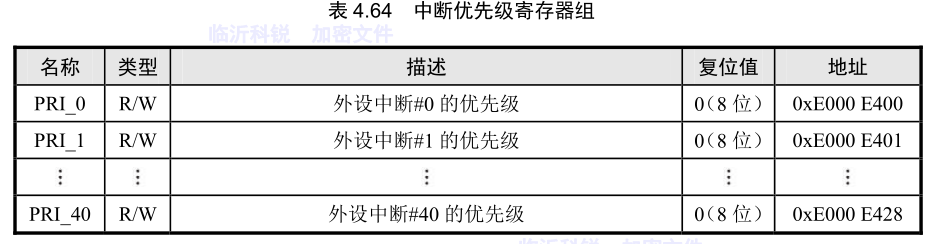

中断优先级寄存器。这些寄存器可分配每一个中断的优先级,并包含中断的优先级字段。

操作示例

对优先级进行分组,设置外部中断 0的优先级。

SCB->AIRCR = (0x05FA) | (0x05 << 8) ; /* 优先级在位 5 处分组 */

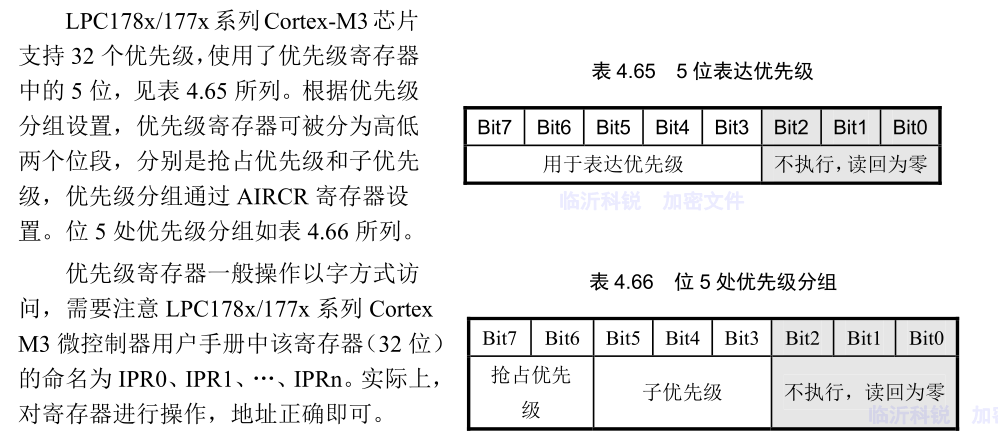

NVIC->IPR4 = ( 0x01<< 3) << 16 ; /* 外部中断 0 的优先级寄存器位于 IPR4[23:16] 字段 */LPC178x/177x 系列 Cortex-M3 芯片支持 41 个向量中断,IPR0~IPR10 为有效寄存器。

活动状态

每个外部中断对应在活动状态寄存器(IABR)都有一个状态位。处理器开始执行中断服务

例程,中断相关的活动位就被置“1”,中断退出该活动位被清“0”。若当前中断在执行服务例

程期间被高优先级的中断抢占,其活动状态也依然为“1”。

IABR 寄存器组描述如表 4.67 所列。IABR 寄存器为 32 位只读寄存器。LPC178x/177x 系列

Cortex-M3 芯片支持 41 个向量中断,IABR0~IABR1 为有效寄存器。

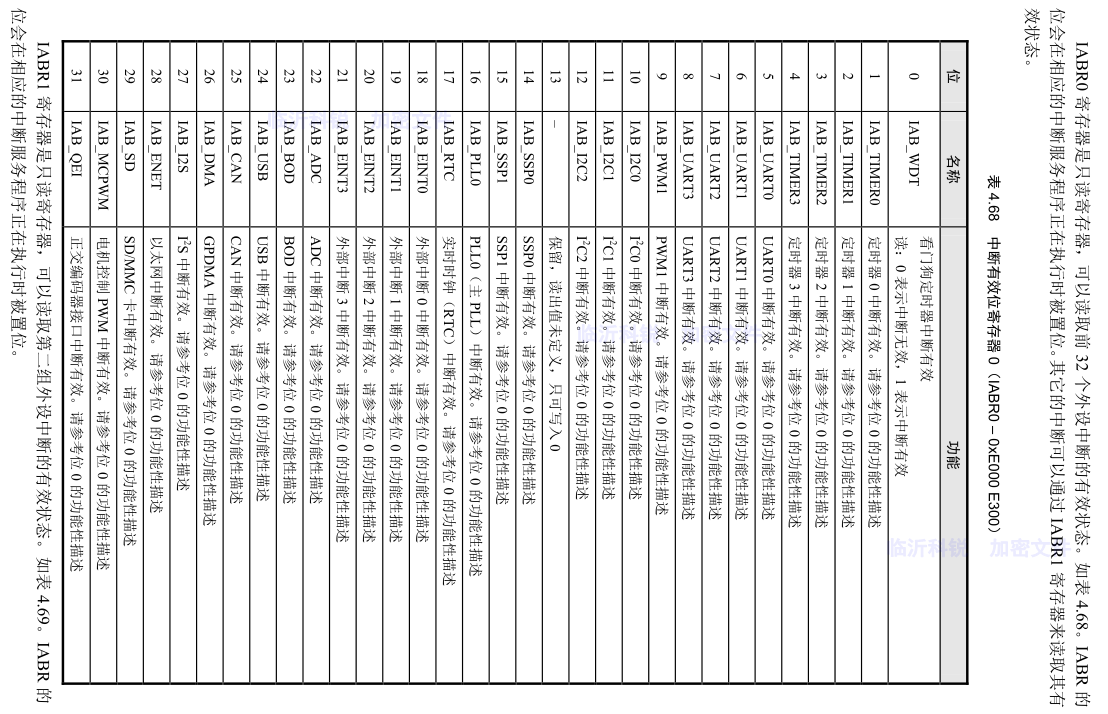

IABR0 寄存器是只读寄存器,可以读取前 32 个外设中断的有效状态。如表 4.68。IABR 的

位会在相应的中断服务程序正在执行时被置位。其它的中断可以通过 IABR1 寄存器来读取其有

效状态。

中断处理

中断建立完整过程如下:

① 系统启动后,设置优先级分组寄存器。缺省情况下分组位为 0,即 7 位抢占优先级、1

位子优先级。

② 如果需要重定位向量表,需要先将硬 fault 和 NMI 服务例程的入口地址写到新表项所在

的地址中。

③ 如果需要重定位向量表,配置向量表偏移量寄存器,使之指向新的向量表。

④ 建立中断向量,即从向量表中取出对应服务程序的入口地址。由于向量表可能进行重定

位,建议先读取向量表偏移量寄存器的值,再根据该中断在表中的位置,计算出服务例程入口

地址。若一直使用 ROM 中的向量表,则无需此步骤。

⑤ 为该中断设置优先级。

⑥ 使能中断。

如果将应用代码存储在 ROM 中,并且不需要修改异常服务程序,可将整个异常向量表存

储在 ROM 的起始区域(0x0000 0000)。在此情况下,向量表的地址偏移量一直为零,并且向

量表已经存在 ROM 中。此时,中断建立的过程可大大简化,只需三步:

① 系统启动后进行优先级分组。

② 设定中断优先级。

③ 使能中断。

由于优先级分组不当会产生不可预知的后果。一般情况下,建议使用默认分组即可,此时

中断建立仅需两步,如图 4.27 所示。其中阴影部分是需户进行软件设置,在软件设置完毕后,

一旦有中断请求信号,Cortex-M3 处理器硬件将自动响应,开始执行入栈、取向量、运行中断

服务函数以及中断退出等操作。