赛灵思PLL的重配置_S6

PLL的重新配置就是可以随时更改输出时钟的频率,而不用重新在编译,生成比特流文件,再下载到对应的器件中去,本文主要介绍PLL的重配置的一些背景,基础知识,后续的文章来分析一下官方提供的相关文件怎么应用到我们的工程中。

撰写本文的目的:由于项目中用到了这部分的知识,但是网上百度了很多,依然没有自己想要的,故只能去官方网站寻求帮助,现将自己总结的东西贴出来,供大家下次参考,转贴请注明出处,谢谢。首先提供历程以及说明文档的下载连接,引用官方。

PLL基础知识介绍

----------参考Xilinx官方的文档,在此表示感谢

/*******************************************************2017年5月8日 第一次撰写 *****************************************/

一. 概述:Spatan-6 系列设备的时钟管理单元(CMT)包括两个DCM和一个PLL,它有一个很强大的功能是可以动态的配置相位、周期和可分频时钟的数值,该应用笔记详细描述了重新配置PLL的必要点,而且提供相关的参考设计可用于用户的工程中。在参考设计中,我们有意的使用CLKFBOUT作为反馈路径,不支持CLKOUT作为反馈路径。PLL的配置分为4个组,分别是分频/倍频组,相移组,锁存组,过滤组。接下来就省略啦,这些都是翻译官方的参考文档的,最后自己取阅读一遍。

二.

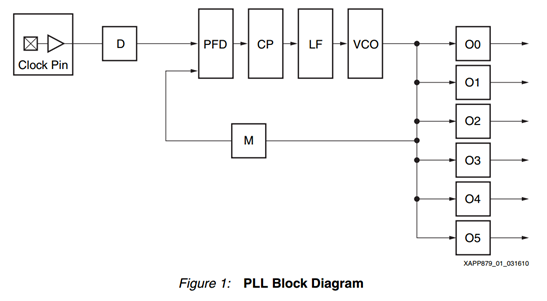

PLL的重新配置主要是通过PLL_DRP完成的,如下图所示:

上图是PLL的框图,这里我简单的介绍一下,输入的时钟经过D(可编程计数器实现倍频或者分频),PFD(相位偏移需要),CP(驱动电荷泵,我也不知道干嘛的。。。),LF(环路滤波器),VCO(电压控制振荡器),和一个专用的计数器M(此计数器控制PLL的反馈时钟,以实现大范围频率合成),最后生成6路时钟,每一路需要单独配置,图中只画了一个。

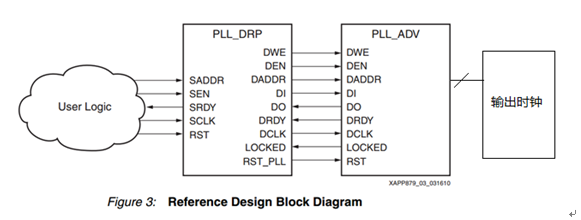

接下来是配置PLL的模块划分图,大概分成如下这几部分:

上图是PLL配置的系统框图,实际应用中,user logic即是用户逻辑,可认为是顶层文件,然后控制和PLL_DRP的这几个接口既可以配置PLL了,PLL_ADV 和 PLL_DRP的另一侧相连,以实现对PLL的配置,输出的时钟是一系列的时钟信号,也就是我们的需要的时钟了。官方提供的例程中,有两组配置时钟供我们测试。下面说明一下用户侧的几个信号:SEN(状态使能信号,一个clk),在时钟检测到SEN有效使,同时检测SADDR的值,然后进行状态1或者2的配置,SCLK和RST就不解释了,不过官方提供的参考设计中,对时钟信号采用了原语进行描述。

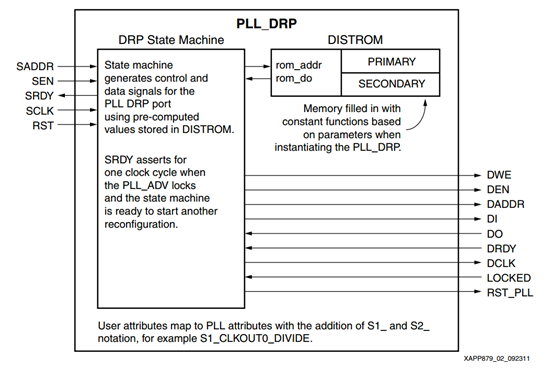

接下来看看PLL_DRP,对与我们用户来说,可以不关注PLL_ADV这个端口,我们主要关注PLL_DRP这个端口怎么操作PLL_ADV即可,框图如下所示:

上图是官方的插图,其实这这个模块主要包含一个状态机和ROM,状态机用来配置PLL_ADV,而ROM中存放我们的计算好的数据以重新配置PLL,这是官方参考设计中的结构,要配置的话只要把rom对应的地址值取出来即可。

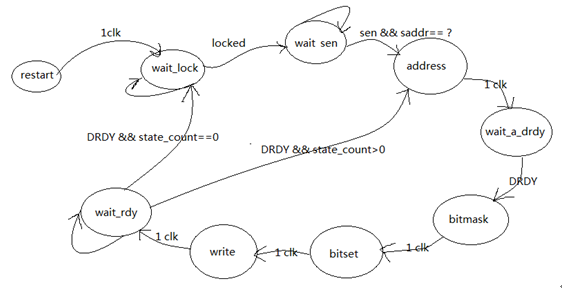

接下来我们对PLL_DRP中的状态机进行分析,这里我直接贴出来自己画的状态转移图,仅供参考:

简单说明:上电初始化时,会自动的等待一个locked,接着在wait_sen的状态等待SEN,并在判断SEN有效时,SADDR的值是多少,然后进行判断,选择读取rom的地址是从多少开始,,然后配置相关的寄存器,总共有23个寄存器(见附录),配置完23个寄存器之后,等待锁存locked信号有效时(高有效),就代表配置已经ok了。

需要工程文件请向博主索要,如果有什么疑问,欢迎大家讨论,转贴请注明出处,谢谢。

---------cofin_add