最近在调试这个读的过程,现将调试过程中的问题记录一下。

1.测试目标:通过NIOS直接操作内存,然后在verilog中读取数据流,保证读取和写的一致。

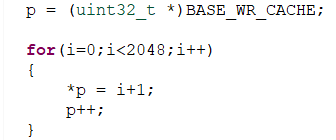

通过上述c程序对内存赋值,然后通过该IP读取内存中的数据,假设从内存的一半开始读取,这里为了方便计算以及对比,我将数据从1开始赋值。

地址定义如下:

在NIOS中,需要将最高位置1,从而避免访问cache,二来需要注意的是,操作时地址是:内存的大小/2 + 内存分配的基地址。

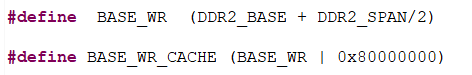

2.在qsys中调用该IP,然后顶层例化如下:

这里我用的1G bit的ddr2,相当于128M * 8bit,所以地址是64M起始,即地址 = 67108864,这里通过该IP访问内存时,并不像NIOS中,需要加基地址。

其次由于不是burst传输的,因此control_fixed_location 设置为0;下面的control_read_length设置为(实际自己设置):4096*2 = 8192 BYTE,而数据线宽度我设置的是32Bit,也就是4字节,因此8192/4 = 2048(words),十六进制0x800,因此读取2048次即可。

3.signal tap 波形分析:

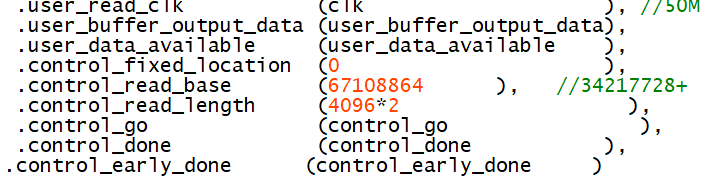

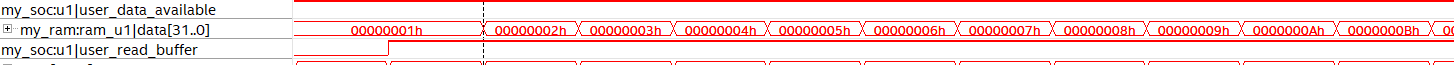

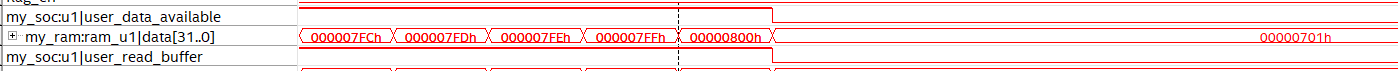

由于之前分析过,输出是在user_read_buffer有效时,且在next clk才输出数据,因此我这里在user发出control_go信号之后,人为的产生一个clk的user_read_buffer信号,这样我之后操作vld和data就对齐了。如下图所示,之后user_read_buffer和data是对齐的:

接下来看下最后一个数据读出,下图中最后一个数字是0x800,对应10进制2048,每次读取4字节,因此和我们在参数例化时设置的一致:

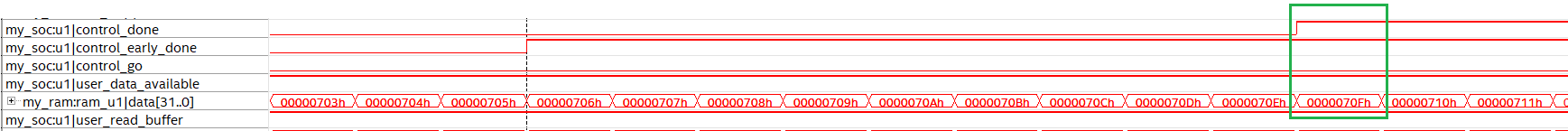

4.control_done 和 early_done 信号分析

如上图所示,当数据为0x70F时,control_done为1,上次分析该信号是指示最后一个数据的,但是我没有发现在0x800出现,二十在0x70f出现的,而fifo的深度我设置的是256,故我猜测该信号是表示最后一个数据已经写入到FIFO中,然后该信号拉高(感觉不好用),control_early_done超前control_done,在此不做分析。

5.总结

该ip可以从Avalon MM Slave中读取一定长度的数据,然后通过流的方式输出,这在流处理过程中会有很大的应用,比如通过NIOS配置ccd/cmos传感器,之后通过相应的接口将数据写入到缓存中(可用Avalon-MM Master Templates-Write,下次分析),之后再通过读端口将数据读出,这样会大大的简化user 的操作,且user可以把输出的数据进行打包,若加上sop和eop等信号,则可以直接传送到千兆网模块,当然还需要计算数据流的大小。

除了上述的应用,还可以共享内存做图像显示,在NIOS中给内存赋值,然后读取内存中的数据到相应的显示设备显示即可,我想如果加上GUI会更加强大,且省成本,该方案可作为一种廉价的嵌入式解决方案。