https://zhuanlan.zhihu.com/p/86698219

FPGA(Field Programmable Gate Array)是在PAL、GAL等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

FPGA由于其可编程特性,可以被用于实现任意的逻辑功能,FPGA的每一个时钟周期可以并行处理多个指令。由于FPGA可以被设计为专门处理某个(或某些)算法,所以即使其支持的时钟频率低于CPU,但单个时钟周期可以完成的运算可以远大于一个CPU指令可以完成的运算量,甚至整个算法都可能在几个时钟周期之内完成,所以完成整个算法FPGA所需的时钟周期数可以远低于CPU。

在证券交易领域,行情数据瞬息万变,盈利的机会转瞬即逝,拥有更低的时延、更快的响应,意味着能精准把握买卖机会和点位。现场可编程门阵列(“FPGA”)技术与传统软件系统相比,能实现可预知的超低时延,该技术已在模型计算、高频交易等领域大放异彩。

本文主要介绍如何基于FPGA技术实现沪深行情硬件加速,涵盖了系统的设计及实现、系统的实测效果及系统预留的强大扩展性等内容,希望能有助于国内证券行业对FPGA技术的研究和应用,为开发者提供简单的相关技术参考。

一、概述

1.1 低交易时延的挑战

在证券交易领域,盈利的机会转瞬即逝,“更低交易延迟”是所有金融交易追求的核心目标之一。目前国内金融行业的交易系统大部分基于传统通用CPU架构,交易提速存在瓶颈,满足不了超低时延的交易需求。而随着 FinTech(金融科技)的发展,各种算法交易、量化交易兴起,金融行业追求更低交易延迟时间的“竞赛”不断升级,成为各大金融机构的核心挑战之一。尤其是近年来程序化交易在资本市场的全面应用,传统的软件技术或以软件为核心的加速技术难以满足微秒级的实时处理和实时响应的要求。业内均在寻求搭建低时延交易系统的解决方案,基于GPU、FPGA硬件并行加速的技术逐渐进入证券交易领域,成为金融科技领域新的趋势,是华尔街的主流技术之一。

降低交易延迟简单来说就是如何实现金融数据加速。FPGA具有硬件可编程、低功耗、低时延的特性。基于RTL(Register Transfer Level:寄存器传输级)级的逻辑编程,可定制化各类通讯协议(如TCP/IP协议栈卸载)、各种消息编解码(如上交所的FAST协议解码)及系统各种颗粒度的操作,实现数据的并行和流水的并行,达到极低的系统时延和极高的系统容量。

1.2FPGA技术在沪深行情系统的应用

近年来,随着国内金融市场的快速发展和规模不断扩大,业内信息系统往高性能、高可靠、高容量、低时延的方向发展。众多金融技术公司,相继推出基于FPGA的产品,尤其在期货行业,使用FPGA开展各类应用的开发,如行情、交易、风控等领域,已经取得了许多成果,为FPGA在证券行业的应用开发提供参考。

架构的选型

FPGA架构近年来历经Net-FPGA、OpenCL+RTL异构、RTL+软件异构等,目前基于金融商用系统的稳定性、系统可扩展性、健壮性的充分考虑,选定RTL+软件的异构架构。

为何选择FPGA技术落地行情加速

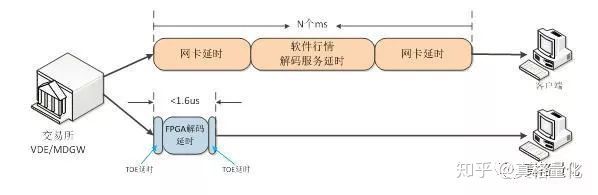

通过对沪深行情从交易所前置机VDE/MDGW至行情应用客户端的时延路径进行分析(见下图),当前业内大多数厂商采用软件进行行情解码,提供行情服务。

这些行情解码服务时延明显,可能超过10毫秒,且行情解码软件数据处理能力有限,牛市行情压力下,实时性难以得到保证。而通过FPGA技术对沪深Level-2行情加速解码,可以最终实现低至纳秒级的沪市STEP-FAST解码引擎,在理想测试环境下端到端的处理时延降低到数十微秒(含网络时延)级别,得到明显的提速效果。

二、FPGA技术在沪深行情加速的设计与实现

2.1 基于FPGA的异构架构设计

根据业务及扩展需求,对基础硬件选型指导如下:

(1)10GE万兆以太网接口,行情源、TCP行情推送、组播行情推送采用独立的接口。

(2)可定制化的TOE IP,支持TCP、UDP、IGMP、ICMP、ARP、RARP全卸载,且TCP连接数支持至少32个。

(3)PCIe Gen3X8,且兼容Gen1/2/3。

(4)至少两个Bank DDR,内存容量不少于8GB。

(5)至少两个Bank QDR。

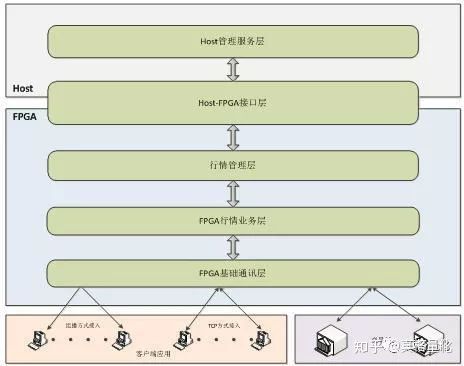

传统TCP /IP 协议是基于CPU( Central Processing Unit,中央处理器) 软件实现的,而使用CPU 进行TCP /IP 协议栈处理,存在能力不强、效率不高的缺点,占用大量的CPU资源,浪费存储空间及产生大量功耗,使其性价比很低,影响性能,万兆以太网的的带宽资源得不到充分的利用。故所选的板卡使用万兆以太网口作为其信息传输接口,支持TCP /IP 协议栈的TOE IP是关键之一。通过FPGA 来实现TCP /IP 协议栈以及以太网MAC 控制器,将原本属于主CPU 的这部分工作由额外的硬件电路完成,减轻CPU 的负担,加速网络处理的能力,提升系统的性能。系统的可扩展性是系统设计的重点之一。由下往上分为五个逻辑层次,包括FPGA基础通信层、FPGA行情业务层、行情管理层、Host-FPGA接口层和Host管理服务层,层次之间设计开发边界明确,上层依赖下层模块,调用下层或同层模块的接口,上下层之间功能充分解耦,如下图示。

其中FPGA基础通信实现独立的通信功能,提供清晰的功能边界和明确的开发接口。在Host侧与FPGA侧可通过C++方式的API进行直接调用。

2.2 Level-2行情解码引擎

上海证券交易所信息网络公司(简称“上交所”)于2016年建设新一代的低时延行情发布系统LDDS,支持多种信源,具有低时延、大流量、易扩展、高可用等特点,系统在较优的网络环境中平均时延小于1ms。该Level-2行情系统是基于FAST技术标准、面向专业投资者的新一代实时行情发布系统。与传统的基本行情相比,Level-2行情更加实时,包含更多的价位深度、逐笔成交、订单等内容和其他有价值的信息。下面以上交所的Level-2行情为例,阐述行情解码引擎的实现。

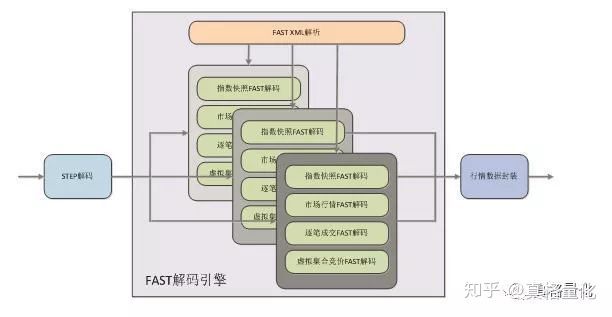

上交所的LDDS以国际标准的金融信息交换协议(FIX/FAST)为基础,结合中国标准的证券交易数据交换协议(STEP)的特点确定数据传输协议,根据我国证券市场数据的特点以及Level-2行情内容的特性设计在证券市场数据领域具有独创性的算法。FAST协议在保持FIX协议灵活性的基础上,将市场数据大幅度压缩,大大提高了处理速度。FAST系统大幅减少Level-2行情所需的传输带宽(不到原来的25%)和发布系统的负荷(减少到原来的10%)

鉴于上交所FAST协议的复杂性,同时根据RTL的特性,设计出一套并行、全流水式的高效STEP-FAST解码引擎方案,如下图所示,不同行情类型解码并行处理,根据实际应用增加引擎数量,达到更高的数据解码吞吐率。同时做到FAST的XML模板可配,以应对交易所的变更。

— — — — — — E N D — — — — — —

真格量化可访问: