自建AXI4的IP核的地址问题

1、问题概述

在AXI4中,对应的操作通过对对应的寄存器设置来完成。其中的寄存器又分为数据寄存器和地址寄存器。其中,如果只是想要操作数据的话,只需要使用数据寄存器即可。在自建AXI4的IP时,会选择数据寄存器的个数。在打开封装文件时也可以看到数据寄存器。一般是slv_reg0·····等编号。其中slv代表从机,reg0代表寄存器0.这里有一个如何操作寄存器的问题。

2、问题解决

可以看出,这个数据寄存器既可以接收AXI的数据,也可以发送数据到AXI上。这里的功能十分类似一个三态门。只不过这里的控制信号也是一个可控寄存器的输出。主机通过设置配置寄存器决定输入还是输出,通过地址读取或者写入数据。严格来说,如果要使用这个寄存器的作为输入输出口,是需要和控制信号也就是配置寄存器的状态关联的。比如,作为接收主机数据时的输入寄存器,该寄存器作为正常的输入口,可以直接输出到所需的PL模块。当作为发送数据到主机的输出口,则需要接受来自PL模块的信号。显然,这里是有矛盾的。一个寄存器不可能同时有两个输入和输出。所以,虽然AXI总线是可以设置从机的通信模式:接收或者发送,但是,在设计时,具体到某个数据寄存器时,只能作为输入或者输出,不可更改。作为向主机输入的输出寄存器,甚至可以直接采用wire型变量,实时等待发送。而作为向主机接收数据的输入寄存器,只需要用reg向其他变量赋值即可将数据导出到PL。显然,发送到主机是比较困难的,需要等待主机的读取。主机是可以对每个特定的寄存器设置输入输出模式的。所以在PS端需要提前设置模式以便寄存器正确的工作。当然,如果一定要实现某个寄存器的输入输出灵活转换,则可以牺牲另外一个寄存器用于配置PL的寄存器。如果对AXI总线的信号比较熟悉的话,也可以直接读取对应的从地址进行判断,这就是需要更加复杂的结构。现在暂时不涉及。

3、问题总结

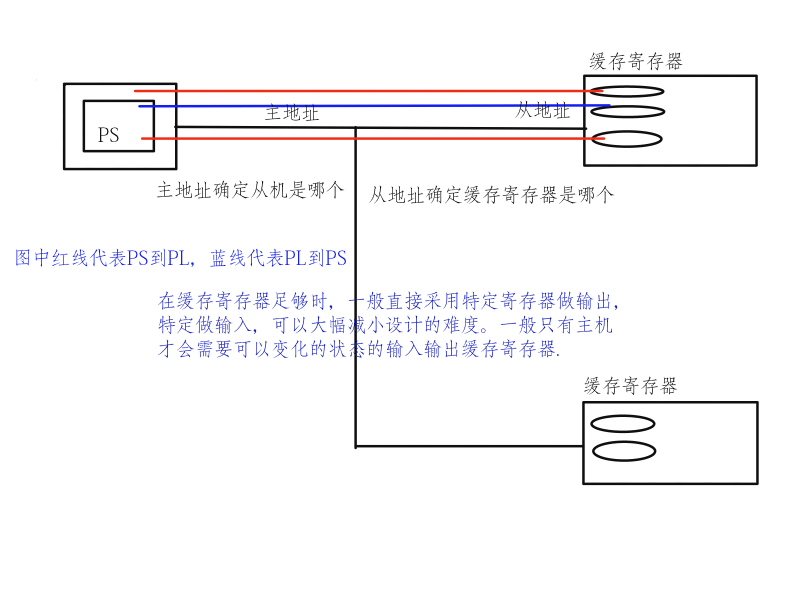

这里主要通过对主地址和从地址的对应的物理信号出发,分析所需要的数据操作。下面给出一个AXI数据传输的关系图。

这只是用于理解PS端设计时的示意图。如果想要完全理解AXI的从机逻辑,必须要五个通道和辅助的模块出发。后面会逐渐涉及数据的读写、地址的读写、响应信号的构建、优先级判断、数据缓存等各种细节的问题。