本文由远航路上ing 原创,转载请标明出处。

这节笔记记录IP核的生成以及参数设置。

先再IP库里下载安装Framebuffer 的ipcore 并安装完毕。

一、IP核的生成:

1、先点击IP核则右边会出现生成对话框:

按箭头指示顺序进行设置:要设置生成ip核的路径(可以新建一个文件夹ipcore来放置IP核,若有多个IP核则在ipcore下分别建立文件夹),IP核的名字,以及语言的类型:verilog或VHDL。最后点击Customize.

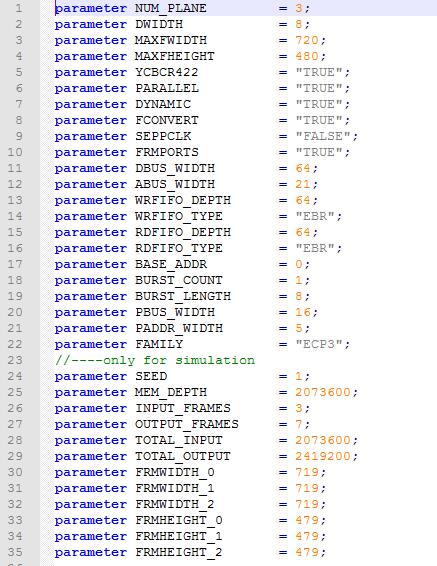

2、 在上一步设置之后会出现下面的设置界面,先设置输入视频格式,有三种:YCbCr422,YCbCr444 or RGB ,单信号。在动态参数更新未被选择时(静态模式),输入视频帧的高度与宽度是固定的,在方框内直接填入,注意范围为64--4096,不过建议大于64,否则可能无视频被采集到。在选择动态模式时,此处填写的数据为最大的高度与宽度,实际的高度与宽度要以参数设置为准。

选择Parallel processing 之后,则数据会是并行数据;16bit,否则为串行数据:8bit。

选择Frame rate conversion之后,启动帧率转换,会加入一个输入端口OCLK,否则就会就会按输入信号时钟输出。

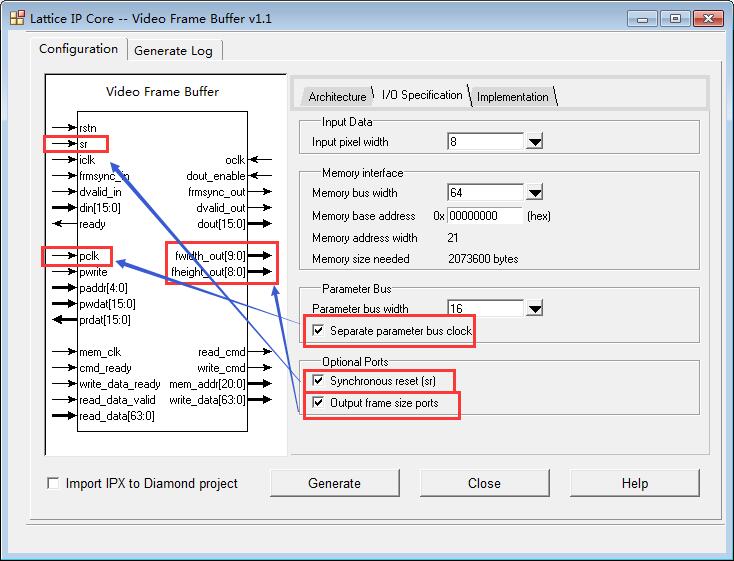

在选择了动态配置的情况下,界面如下:

帧率的高度和宽度设置变为了最大分辨率设置。同时左侧会多出设置参数的信号。时序图见datasheet.

对于宽度和高度设置的寄存器的地址为:

在动态设置的时候,每个寄存器的size为32,则占用4个字节,所以设置的时候可以两个字节分开设置,比如设置FRMWIDTH时,地址为0x00时设置低2字节,0x02时设置高2字节。设置帧高度和宽度的数据为实际数据-1.比如分辨率大小为1920*1080,则送人的数据应为1919*1079.

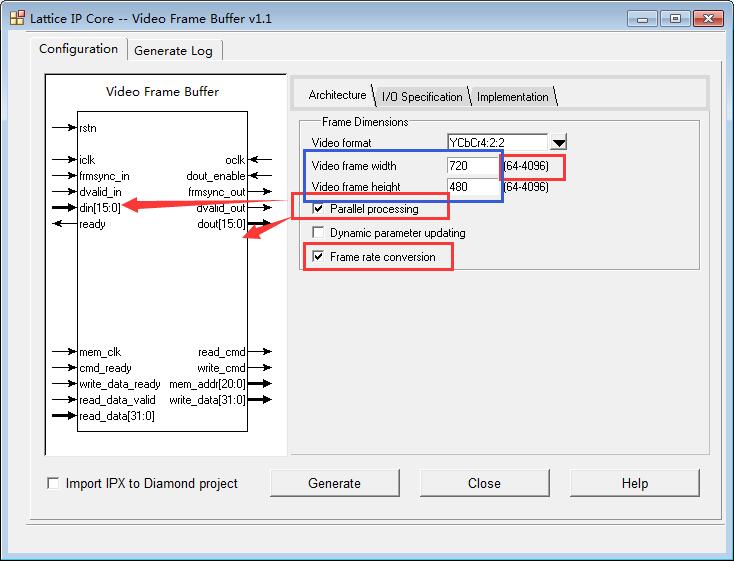

3、先设置像素的宽度(8/9/10)。

再设置存储总线宽度,这个与DDR的数据总线宽度一致,(一般framebuffer ip核接DDR的ip核,所以与ddr ip核的数据总线宽度一致)。

parameter bus width 的宽度可以为8/16/32bit,根据最大分辨率的位数来选择参数总线的宽度。

选择分离参数时钟,则会多出一个pclk的时钟输入端口,根据pclk的时钟来设置参数;若不选此项,则根据输入时钟来设置时钟参数。

选择同步复位选项,则多出一个同步复位的端口。

output frame size ports 端口,选择此项则会多出两个端口来表示输出帧的长度和宽度,这两个参数在frmsync_out有效的时候才会更新。

4、设置FIFO的类型,有两种,

设置FIFO的深度,则FIFO所存储的总的数据为:depth*bus width==64(depth)*64(bus width) = 64*4*16(ddr芯片的数据位宽) = 256*16个16bit的数据,

则在数据存储量到总存储量的一半的时候出发DDR的写操作,则一次写入的数据为128*16bit的数据,则Framebuffer IP会向DDR 的IP送出32个64bit(bus width)的数据。

设置DDR 存储的突发长度和命令突发计数。此两处的值要与DDR的设置相配合才可以。(详细配合后面再说)

最后点击Generate 则等一段时间就可以生成了。

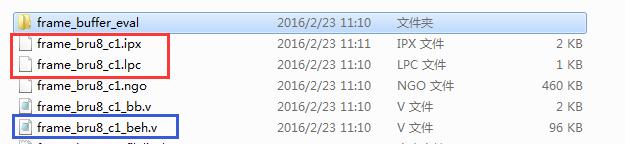

在生成之后,文件夹内会生成一些文件:

其中红线内部的两个文件可以作为综合的文件加入工程(两者其一即可),蓝线内的文件可以作为前仿真文件加入工程。

而顶层文件和参数文件在frame_buffer_eval文件夹内部。

打开frame_buffer_eval文件夹,出现两个文件夹,testbench文件夹内部是前仿真的外部辅助文件,在仿真时要把这两个文件加入到工程内,并选择为只仿真。

frame_bru8_c1文件夹内部存放着顶层文件,参数文件和modelsim仿真的.do文件。

上图所示,sim文件夹内部是仿真的.do文件,而src文件夹内部是顶层文件(rtl)和参数文件(params)。

将此文件加入工程,作为顶层文件。

在params文件夹内找到params.v文件,这是参数文件,但是本工程不需要也不用添加。

打开params.v文件可以看到内部的参数都是IP核生成时所设置的参数。