第3章 存储器

本章介绍了TMS320C54x DSP存储器的构成和操作。一般来说,C54x器件共有192K 16位字的存储窨,这个空间分成3个专用的部分:64K字程序、64K字数据和64K字I/O口。在某些C54x器件中,存储器结构已经通过重叠和分页的方法加以改变,这样就增加了存储器空间的容量。

C54x体系结构上的并行特点和片内RAM的双存取能力使C54x可以在任意给定的机器周期内同时进行4个存储器操作:一条指令的读取操作、两个操作数读操作以及一个操作数写操作。

在片内存储器中操作有如下几个优点:

Higher performance because no wait states are required

Lower cost than external memory

Lower power than external memory

The main advantage of operating from off-chip memory is the ability to access a larger memory space.

3.1 存储器空间

C54x DSP的存储器划分成3种独立可选的空间:程序、数据和I/O。这些空间中的RAM、ROM、EPROM、EEPROM或者存储器映射的外设可以位于片内或片外。

程序存储器中包含要执行的指令和执行指令时所需的表,数据存储器空间存储指令所需的数据,I/O存储空间连接外部的存储器映射外设,也可作外部数据存储空间。

按芯片各类的不同,C54x的片内存储器有这样几种类型:双存取RAM(DARAM)、单存取(SARAM)、双向共享RAM和ROM。RAM总是映射到数据空间,但也可以映射到程序空间。ROM可以被激活并映射到程序空间,也可部分映射到数据空间。

在CPU状态寄存器中有3位影响存储器的结构。这3位产生的影响因器件不同而不同。

MP/$overline {MC}$、OVLY和DROM 3位在处理器模式状态寄存器(PMST)中。

3.2 程序存储器

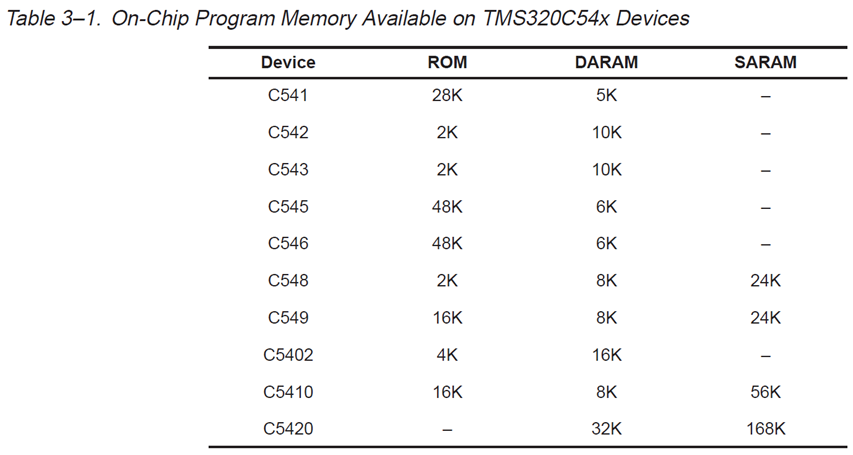

The external program memory on most C54x devices can address up to 64K 16-bit words. The C54x devices have on-chip ROM, dual-access RAM(DARAM), single-access RAM (SARAM), and two-way shared RAM that can be mapped by software into the program-memory space. Table 3–1 shows the on-chip program memory available on the various C54x devices. For devicespecific on-chip program memory configurations, see the device data sheet.

When the memory cells are mapped into program space, the C54x device automatically accesses these memory cells when addresses fall within the boundaries of the on-chip memory. When the program address generation unit(PAGEN) generates an address outside the boundaries of the on-chip memory, the device automatically generates an external access.

3.2.1 程序存储器配置

MP/$overline {MC}$和OVLY位决定了哪些片内存储器在程序空间有效。复位时,MP/$overline {MC}$引脚上所接的逻辑电平被传送到PMST寄存器中的MP/$overline {MC}$位。MP/$overline {MC}$位决定是否使能片内ROM。若MP/$overline {MC}$=1,器件被构造成微处理器(microprocessor),片内ROM被禁止。若MP/$overline {MC}$=0,器件被构造成微处理机(microcomputer),片内ROM被使能。MP/$overline {MC}$引脚只在复位时才被采样,但是用户可以通过软件设置或清除PMST寄存器的MP/$overline {MC}$位以使能或禁止片内ROM。

3.2.2 片内ROM组织

片内ROM被划分成块,并以块来组织,以提高性能。例如,块的组织形式可使用户从ROM的某一块记取一条指令,同时又不影响对另一个ROM块的数据访问。

3.2.3 程序存储器地址映射和片内ROM内容

在器件复位时,复位、中断和陷阱向量被映射到程序空间从地址FF80h开始的页(128个字)中。但是,这些向量在器件复位以后可以重新映射到程序存储器任意页(128个字)的开始处。这个特点可以很方便地把向量表从引导ROM中移出,而且把ROM从存储器映射中移走。

注意:在片内ROM中,128个字被保留用作器件测试。要在片内ROM中实现的应用程序代码不能占用程序空间FF00h~FF7Fh的128个字。

3.2.4 片内ROM代码内容和映射

具有片内引导装载ROM的C54x器件,根据不同的器件,F800h~FFFFh的2K字可能包括以下一项或多项内容:

A bootloader program that boots from the serial ports, external memory, an I/O port, or the host port interface (if present)

A 256-word u-law expansion table

A 256-word A-law expansion table

A 256-word sine look-up table

An interrupt vector table

3.2.5 扩展程序存储器

C548、C549、C5402、C5410和C5420的程序存储器空间采用了分页扩展存储器的方法,这样允许访问多达8192字的程序存储器空间。为了实现这种扩展的方法,C548、C549、C5402、C5410和C5420增加了以下特性:

23 address lines, instead of 16 (20 address lines in the C5402, and 18 in the C5420)

An extra memory-mapped register, the program counter extension register (XPC)

Six extra instructions for addressing extended program space

XPC是存储器映射寄存器,映射到数据空间的001E地址,它的值决定页号。在硬件复位时,XPC被初始设置为0。

C548、C549、C5402、C5410和C5420的程序存储器被设置为128页(C5402是16页,C5420是4页),每一页为64K字。

当片内RAM映射到程序空间时(OVLY=1),程序存储器的每一页由两部分组成:最多32K字的公共块和32K字的私有块。公共块被所有的页共享,私有块只能通过它所在的页来访问。

如果片内ROM被使能(即MP/$overline {MC}=0$,那么它只能放在0页上,而不能映射到程序存储器其它页上。

为了方便用软件对页进行切换,C548、C549、C5402、C5410和C5420有6条影响XPC的专用指令。

FB – Far branch (with or without delay)

FBACC – Far branch to the location specified by the value in accumulator A or accumulator B (with or without delay)

FCALA – Far call to the location specified by the value in accumulator A or accumulator B (with or without delay)

FCALL – Far call (with or without delay)

FRET – Far return (with or without delay)

FRETE – Far return with interrupts enabled (with or without delay)

3.3 数据存储器

C54x中的数据存储器最多包含64$ imes$16位字。除了双存取RAM(DARAM)和单存取RAM(SARAM)以外,C54x器件片内ROM也以用软件映射成数据ROM(DROM)。当访问地址属于片内存储器时,就可以进行RAM或数据ROM(在其有效的情况下)的访问。当数据地址产生逻辑(DAGEN)产生一个超出片内存储器范围的地址时,器件自动产生一个外部访问。

3.3.1 数据存储器配置

数据存储器可以在片内或片外。片内DARAM被映射到数据存储器空间。对某些C54x器件而言,用户可以通过置PMST寄存器中的DROM位将部分片内ROM映射到数据空间。这一部分片内ROM既可以映射到数据空间(用DROM位),又可以映射到程序空间(用MP/$overline {MC}$位)。这种情况下,指令可以把ROM作为数据空间的数据ROM来使用。复位时,处理器将DROM位清零。

当使用单向数据存储器操作数寻址时,那么指纹在单周期内读出ROM数据,包括带有32位长字节操作数的指令。在双向存储器操作数寻址时,如果两个操作数都驻留在相同的块中,那么读取需要2个周期。如果两个操作数驻留在不同的块中,则读取只需1个周期。

3.3.2 片内RAM组织

片内RAM被分成块,并以块为单位来进行组织,以提高性能。所有C54x器件中的DARAM的第一个1K字存储器包含了存储器映射CPU和外设寄存器、32个字的便笺式DARAM和896个字的DARAM。

3.3.3 存储器映射寄存器

64K字数据存储空间包括器件的存储器映射寄存器,它们驻留在数据空间的第0页中(数据地址0000h~007Fh)。数据空间的第0页包括以下内容:

The CPU registers (26 total) are accessible with no wait states.

The peripheral registers are used as control and data registers in peripheral circuits. These registers reside within addresses 0020h–005F and reside on a dedicated peripheral bus structure.

The scratch-pad RAM block (60h–7Fh in data memory) includes 32 words of DARAM for variable storage that helps avoid fragmenting the large RAM block.

3.3.4 CPU存储器映射寄存器

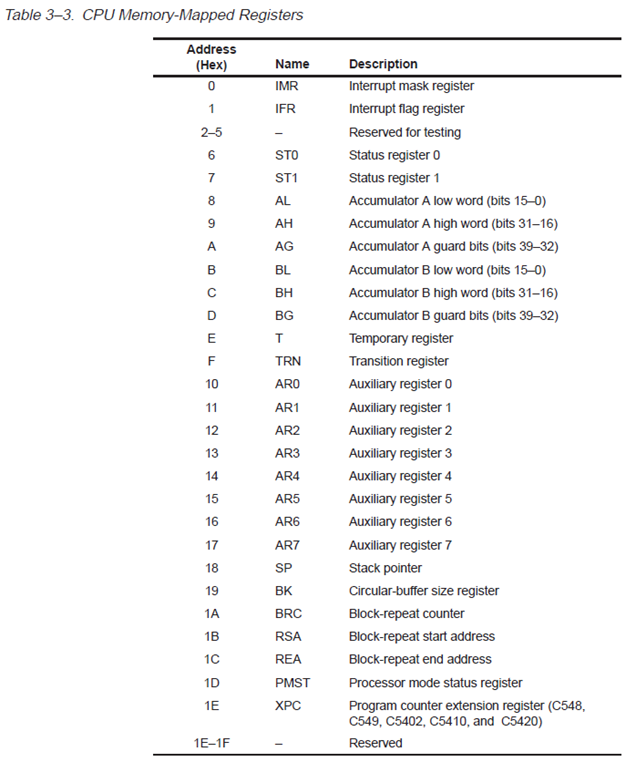

表3-3列出了CPU存储器映射寄存器的清单。本节给出这些寄存器的一个简单总结。

3.3.4.1 中断寄存器(IMR、IFR)

中断屏蔽寄存器(IMR)在需要时可以独立地屏蔽某些中断。中断标志寄存器(IFR)指出当前中断的状态。

3.3.4.2 状态寄存器(ST0、ST1)

状态寄存器ST0和ST1包含C54x器件各种条件和模式的状态。ST0包括算术操作和位操作产生的特别贵标志(OVA、OVB、C和TC),另外ST0还包括DP和ARP字段。ST1反映处理器运行模式和指令状态。

3.3.4.3 累加器(A、B)

C54x器件有两个40位的累加器:累加器A和累加器B。每个累加器都采用存储器映射方式,并且分成累加器低位字(AL、BL)、累加器高位字(AH、BH)和累加器保护位(AG、BG)几部分。

3.3.4.4 暂存寄存器(T)

暂存寄存器T有许多用处,例如,它可存放:

One of the multiplicands for multiply and multiply/accumulate instructions (For more details about the T register and the processes of multiplication

A dynamic (execution-time programmable) shift count for instructions with shift operation such as the ADD, LD, and SUB instructions

A dynamic bit address for the BITT instruction

Branch metrics used by the DADST and DSADT instructions for ACS operation of Viterbi decoding

另外,EXP指令将计算出的指数放入T寄存器,NORM指纹使用T寄存器的值来标准化数据。

3.3.4.5 状态转移寄存器(TRN)

这是用于在Viterbi算法中记录转移路径的寄存器。CMPS指令(比较、选择最大值并存储)在比较累加器高位字和低位字的基础上,修改TRN寄存器内容。

3.3.4.6 辅助寄存器(AR0~AR7)

8个16位的辅助寄存器可以被CPU访问,可以用辅助寄存器算术单元(ARAU)进行修改。辅助寄存器最主要的功能是产生访问数据空间的16位地址,但它们也可以作为通用寄存器或计数器来使用。

3.3.4.7 堆栈指针寄存器(SP)

16位堆栈指针寄存器(SP)存有系统堆栈顶部的地址。SP总是指向最后一个压入堆栈的指令存放地址。堆栈是使用中断、转移、调用、返回和PSHD、PSHM、POPD、POPM指令来进行操作的。在数据压入堆栈之前,SP中的16位值要作递减操作,然后才能将数据压入堆栈。而当数据弹出堆栈之后,SP的值要作增量运算。

3.3.4.8 循环缓冲容量大小寄存器(BK)

循环缓冲容量大小寄存器(BK)是一个16位寄存器。在循环寻址时,辅助寄存器算术单元(ARAU)使用它来说明数据块的容量大小。

3.3.4.9 块重复寄存器(BRC、RSA、REA)

当一个代码段要重复执行时,用16位的块重复计数寄存器(BRC)来指明代码段重复执行的次数。16位的块重复开始地址寄存器(RSA)和16位的块重复结束地址寄存器(REA)分别存放要重复执行的程序存储的首地址和末地址。

3.3.4.10 处理器模式状态寄存器(PMST)

处理器模式状态寄存器(PMST)是一个16位的状态寄存器,它用来控制C54x装置的存储器配置状态。

3.3.4.11 程序计数器扩展寄存器(XPC)

程序计数器扩展寄存器(XPC)是一个包含当前程序存储器地址高7位的寄存器。只有C548/C549/C5402/C5410/C5420几种器件具有程序计数器扩展寄存器(XPC)。

3.4 I/O存储器

C54x器件除了提供程序和数据存储空间之外,还提供I/O存储空间。I/O存储空间有64K字寻址范围(0000h~FFFFh)且只存在于片外,PORTR和PORTW指令可以访问I/O空间。I/O空间的读操作访问时序不财政开支程序和数据存储空间的访问,这样可以使访问独立的I/O映射器件比访问存在器更加方便。

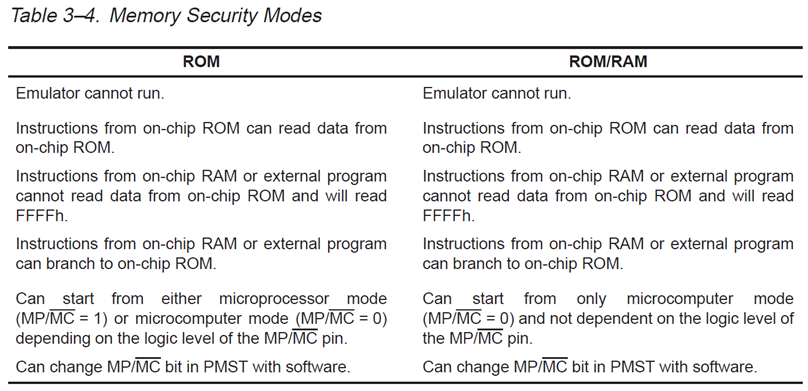

3.5 程序和数据安全保护

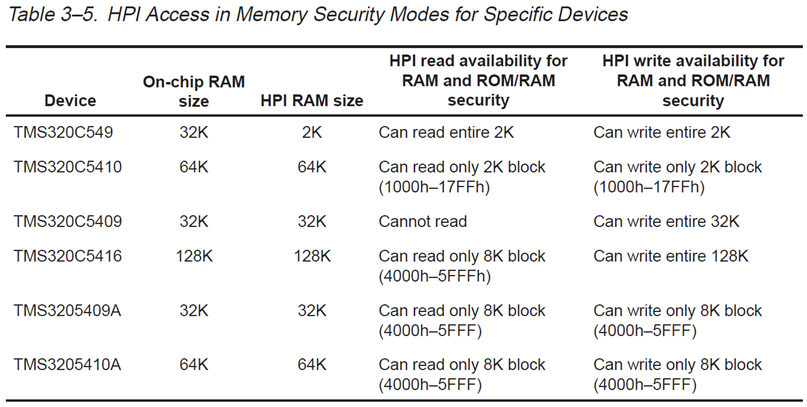

C54x有两级安全选项:片内ROM级别安全选项和片内ROM/RAM级别安全选项。表3-4总结了存储器安全模式的内容,表3-5总结了在使用存储器安全模式时HPI存储器的访问。