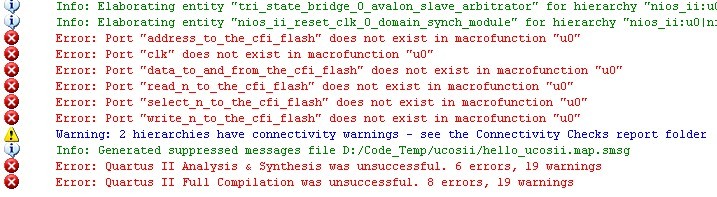

ERROR1:在quartus编译时出现以下错误

定位找到代码中的位置

发现原来是component的名字没有改成和.v文件中的一样,改之即解决。

ERROR2:下面这个错误我也出现了,因为是挂的服务器的license,有段时间不能用,挂上license再编译即解决。为图方便,直接将别人的相同问题转过来

--引用--------------------------------------------------

sbqakqux: 我按照你上面的操作来弄,但在quartus II 7.2中生成的sof文件,并不是hello_ucosii.sof,而是hello_ucosii_time_limited.sof.

请问这是什么问题啊??

先谢谢楼主了!!

--------------------------------------------------------

這表示沒有破解成功

請參考

http://www.cnblogs.com/oomusou/archive/2008/02/03/1063978.html

http://www.cnblogs.com/oomusou/archive/2008/06/25/quartus_ii_72_sp3_crack.html

ERROR3:NIOSII IDE 编译出现

Using cable "USB-Blaster [USB-0]", device 1, instance 0x00

Pausing target processor: not responding.

Resetting and trying again: FAILED

Leaving target processor paused

-重头找问题,重新编译(没有改动),下载,NIOS编译,还是老问题

网上找了找,这个问题遇到的人很多,解决方法也五花八门。

其中参考了萧大的一篇文章: 如何解決Nios II的『Leaving target processor paused』的錯誤訊息?

也不行

解决方法:第二天早上又重头编译,居然一切正常了。原来要把NIOS,QUARTUS都关了再开,重新下载,编译。

Abstract

之前我已經討論這個主題,不過現在看起來,當時的一些設計仍有改進的空間,所以打算重新加以優化。

Introduction

使用環境:Quartus II 7.2 SP3 + Nios II EDS 7.2 SP3 + DE2(Cyclone II EP2C35F627C6)

在(原創) 如何自己用SOPC Builder建立一個能在DE2上跑μC/OS-II的Nios II系統? (IC Design) (DE2) (Quartus II) (Nios II) (SOPC Builder) (μC/OS-II)中,我已經討論過這個題目,經網友FJL提醒,才發現當初的設計雖然可行,不過仍有些缺點:

1.明明只用到SRAM,卻還加上Tristate Bridge與CFI Flash。

2.由於當時功力有限,一些解釋也欠缺完整。

所以決定重新打造一個更精簡的Nios II。若你是Nios II與SOPC Builder的初學者,建議你先依照(原創) 如何自己用SOPC Builder建立一個能在DE2上跑μC/OS-II的Nios II系統? (IC Design) (DE2) (Quartus II) (Nios II) (SOPC Builder) (μC/OS-II)的方式一步一步的建立Nios II,本文僅介紹與前文不同之處。

Step 1:

加入所需的ip

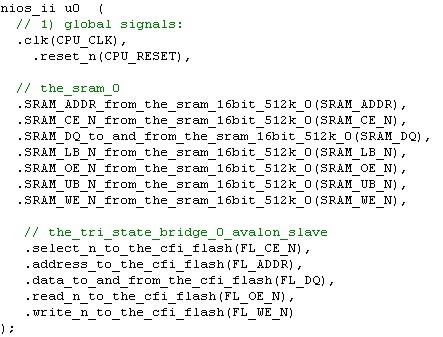

與(原創) 如何自己用SOPC Builder建立一個能在DE2上跑μC/OS-II的Nios II系統? (IC Design) (DE2) (Quartus II) (Nios II) (SOPC Builder) (μC/OS-II)比較,因為實際上只用到SRAM,所以只要加入SRAM即可,並不需要Tristate Bridge與CFI Flash。

由於Nios II只使用到100MHz的clock,並不需要另外加上50MHz clock。

Step 2:

設定Nios II CPU的Reset Vector與Exception Vector

由於現在只有SRAM,所以將Reset Vector與Exception Vector全部設在SRAM。

Step 3:

更精簡的top module

DE2_NIOS_Lite.v / Verilog

2 (C) OOMusou 2008 http://oomusou.cnblogs.com

3

4 Filename : DE2_NIOS_Lite.v

5 Compiler : Quartus II 7.2 SP3 + ModelSim-Altera 6.1g

6 Description : DE2_NIOS lite version for SRAM only

7 Release : 08/29/2008 1.0

8 */

9 module DE2_NIOS_Lite (

10 input CLOCK_50, // On Board 50 MHz

11 input [3:0] KEY, // Pushbutton[3:0]

12 inout [15:0] SRAM_DQ, // SRAM Data bus 16 Bits

13 output [17:0] SRAM_ADDR, // SRAM Address bus 18 Bits

14 output SRAM_UB_N, // SRAM Low-byte Data Mask

15 output SRAM_LB_N, // SRAM High-byte Data Mask

16 output SRAM_WE_N, // SRAM Write Enable

17 output SRAM_CE_N, // SRAM Chip Enable

18 output SRAM_OE_N // SRAM Output Enable

19 );

20

21 wire CPU_CLK;

22 wire CPU_RESET;

23

24 Reset_Delay u0 (

25 .iRST(KEY[0]),

26 .iCLK(CLOCK_50),

27 .oRESET(CPU_RESET)

28 );

29

30 SDRAM_PLL u1 (

31 .inclk0(CLOCK_50),

32 .c1(CPU_CLK)

33 );

34

35 nios_ii u2 (

36 .clk(CPU_CLK),

37 .reset_n(CPU_RESET),

38 // SRAM

39 .SRAM_ADDR_from_the_sram(SRAM_ADDR),

40 .SRAM_CE_N_from_the_sram(SRAM_CE_N),

41 .SRAM_DQ_to_and_from_the_sram(SRAM_DQ),

42 .SRAM_LB_N_from_the_sram(SRAM_LB_N),

43 .SRAM_OE_N_from_the_sram(SRAM_OE_N),

44 .SRAM_UB_N_from_the_sram(SRAM_UB_N),

45 .SRAM_WE_N_from_the_sram(SRAM_WE_N)

46 );

47

48 endmodule

Step 4:

可順利執行Nios II EDS的Hello World與Hello MicroC/OS-II project template。

完整程式碼下載

DE2_NIOS_LITE_SRAM.7z

Conclusion

若你覺得自己打造Nios II系統有難度,可以考慮使用(原創) DE2_NIOS_Lite 1.0 (SOC) (Nios II) (SOPC Builder) (DE2)與(原創) DE2_NIOS_Lite 1.1 (SOC) (Nios II) (SOPC Builder) (μC/OS-II) (DE2),這是一個簡化的Nios II版本,或者參考DE2 CD的reference design。

See Also

(原創) 如何自己用SOPC Builder建立一個能在DE2上跑μC/OS-II的Nios II系統? (IC Design) (DE2) (Quartus II) (Nios II) (SOPC Builder) (μC/OS-II)

(原創) DE2_NIOS_Lite 1.0 (SOC) (Nios II) (SOPC Builder) (DE2)

(原創) DE2_NIOS_Lite 1.1 (SOC) (Nios II) (SOPC Builder) (μC/OS-II) (DE2)