本文由知乎

赵俊军授权转载,知乎主页为https://www.zhihu.com/people/zhao-jun-jun-19

B.4 映射示例

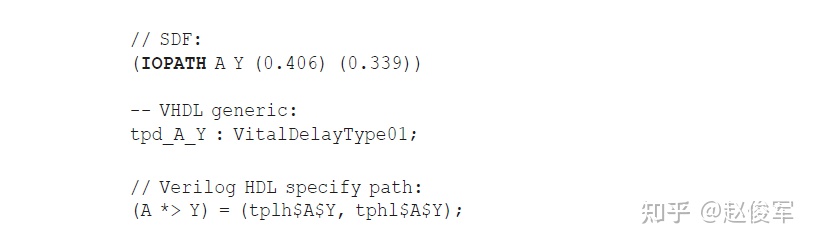

以下是将SDF结构映射到VHDL泛型(generic)和Verilog HDL声明(declaration)的示例。

传播延迟

- 从输入端口A到输出端口Y的传播延迟:上升时间为0.406,下降时间为0.339:

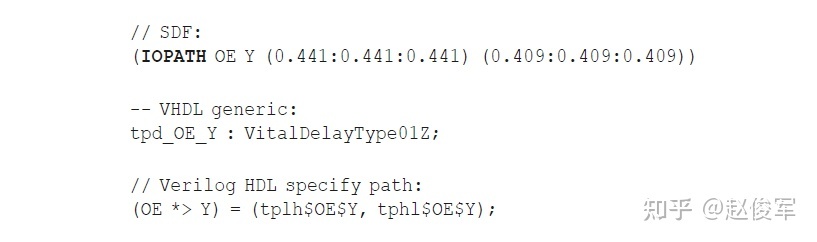

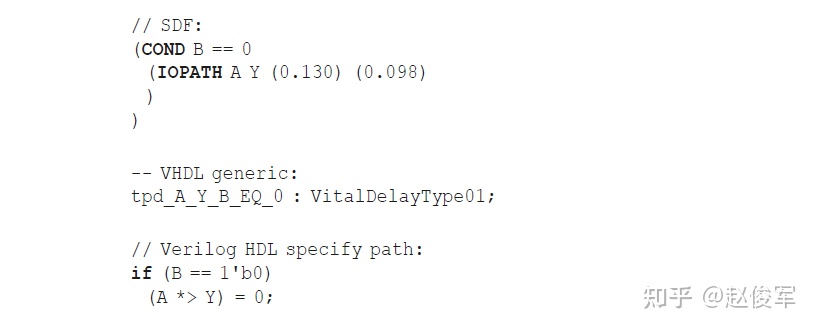

- 从输入端口OE到输出端口Y的传播延迟:上升时间为0.441,下降时间为0.409。最小、标准和最大延迟是相同的:

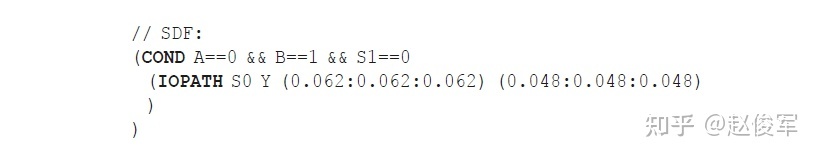

- 从输入端口S0到输出端口Y的条件传播延迟:

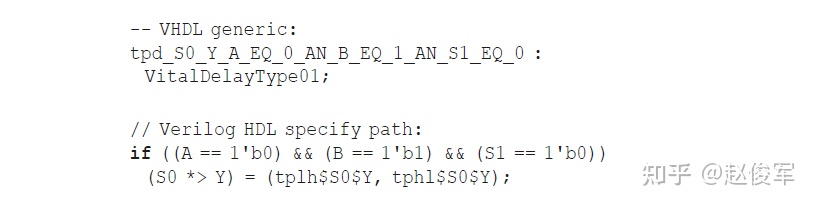

- 从输入端口A到输出端口Y的条件传播延迟:

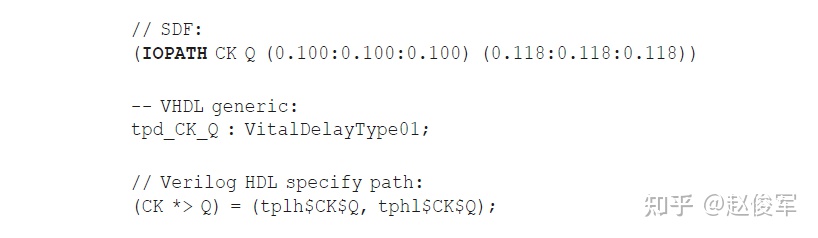

- 从输入端口CK到输出端口Q的传播延迟:

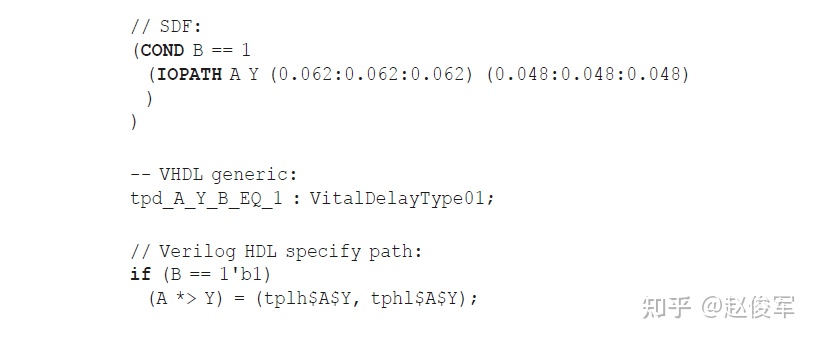

- 从输入端口A到输出端口Y的条件传播延迟:

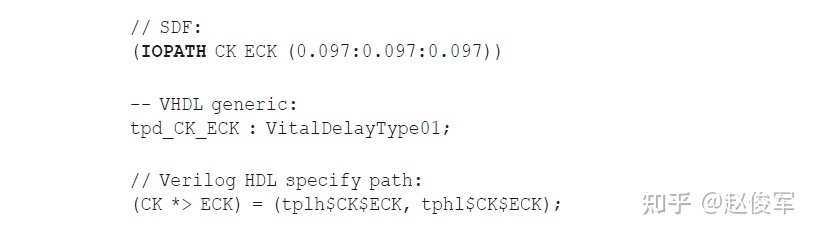

- 从输入端口CK到输出端口ECK的传播延迟:

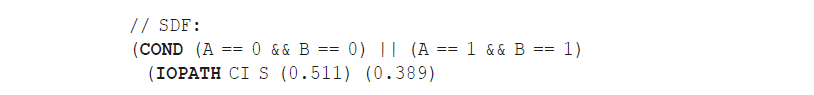

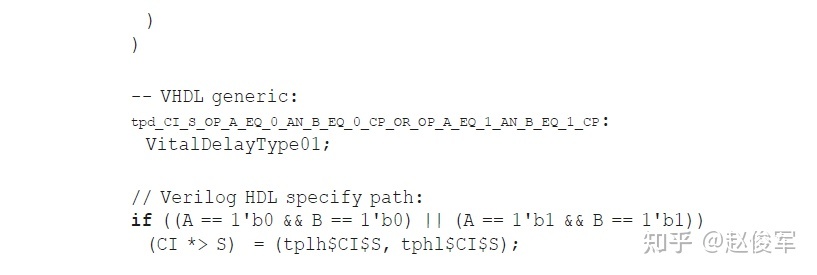

- 从输入端口CI到输出端口S的条件传播延迟:

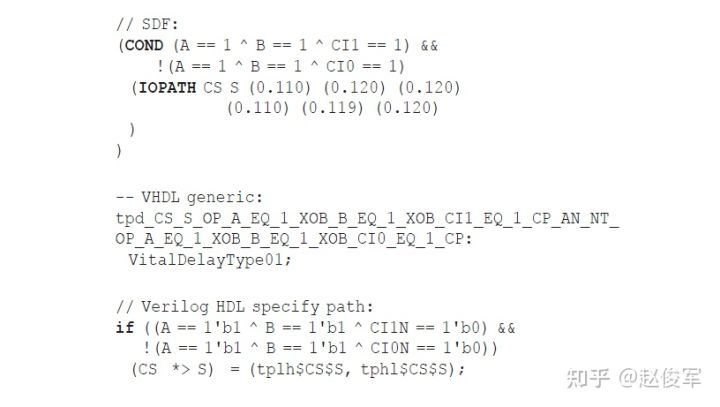

- 从输入端口CS到输出端口S的条件传播延迟:

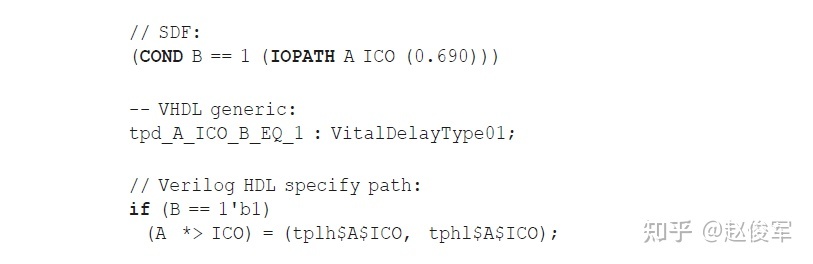

- 从输入端口A到输出端口ICO的条件传播延迟:

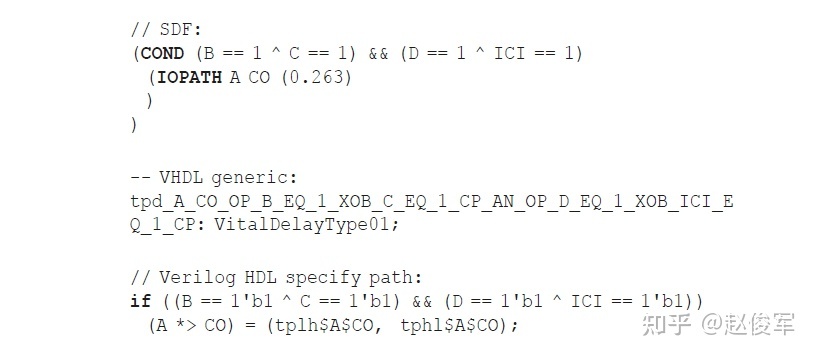

- 从输入端口A到输出端口CO的条件传播延迟:

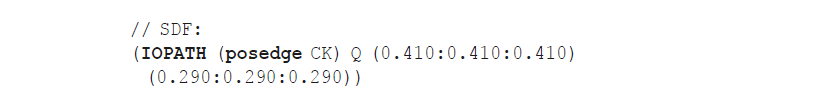

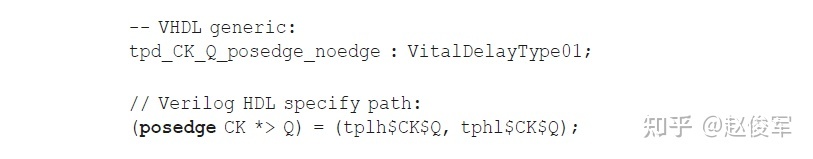

- 从CK的上升沿到Q的延迟:

输入建立时间

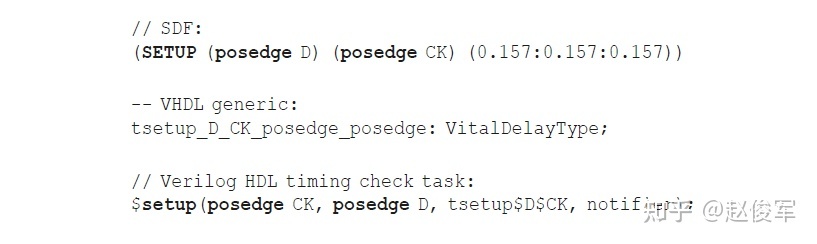

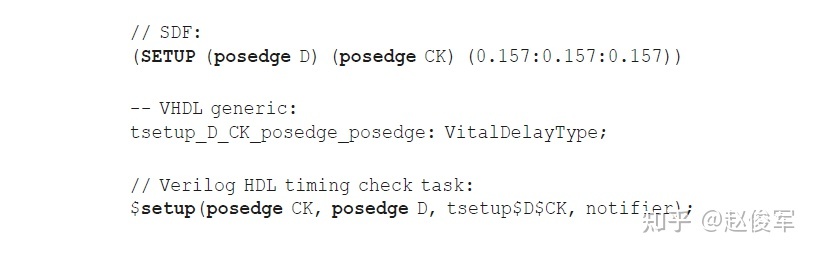

- D的上升沿与CK的上升沿之间的建立时间:

- D的下降沿与CK的上升沿之间的建立时间:

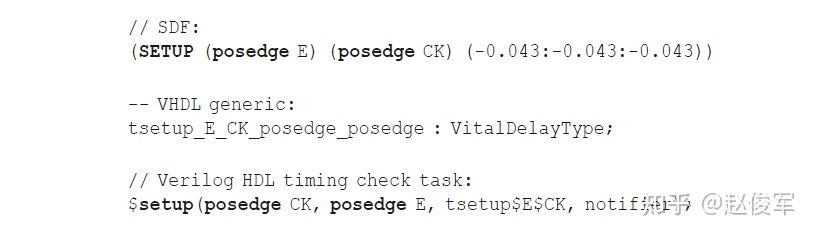

- 输入端口E的上升沿与参考CK的上升沿之间的建立时间:

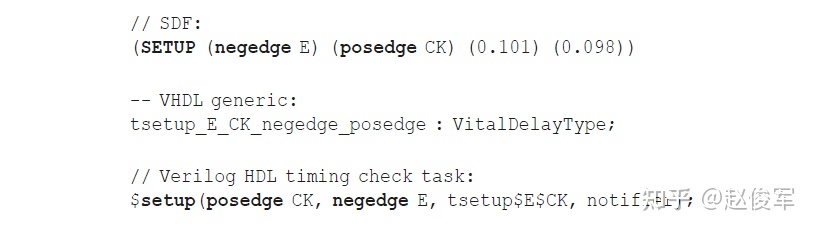

- 输入端口E的下降沿和参考CK的上升沿之间的建立时间:

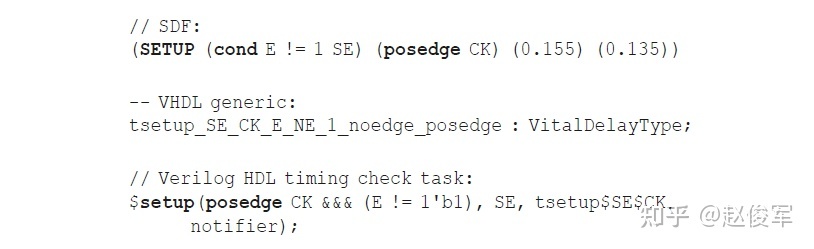

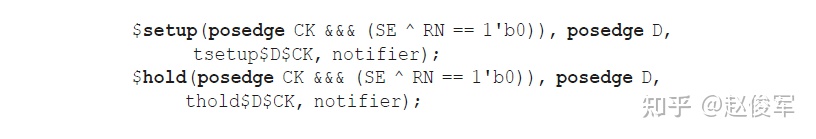

- SE和CK之间的条件建立时间:

输入保持时间

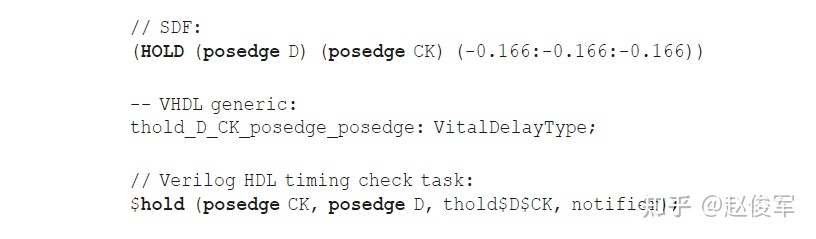

- D的上升沿与CK的上升沿之间的保持时间:

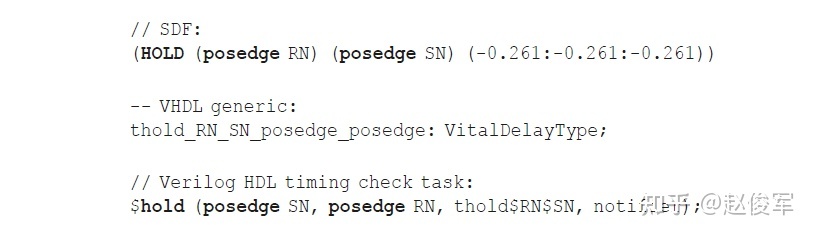

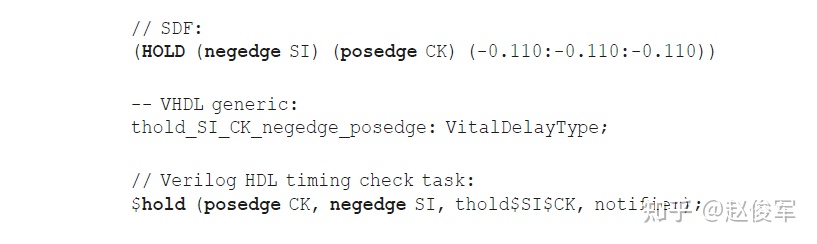

- RN与SN之间的保持时间:

- 输入端口SI与参考端口CK之间的保持时间:

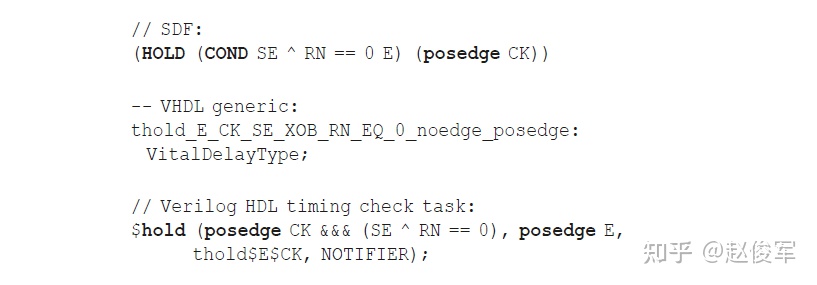

- E和CK上升沿之间的条件保持时间:

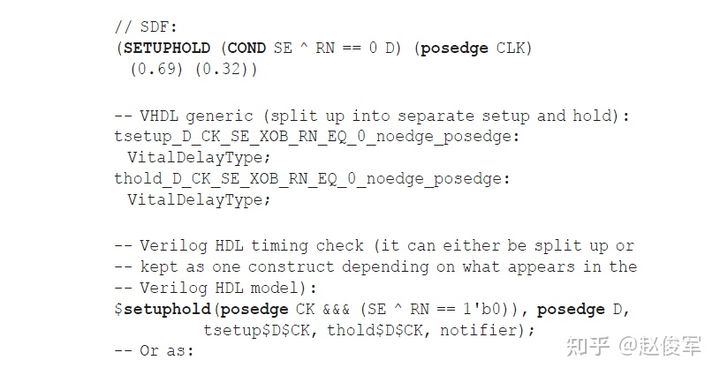

输入建立和保持时间

- 在D和CLK之间的建立时间与保持时间检查。这是一个有条件的检查,第一个延迟值是建立时间,第二个延迟值是保持时间:

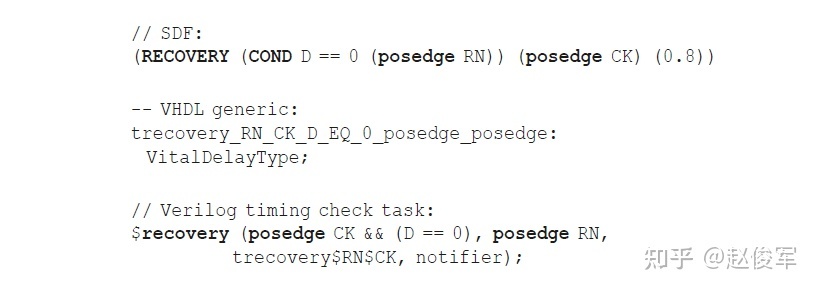

输入恢复时间

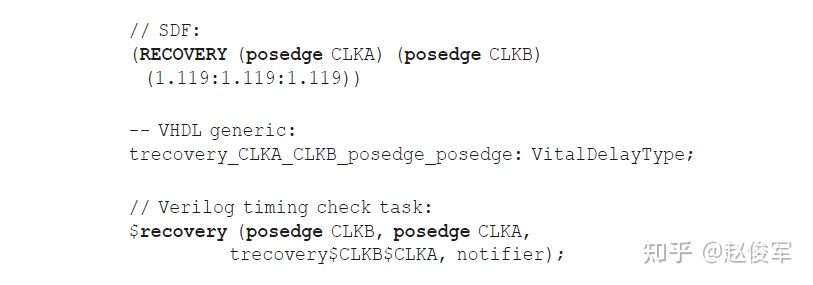

- CLKA和CLKB之间的恢复时间:

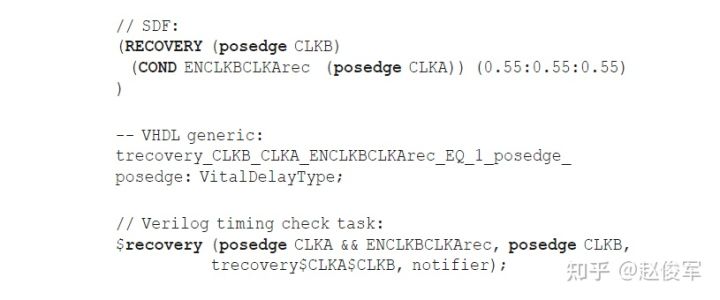

- CLKA上升沿与CLKB上升沿之间的条件恢复时间:

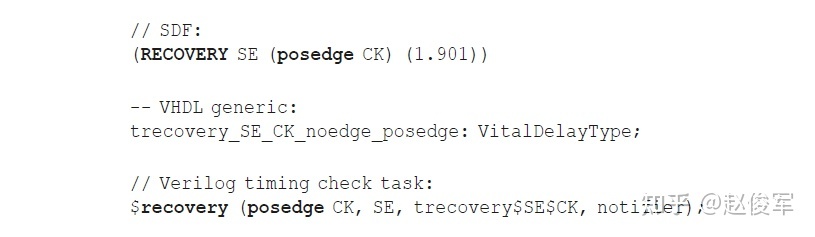

- SE与CK之间的恢复时间:

- RN与CK之间的恢复时间:

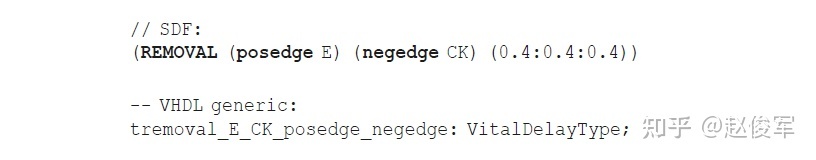

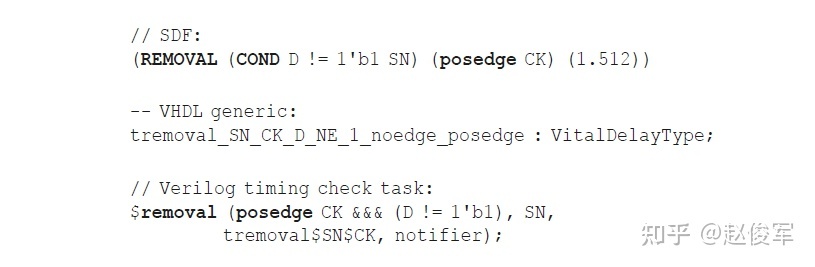

输入撤销时间

- E的上升沿与CK的下降沿之间的撤销时间:

- CK的上升沿和SN之间的条件撤销时间:

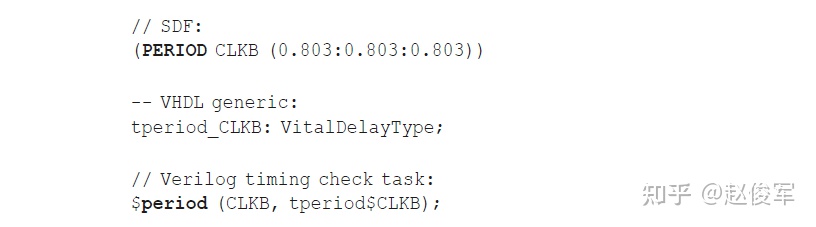

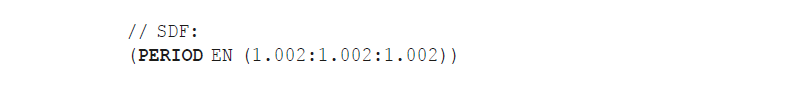

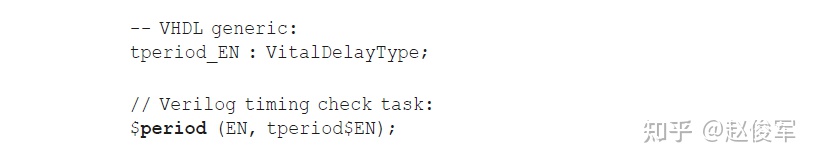

周期

- 输入CLKB的周期:

- 输入端口EN的周期:

- 输入端口TCK的周期:

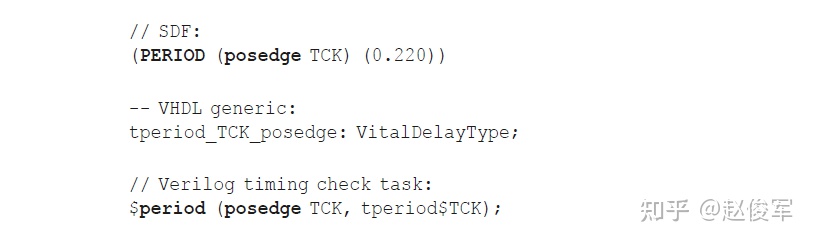

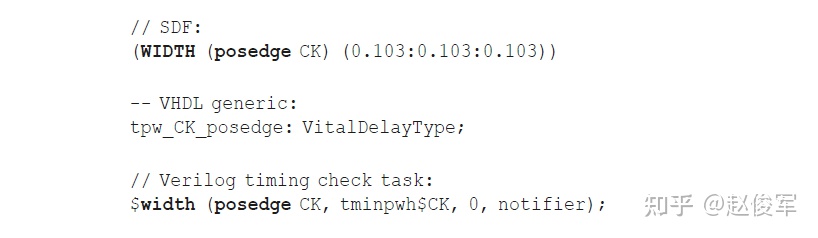

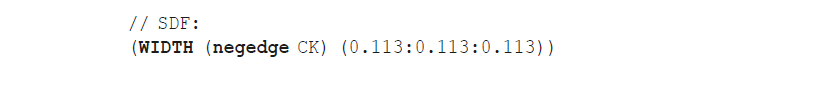

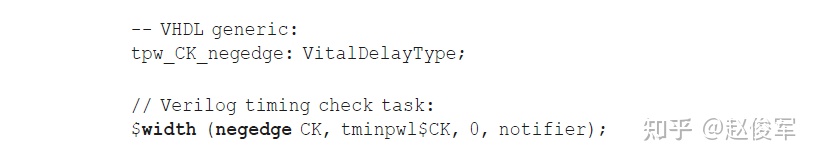

脉宽

- CK上高脉冲的脉冲宽度:

- CK上低脉冲的脉冲宽度:

- RN上高脉冲的脉冲宽度:

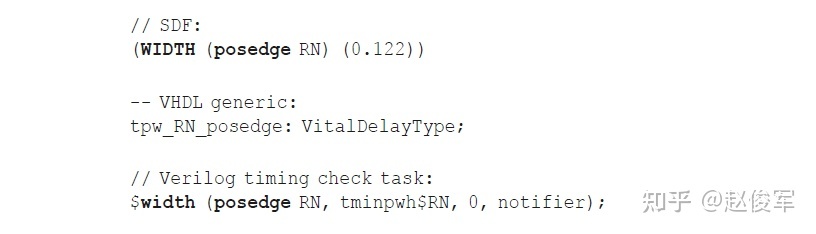

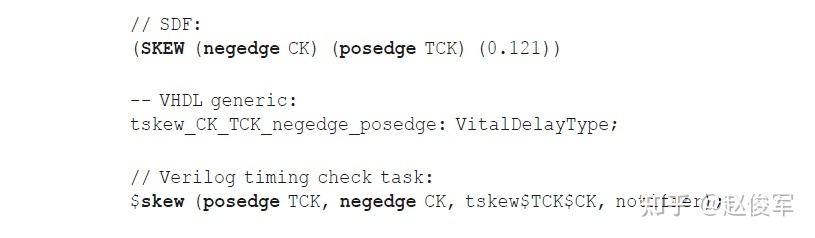

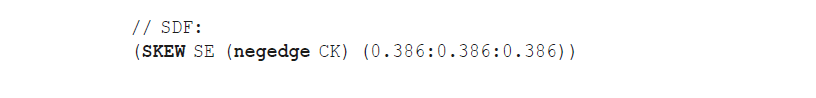

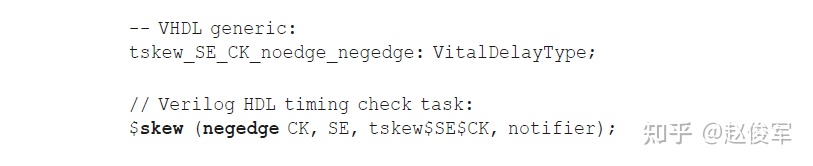

输入偏斜时间

- CK与TCK之间的偏斜:

- SE和CK下降沿之间的偏斜:

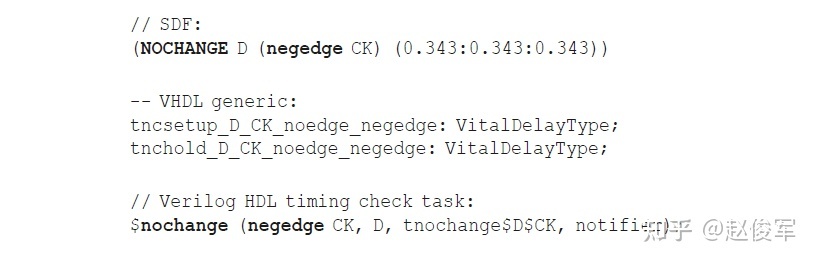

无变化的建立时间

SDF文件中的NOCHANGE结构将同时映射到VHDL中的tncsetup和tnchold泛型。

- D和CK下降沿之间无变化的建立时间:

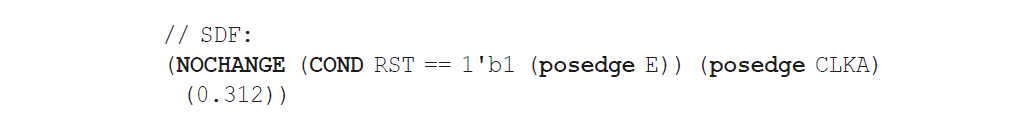

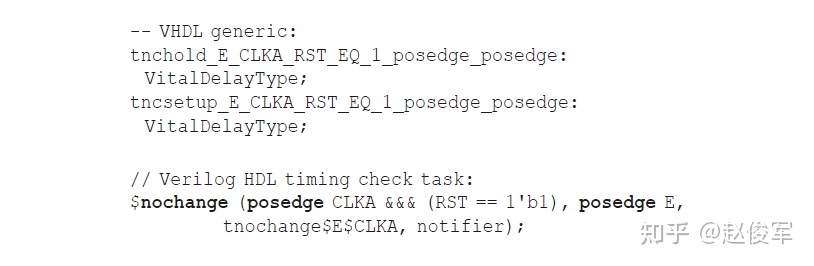

无变化的保持时间

SDF文件中的NOCHANGE结构将同时映射到VHDL中的tncsetup和tnchold泛型。

- E和CLKA之间无变化的条件保持时间:

端口延迟

- 端口OE的延迟:

- 端口RN的延迟:

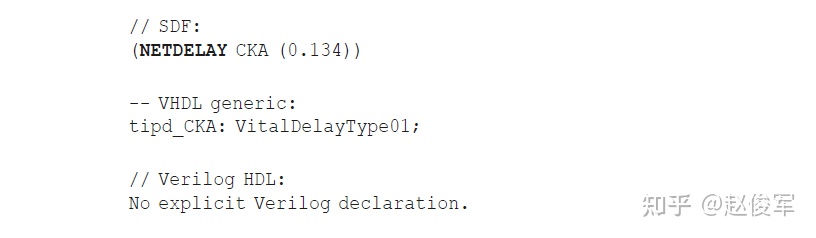

网络延迟

- 连接到端口CKA的网络延迟:

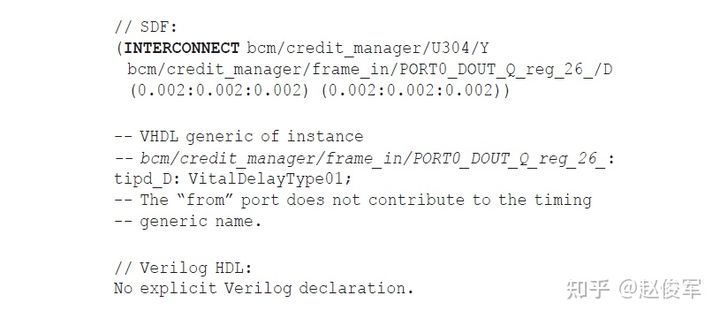

互连路径延迟

- 从端口Y到端口D的互连路径延迟:

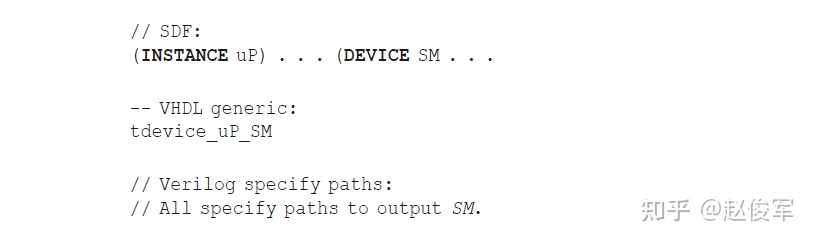

器件延迟

- 实例uP的输出SM的器件延迟:

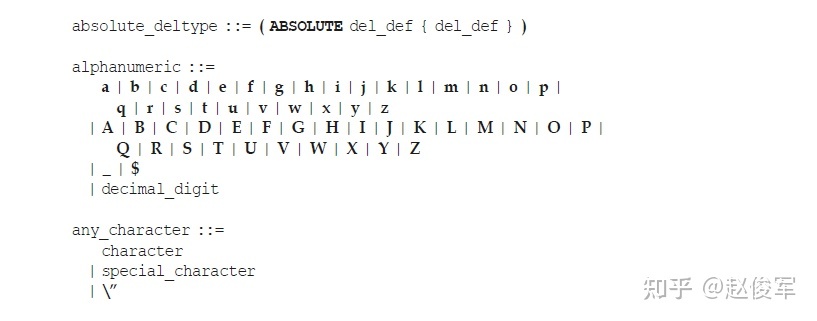

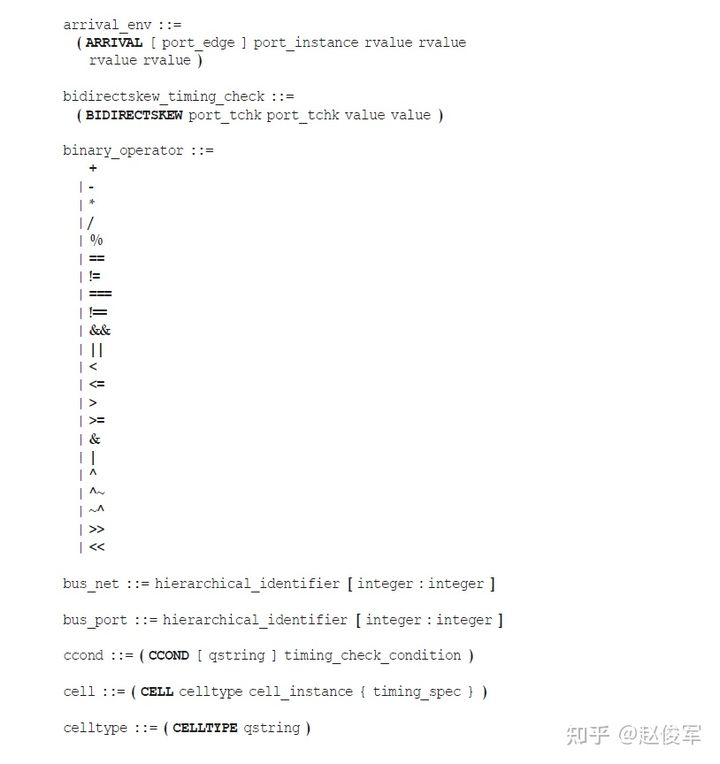

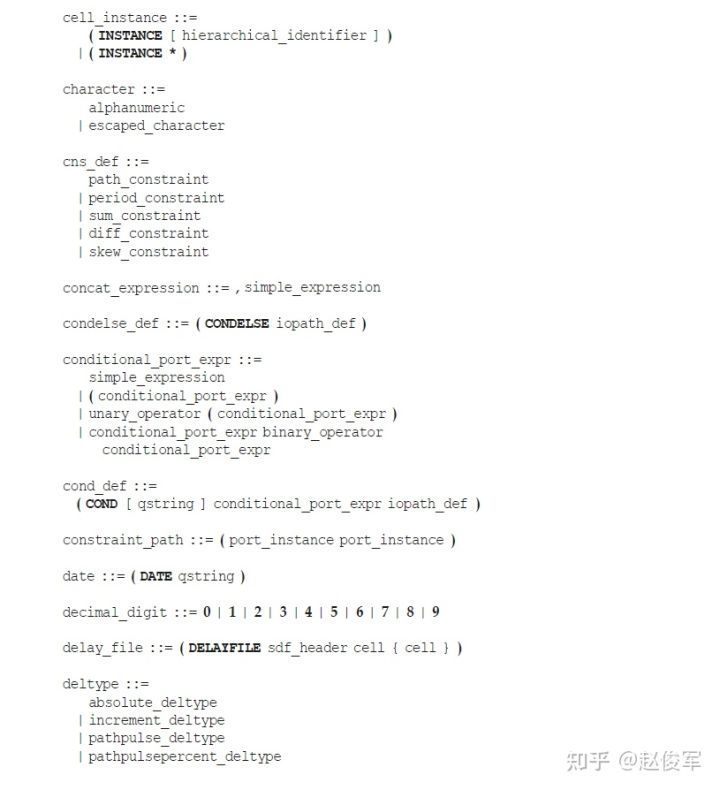

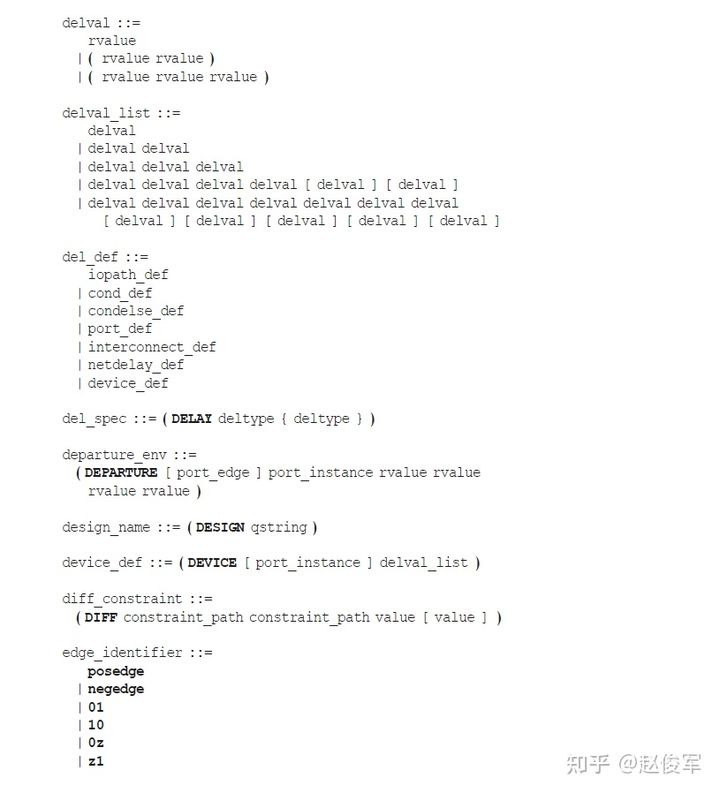

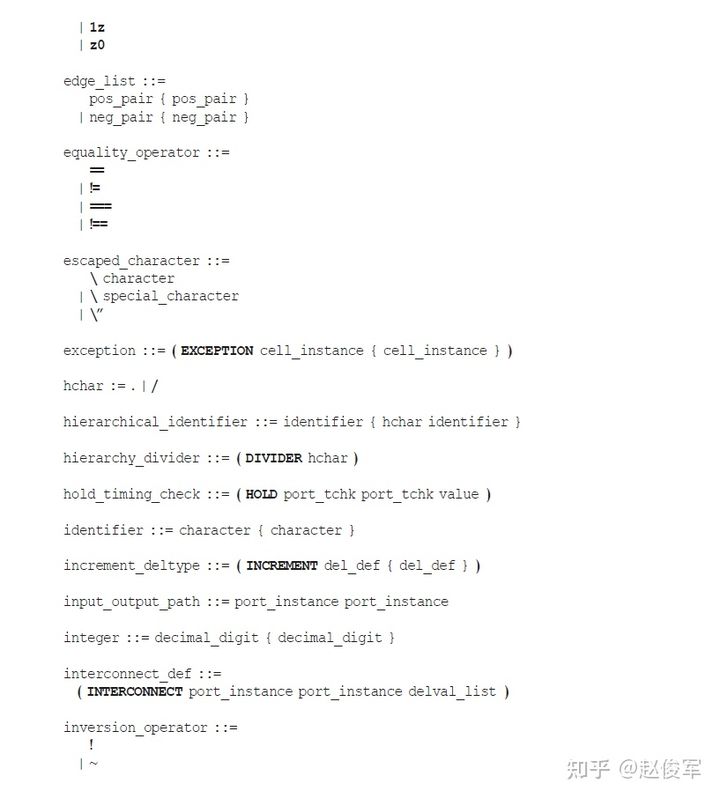

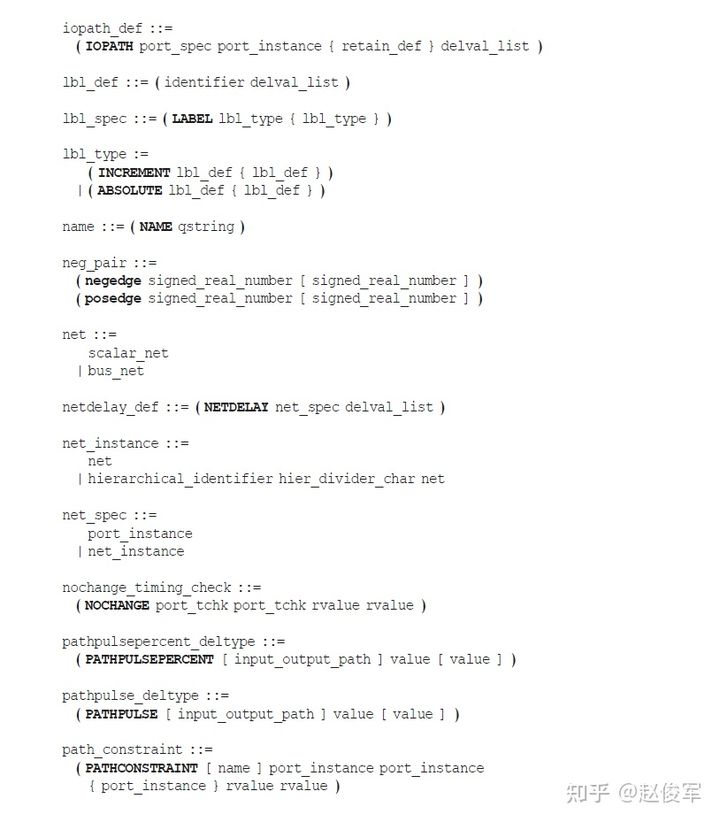

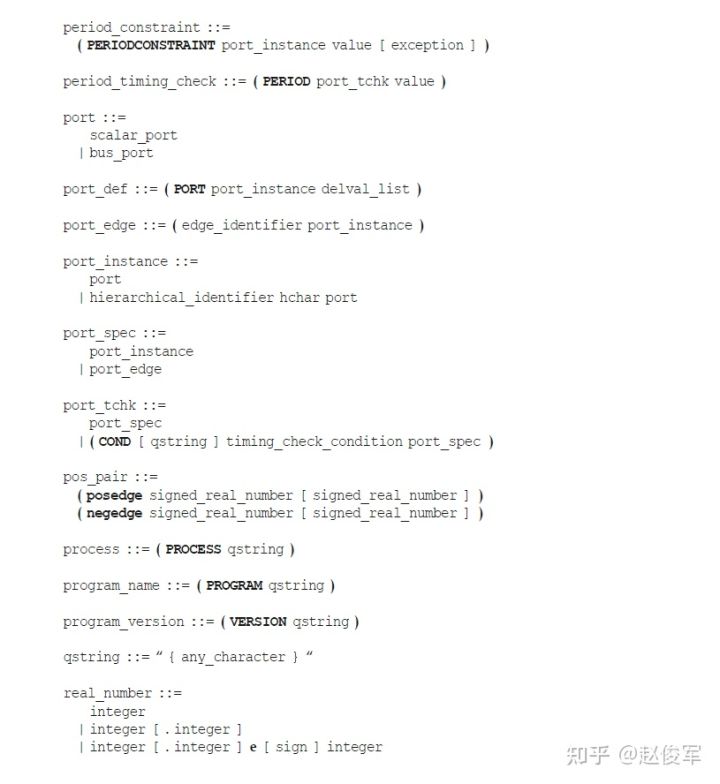

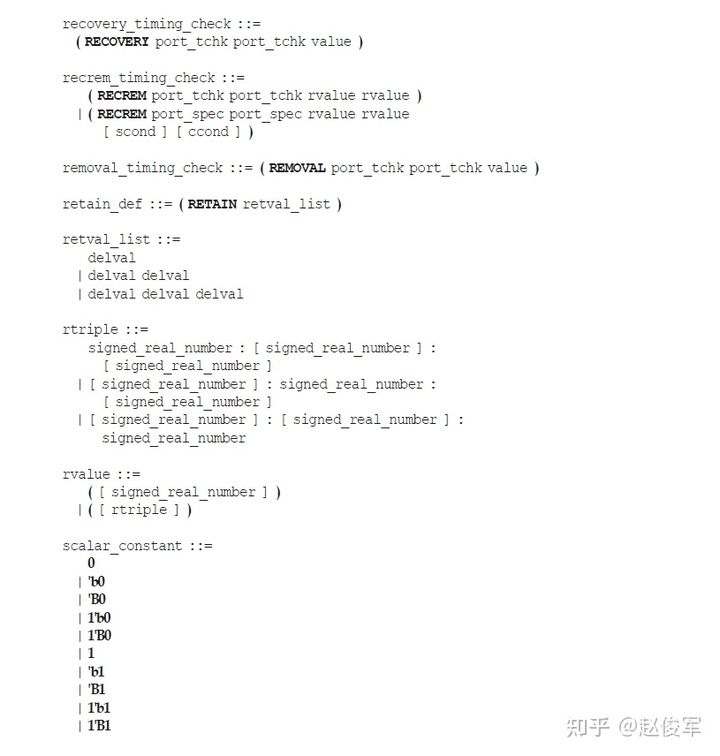

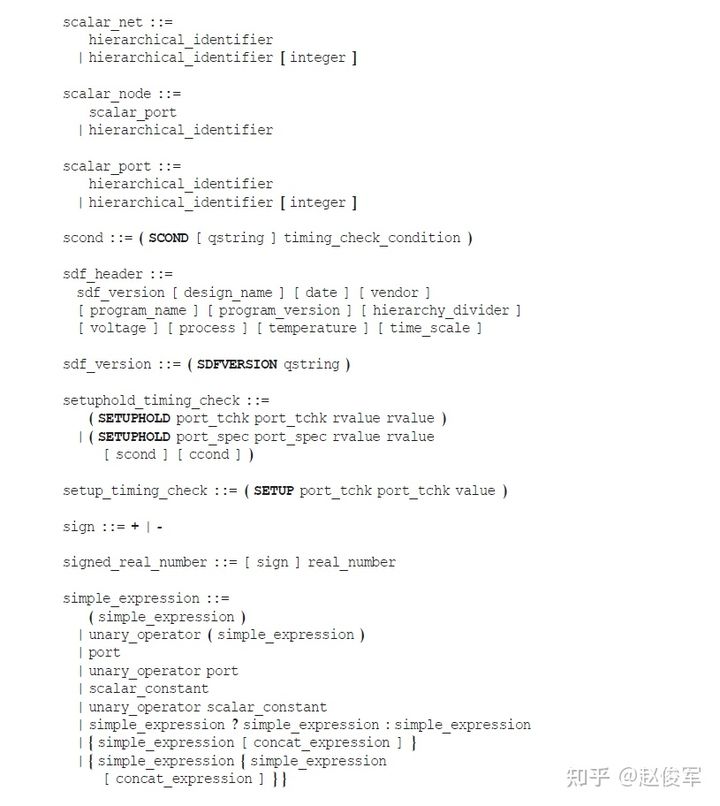

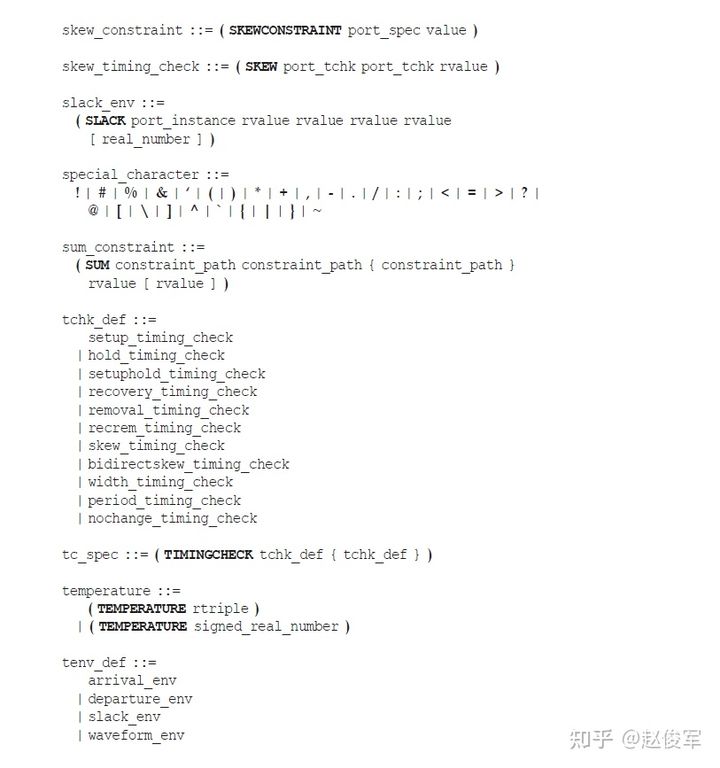

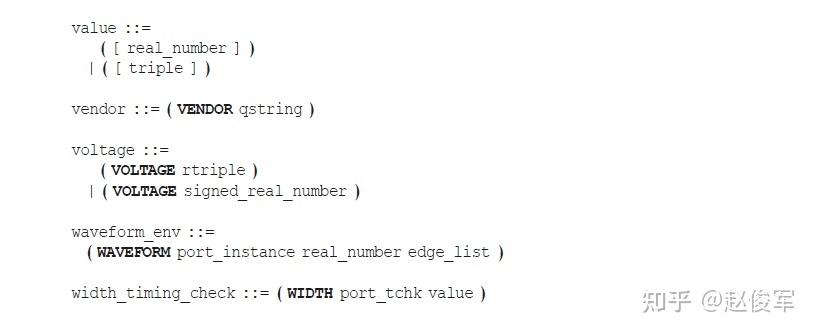

B.5 完整语法

以下是使用BNF格式显示的SDF的完整语法。终端(terminal)名称是大写的,关键字是粗体的,但是不区分大小写。起始的终端是delay_file: