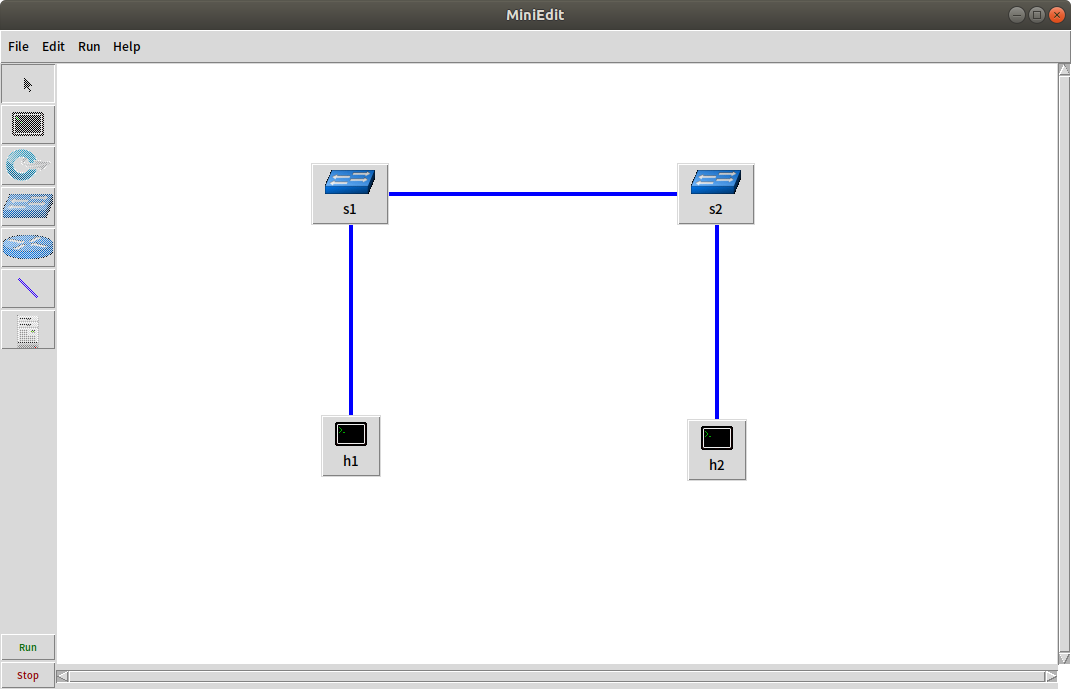

网络拓扑:

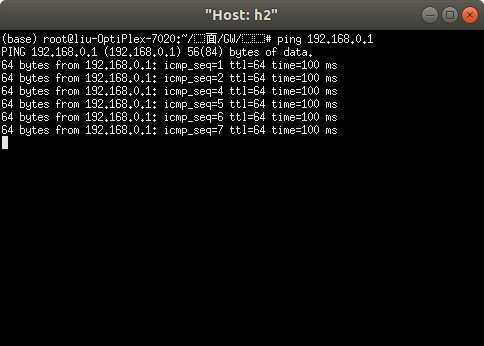

仿真结果:

python 代码:

#!/usr/bin/python from mininet.net import Mininet from mininet.node import Controller, RemoteController, OVSController from mininet.node import CPULimitedHost, Host, Node from mininet.node import OVSKernelSwitch, UserSwitch from mininet.node import IVSSwitch from mininet.cli import CLI from mininet.log import setLogLevel, info from mininet.link import TCLink, Intf from subprocess import call def myNetwork(): net = Mininet( topo=None, build=False, ipBase='10.0.0.0/8') info( '*** Adding controller ' ) info( '*** Add switches ') s1 = net.addSwitch('s1', cls=OVSKernelSwitch, failMode='standalone') s2 = net.addSwitch('s2', cls=OVSKernelSwitch, failMode='standalone') info( '*** Add hosts ') h2 = net.addHost('h2', cls=Host, ip='10.0.0.2', defaultRoute=None) h1 = net.addHost('h1', cls=Host, ip='10.0.0.1', defaultRoute=None) info( '*** Add links ') net.addLink(s2, h2) s1s2 = {'bw':100,'delay':'50ms','loss':5} net.addLink(s1, s2, cls=TCLink , **s1s2) net.addLink(h1, s1) info( '*** Starting network ') net.build() info( '*** Starting controllers ') for controller in net.controllers: controller.start() info( '*** Starting switches ') net.get('s1').start([]) net.get('s2').start([]) info( '*** Post configure switches and hosts ') h1.cmd('ifconfig h1-eth0 192.168.0.1') h2.cmd('ifconfig h2-eth0 192.168.0.2') h1.cmd('route add default gw 192.168.0.2') h2.cmd('route add default gw 192.168.0.1') CLI(net) net.stop() if __name__ == '__main__': setLogLevel( 'info' ) myNetwork()