前言

在某些需求下,数据的位宽后级模块可能不需要原始位宽宽度,需要截位,而某些需求下,需要进行多个数据的合并操作。

在verilog下,截位操作可如下所示:

合并操作可如下所示:

所以问题就来了:如何在不写代码的情况下在block design设计中实现截取与合并的操作呢?

用到的IP

(1)constant IP。

此IP可以输出可配置位宽的常数,电平可配置0或者1。

(2)concat IP。

此IP可以使得分立的线拼接成单一线输出,相当于verilog描述的拼接操作。输入端口数和位宽均可配置。注意In1会放置在高位,[In1,In0]。

(3)slice IP。

此IP功能跟concat IP相反,会把输入截取想要的位宽输出。相当于verilog的位宽截取操作。输入位宽,输出位宽,截取msb和截取lsb都是可以配置的。

实例

100M网口使用MII接口。可以知道数据tx和rx都是4bit位宽的,但在MII IP接口中,数据位宽为8bit。则需截位与合并。

(1)总线位宽合并。

如下图所示,对于100M的网口使用,rx的高4bit需要接0。则需要使用到constant IP和concat IP。

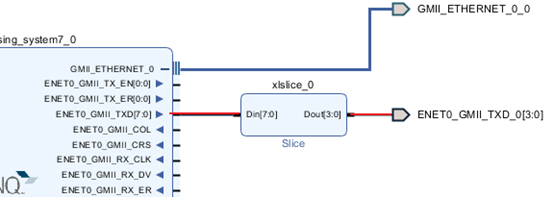

(2)总线位宽截取。

对于100M网口的tx,高位是没用的,则通过slice IP截取低4bit作为输出。

重新生成wrapper,可以看到位宽符合预期,这么做的好处在于无需手动去修改生成的信号位宽,一劳永逸。

以上。