前言

EDF文件可以直接导入Vivado,而无需Verilog源文件。

好处:

(1) 避免沙雕队友修改源代码,则可以直接提交EDF网表文件。

(2) 避免用户剽窃劳动成果。

(3) 对于无需更改的设计复用,直接用EDF网表会贼方便。

软件版本:Vivado2018.3

流程

- 生成EDF网表文件

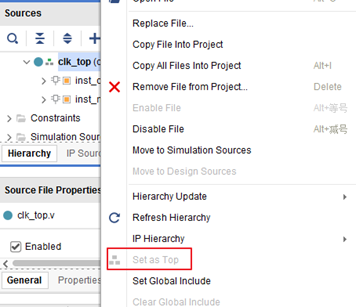

(1)设置需提交的源代码的最顶层为TOP层。可以看到内部调用了2个IP块。

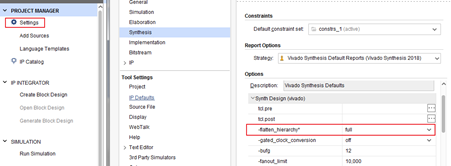

(2)在设置选项的综合设置中选中打平整个设计,防止别人看到模块层次。

设置-mode out_of_context属性,表示在该级不插入任何I/O BUFFERs。

然后运行综合。

(3)tcl控制台输入,导出空壳引脚描述文件。输出文件名跟顶层名一致。

write_verilog -mode synth_stub F: /clk_top.v

(4)tcl控制台输入,导出综合后的网表文件。

若不含Xilinx IP则可通过如下命令生成edf文件:

write_edif F: /clk_top.edf

若含Xilinx IP则需通过如下命令生成edf文件:

write_edif -security_mode all F: / clk_top.edf

可以看到在F盘下生成了相关v和edf文件。

- 使用EDF网表文件

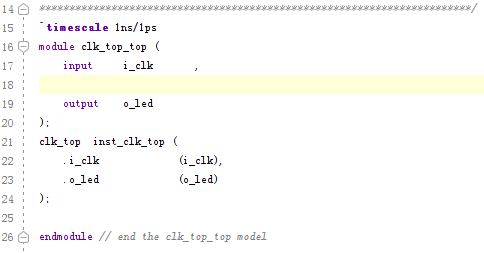

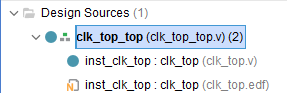

(1) 在新工程中导入空壳v文件及edf网表文件并在top层例化(需要例化的地方例化)。

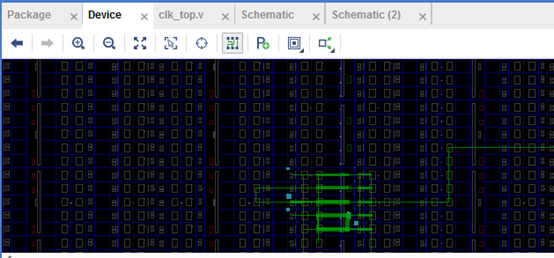

(2) 直接综合适配绑定管脚即可。查看适配结果,可以看到已经适配布线完成。

以上。