前言

从FPGA的PAD到IOB里面的寄存器是有专用布线资源的,而到内部其他寄存器没有专用的布线资源。使用IOB里面的寄存器可以保证每次实现的结果都一样,使用内部其他寄存器就无法保证每次用的都是同一个寄存器且采用同样的布线。

流程

(1)有如下代码:

`timescale 1ns/1ps

module iob_top (

input i_clk ,

input i_a ,

output o_b

);

reg [1:0] r_a_edge = 2'd0;

always @(posedge i_clk)

begin

r_a_edge <= {r_a_edge[0],i_a};

end

reg [11:0] r_cnt = 'd0;

always @(posedge i_clk)

begin

if (r_a_edge == 2'b01)

r_cnt <= 'd0;

else

r_cnt <= r_cnt + 'd1;

end

assign o_b = r_cnt[11];

endmodule // end the iob_top model

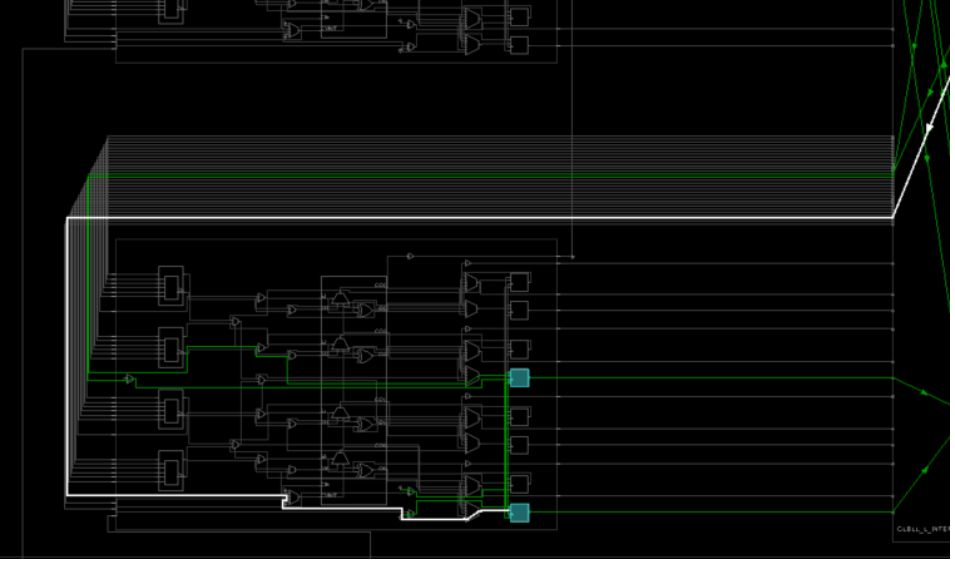

(2)不吸入IOB的方式:适配后可以看到对于检测a的边沿使用了两个寄存器,位于内部的CLB中。

(3)吸入IOB的方式:

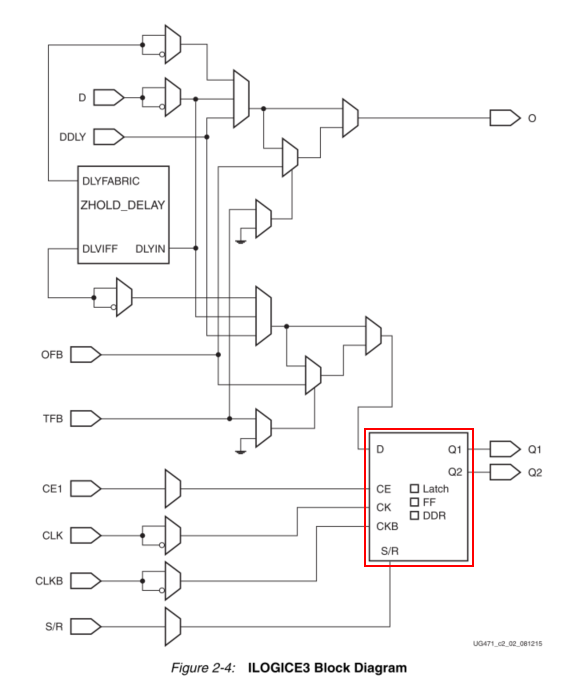

ILOGIC3资源框图:可以看到这个触发器可以作为Latch、FF、DDR使用。

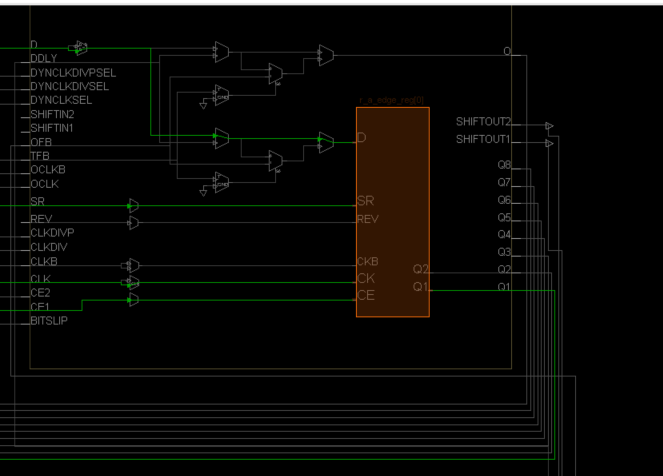

在xdc文件中约束输入使用IOB寄存器资源:

set_property IOB TRUE [all_inputs]

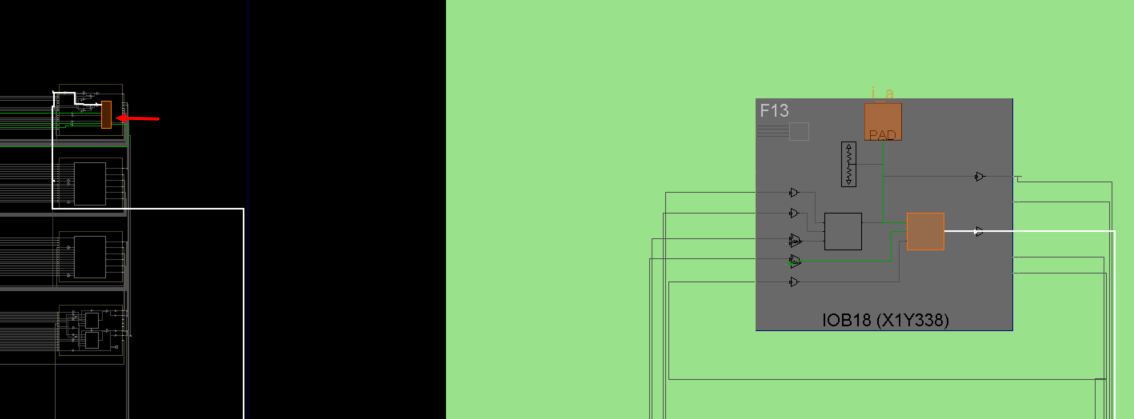

在下图中可以看到使用了IOB寄存器资源,实际上是用了IDDR实现的,另一个寄存器是使用的内部寄存器资源。

如果是用输出的IOB寄存器资源,也是类似的用法。

以上。