前言

ram这种东西,可以用ip方便,也可以自己写代码描述它。

以下讨论单口ram;8bit*256

流程

1.IP:

使用IP当然是最方便的事情啦,但可移植性差而且可定制性较差。

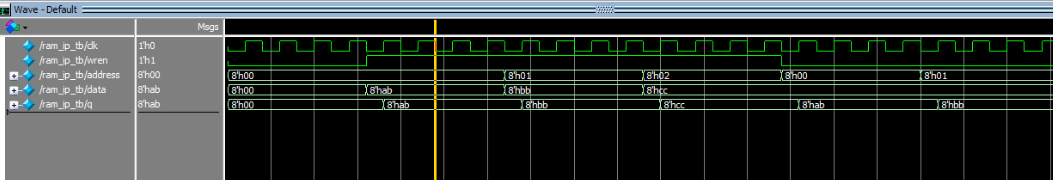

仿真波形:

2.Verilog描述:

描述就得自己写自己调试代码了,不过写好就是一劳永逸啦。。。

开始写了第一版代码:

1 //************************************************ 2 // Filename : ram.v 3 // Author : Kingstacker 4 // Company : School 5 // Email : kingstacker_work@163.com 6 // Device : Altera cyclone4 ep4ce6f17c8 7 // Description : 8bit*256 ram 8 //************************************************ 9 module ram #( parameter DATA_WIDTH = 8,DEPTH = 256,ADDR_WIDTH = 8)( 10 //input; 11 input wire clk, 12 input wire wren, //write high enable; 13 input wire [ADDR_WIDTH-1:0] address, 14 input wire [DATA_WIDTH-1:0] data, 15 //output; 16 output reg [DATA_WIDTH-1:0] q 17 ); 18 reg [DATA_WIDTH-1:0] memory[0:DEPTH-1]; 19 //read; 20 always @(posedge clk ) begin 21 q <= memory[address]; 22 end //always 23 //write; 24 always @(posedge clk ) begin 25 if(wren) begin 26 memory[address] <= data; 27 end 28 end //always 29 endmodule

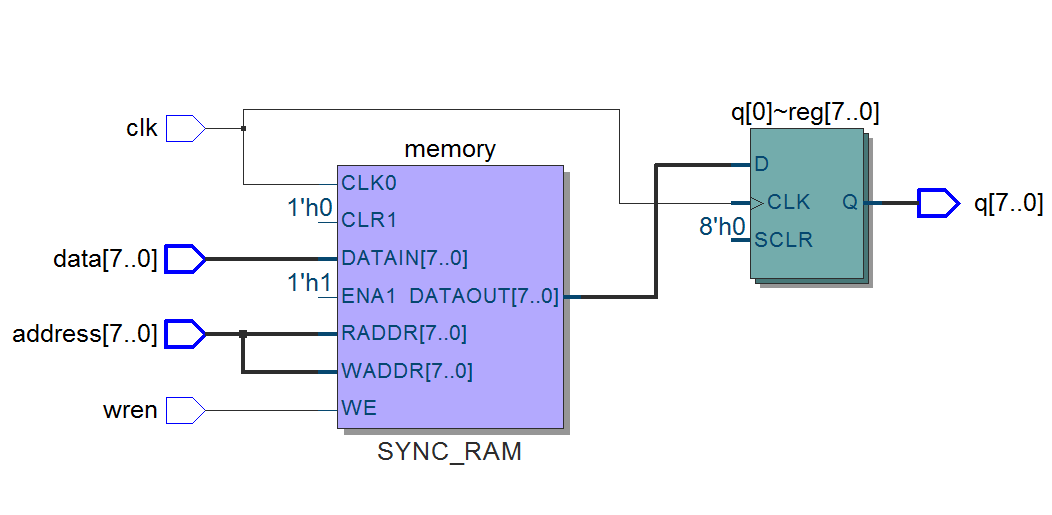

综合RTL:

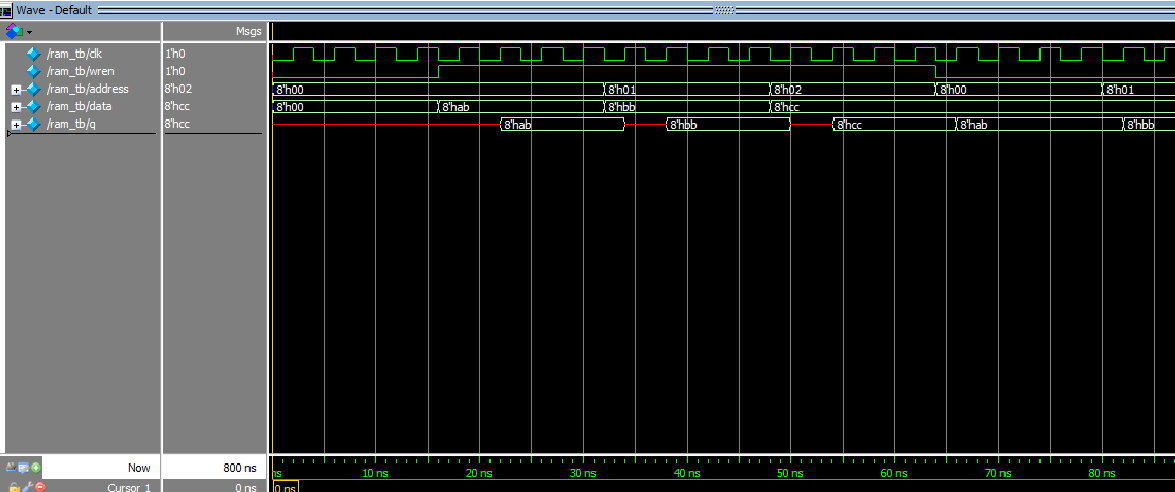

仿真波形:读写同时的时候会有冲突导致xx。

第二版代码:地址寄存一拍。

1 //************************************************ 2 // Filename : ram.v 3 // Author : Kingstacker 4 // Company : School 5 // Email : kingstacker_work@163.com 6 // Device : Altera cyclone4 ep4ce6f17c8 7 // Description : 8bit*256 ram 8 //************************************************ 9 module ram #( parameter DATA_WIDTH = 8,DEPTH = 256,ADDR_WIDTH = 8)( 10 //input; 11 input wire clk, 12 input wire wren, //write high enable; 13 input wire [ADDR_WIDTH-1:0] address, 14 input wire [DATA_WIDTH-1:0] data, 15 //output; 16 output wire [DATA_WIDTH-1:0] q 17 ); 18 reg [DATA_WIDTH-1:0] memory[0:DEPTH-1]; 19 reg [ADDR_WIDTH-1:0] address_reg; 20 //read; 21 always @(posedge clk ) begin 22 address_reg <= address; 23 end //always 24 assign q = memory[address_reg]; 25 //write; 26 always @(posedge clk ) begin 27 if(wren) begin 28 memory[address] <= data; 29 end 30 end //always 31 32 endmodule

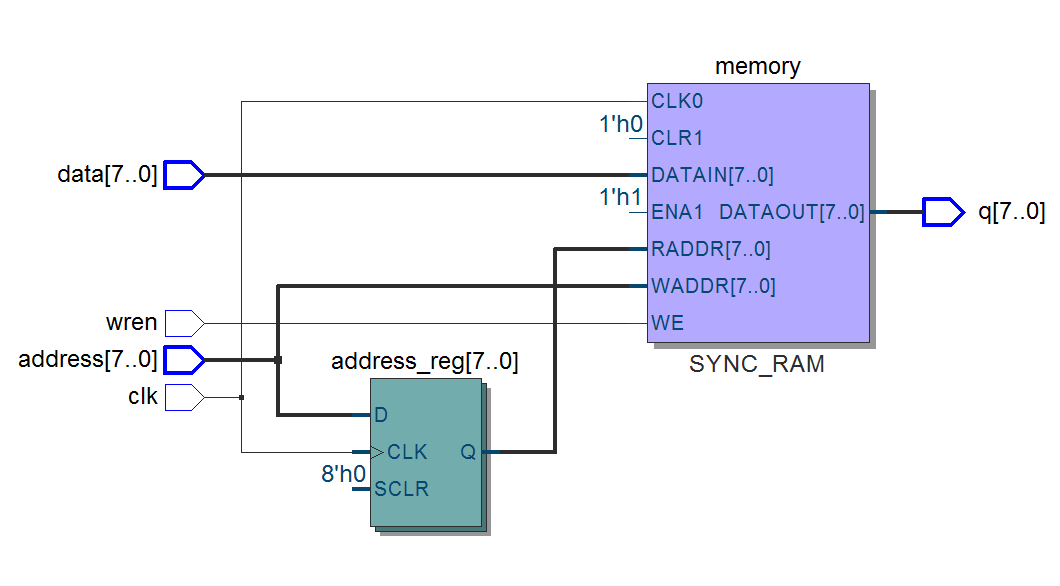

综合rtl:

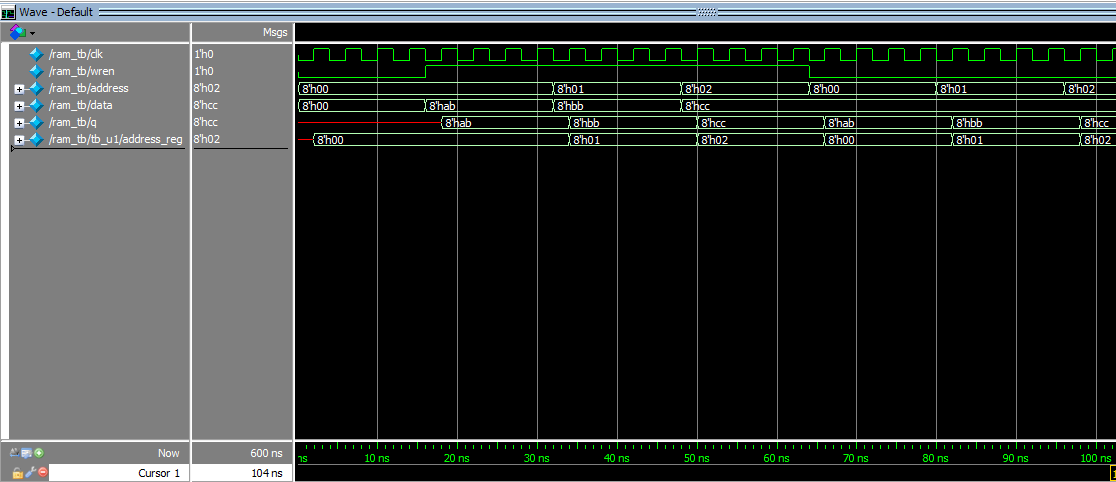

仿真波形:

以上。