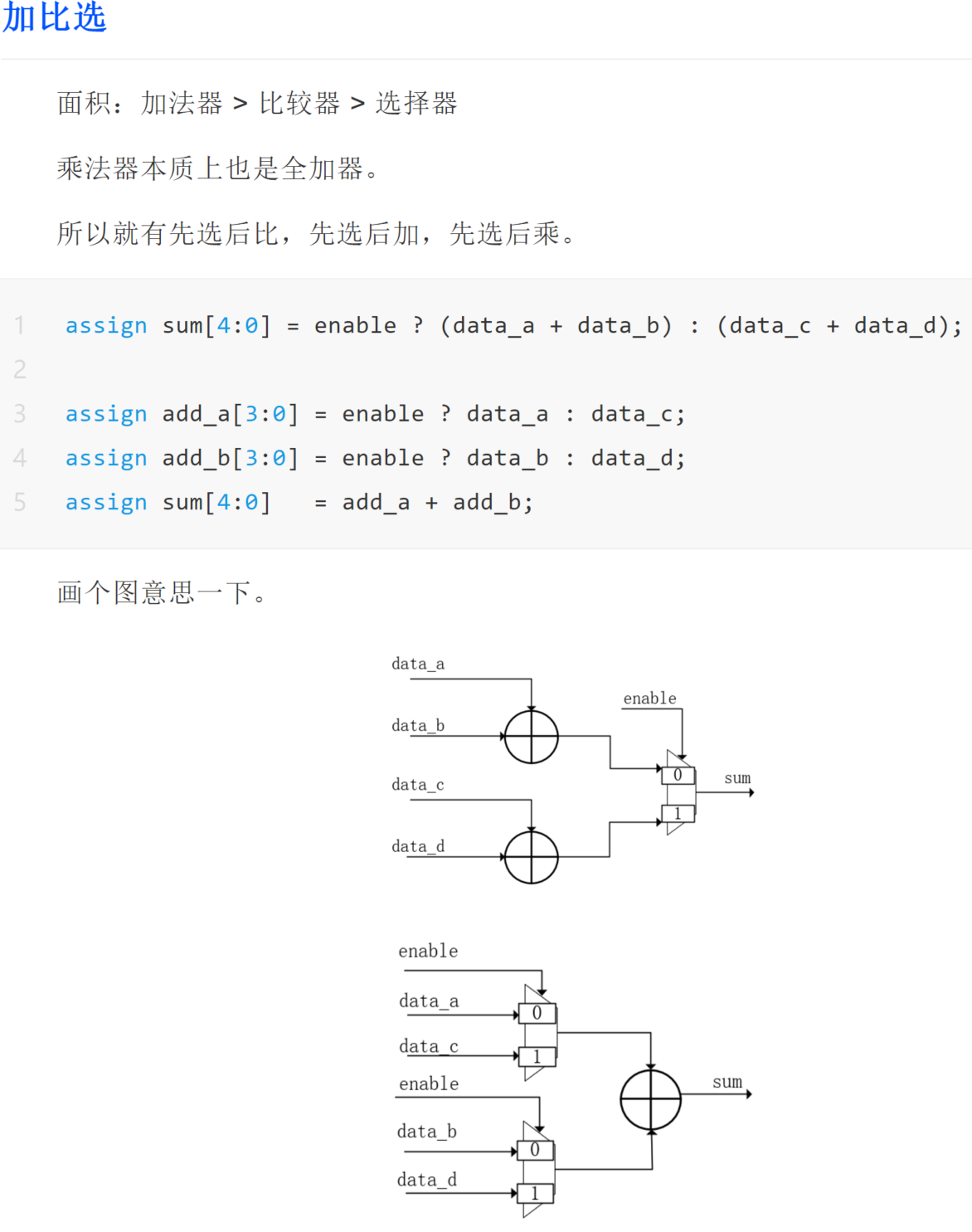

奇技淫巧我不会,但我这有一些我工作后才学到的一些Verilog写法。数字电路设计主要就是,选择器、全加器、比较器,几个常用逻辑门,再加个D触发器,电路基本都能实现了。写代码其实是个体力活,电路和时序图应该在设计阶段就已经到了你的文档里或在脑子里没来得及写出来。组合逻辑+时序逻辑

assign或always@(*)always@(posedge clk or negedge rst_n)

有人说掌握Verilog 20%的语法就可以描述 90%以上的电路,说的对。

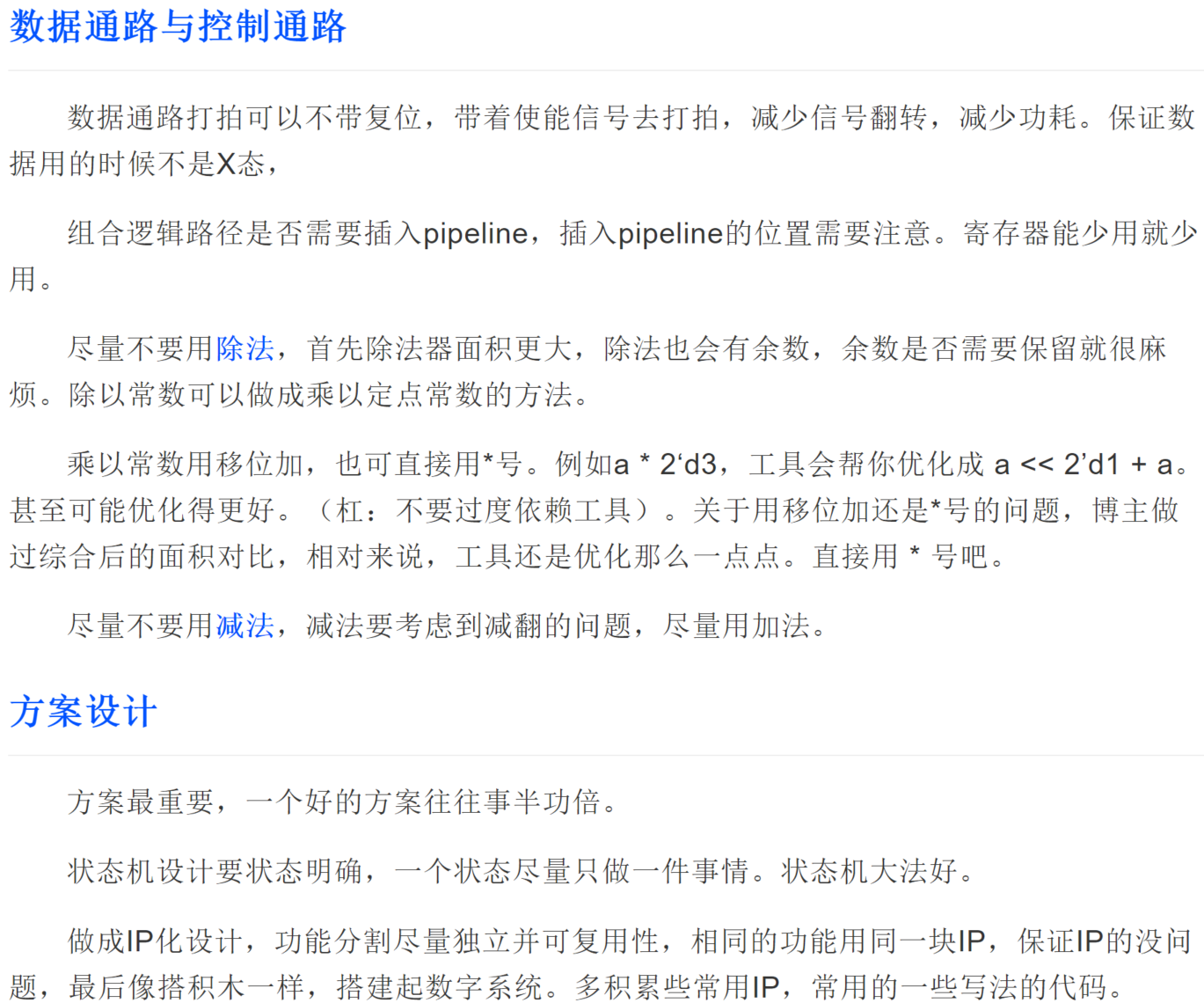

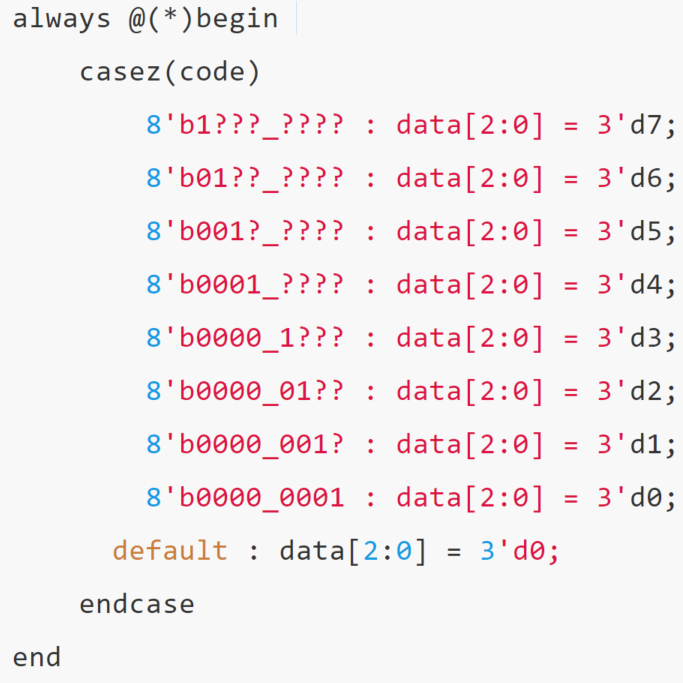

casez

这样的case有优先级选择,可综合,实际项目可以使用,不过我个人习惯上还是,有优先用if-else,没有直接用case。synopsys的EDA工具有关于full case与parallel case可以查看下面博客链接。https://blog.csdn.net/li_hu/article/details/10336511

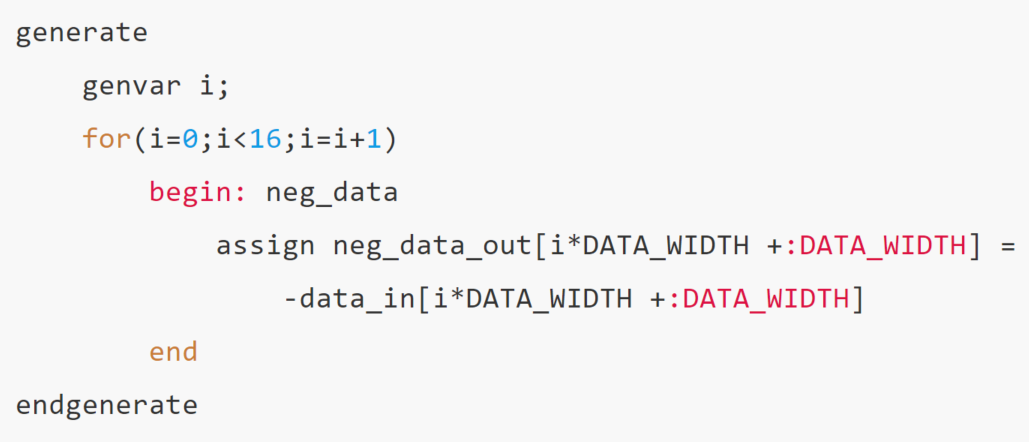

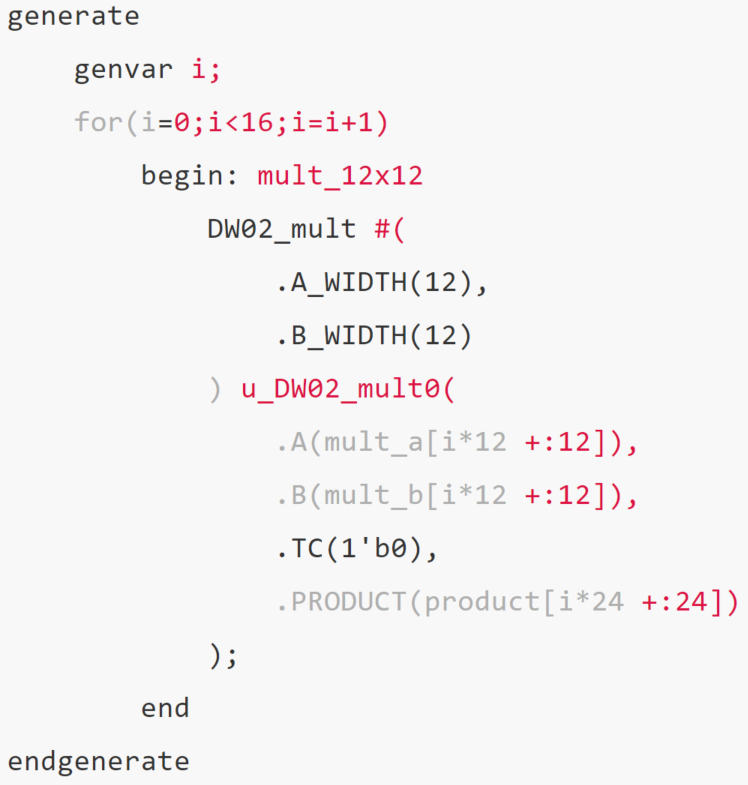

generate+for

合理使用generate+for循环可以提高编码效率,同样的赋值语句需要赋值多次。

同一个模块需要实例化多次:

当然这样写debug会有一些困扰,Verdi会显示每一个generate块,选中对应的块,加进去的波形就会是对应的bit信号。

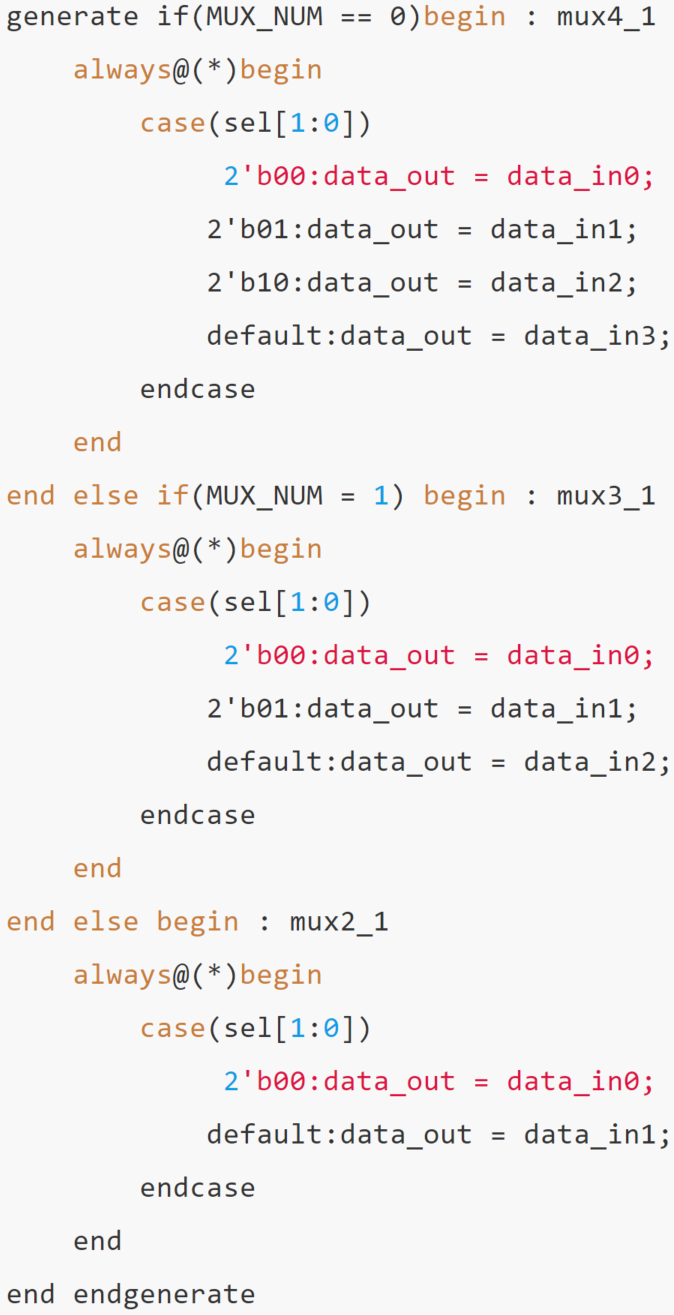

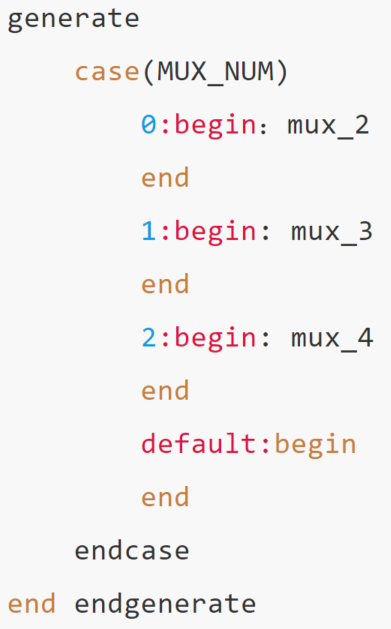

generate if/case

做一些通用IP的方法,随便举个例子比如要做一个选择器通用IP,支持二选一,三选一,四选一。

generate case可以写更多的分支

调用的时候只需要:

布线太密的原因

寄存器位宽太大。

reg [10000-1:0] data;