本文主要是通过迁移的思维,记录本人初次使用周立功的Aworks框架进行BSP开发

前置知识,对于DDR时钟的调整,无非选择其父类时钟,并进行相应的分频即可,当然还得根据SDRAM手册参数进行相应的调整。本文描述在其默认的父时钟不变下,提高其DDR工作频率,提高SDRAM读写的速度。

1. 首先阅读芯片手册

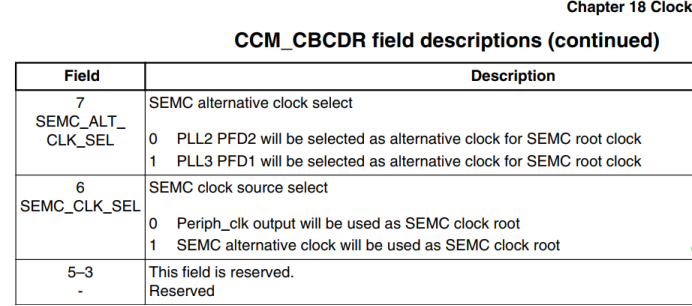

SDRAM的时钟如下所示,SEMC_CLK_ROOT 有两个父类时钟PLL2_PFD2及PLL3_PFD1,在SDK里默认选择使用PLL2_PFD2作为其父类时钟。

CCM_CBCDR寄存器可选择其父类时钟

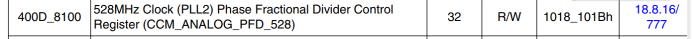

CCM_ANALOG_PFD_528寄存器可以配置DDR的工作时钟

如下字段可配置SEMC_CLK_ROOT:

2. 实际修改

实际算法如下所示:

DDR_ROOT = 528*18/29 = 327.724 / 2 = 163.86Mhz

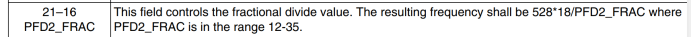

0x101D101B = 163.86M PFD2_FRAC = 29

0x101E101B = 158.4M PFD2_FRAC = 30

0x101F101B = 153.29M PFD2_FRAC = 31

0x1020101B = 148.5M PFD2_FRAC = 32

0x1021101B = 144M PFD2_FRAC = 33

0x1022101B = 139.76M PFD2_FRAC = 34

0x1023101B = 135.77M PFD2_FRAC = 35

0x1024101B = 132M PFD2_FRAC = 36

代码修改位置如下所示:

时钟链上的选择路径如下图所示:

3. 总结

NA。