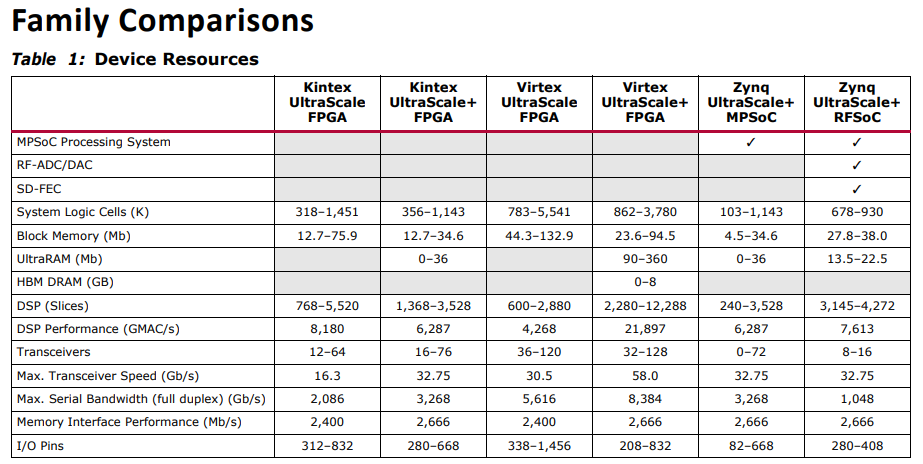

总结: K系列FPGA与KU系列FPGA的主要区别,体现在: (1)工艺制程不一样,K-28nm,KU-20nm; (2)Ultra-Scale采用SSI;大容量K系列也采用SSI,SSI为了解决资源过多,使用多块硅片 ;

(3)KU资源更多,性能更高;

Introduction to the UltraScale Architecture The Xilinx® UltraScale™ architecture is the first ASIC-class All Programmable architecture to enable multi-hundred gigabit-per-second levels of system performance with smart processing, while efficiently routing and processing data on-chip. UltraScale architecture-based devices address a vast spectrum of high-bandwidth, high-utilization system requirements by using industry-leading technical innovations, including next-generation routing, ASIC-like clocking, 3D-on-3D ICs, multiprocessor SoC (MPSoC) technologies, and new power reduction features. The devices share many building blocks, providing scalability across process nodes and product families to leverage system-level investment across platforms. Virtex® UltraScale+™ MPSoC devices provide the highest performance and integration capabilities in a FinFET node, including both the highest serial I/O and signal processing bandwidth, as well as the highest on-chip memory density. As the industry's most capable FPGA family, the Virtex UltraScale+ devices are ideal for applications including 1+Tb/s networking and data center and fully integrated radar/early-warning systems. Virtex UltraScale+ MPSoC devices provide the greatest performance and integration at 20 nm, including serial I/O bandwidth and logic capacity. As the industry's only high-end FPGA at the 20 nm process node, this family is ideal for applications including 400G networking, large scale ASIC prototyping, and emulation. Kintex® UltraScale+ devices provide the best price/performance/watt balance in a FinFET node, delivering the most cost-effective solution for high-end capabilities, including transceiver and memory interface line rates as well as 100G connectivity cores. Our newest mid-range family is ideal for both packet processing and DSP-intensive functions and is well suited for applications including wireless MIMO technology, Nx100G networking, and data center.

Kintex UltraScale devices provide the best price/performance/watt at 20 nm and include the highest signal processing bandwidth in a mid-range device, next-generation transceivers, and low-cost packaging for an optimum blend of capability and cost-effectiveness. The family is ideal for packet processing in 100G networking and data centers applications as well as DSP-intensive processing needed in next-generation medical imaging, 8k4k video, and heterogeneous wireless infrastructure. Zynq® UltraScale+ MPSoC devices provide 64-bit processor scalability while combining real-time control with soft and hard engines for graphics, video, waveform, and packet processing. Integrating an ARM®-based system for advanced analytics and on-chip programmable logic for task acceleration creates unlimited possibilities for applications including 5G Wireless, next generation ADAS, and Industrial Internet-of-Things.

K系列FPGA vs. KU系列FPGA :

Ultrascale系列FPGA只有没有AU系列,只有KU/VU/ZU系列;UltraScale系列中多了 Ultra-RAM/HBM-DRAM资源;

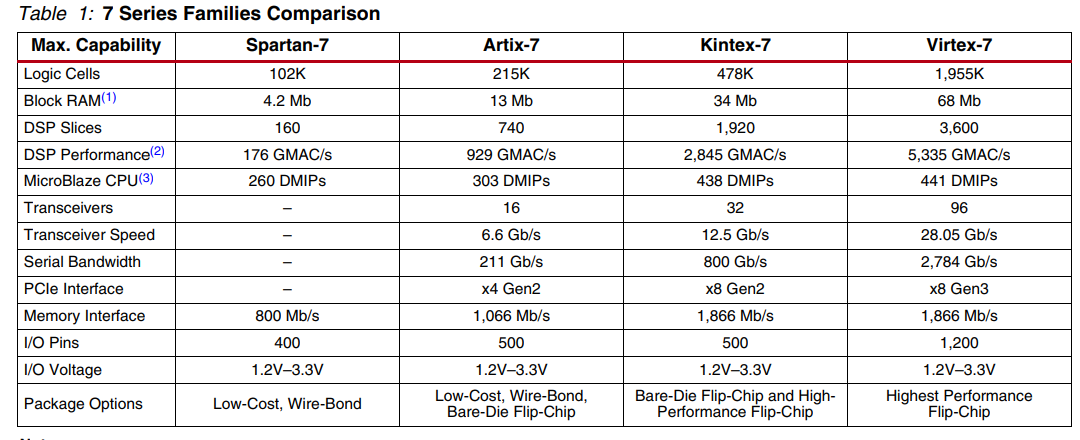

* 7 series families comparison 表格中Logic Cells代表系列中最大值;S7系列没有收发器和PCIe接口。

FPGA中,Logic cells资源对应的FPGA的什么结构?

参考:

ug1026-ultrascale architecture migration;

ds890-ultrascale-overview;

ds180-7 Series FPGAs Data Sheet: Overview