AD16的主要功能是画电路原理图和根据电路原理图设计PCB板。为了使设计的电路、画完的电路原理图,从电路原理上不存在错误,从电路逻辑上不存在混乱,AD16专门开发了电路原理图的仿真程序。这样可以把设计存在的问题,在第一步:绘制电路原理图阶段就及时发现,然后根据仿真结果,改进电路原理图。这就避免了等到印刷电路板装配零件完成为成品之后再发现问题时,造成的大量的人力物力损失。 同样:设计PCB时,也是先在电脑上根据电路原理图,绘制PCB板图。然后再把电脑PCB板图拿到PCB工厂生产PCB板。AD16同样设计了PCB板信号完整性分析程序,把电脑上绘制的PCB板图,进行信号完整性仿真分析,从而早期发现设计的PCB板图是否存在瑕疵,及时改进到理想状态。如果绘制好PCB板图,没有经过PCB板图的信号完整性分析仿真,直接拿到工厂生产PCB板,PCB板装配完工成为成品后,才发现有瑕疵,那就造成了极大的浪费。

PCB板的信号完整性分析,是指PCB板中的一个网络,这个网络的输出波形,与该网络的输入波形相比,尽量的相似,尽量的少失真、少延迟、少变形、少缺失、少振铃、少过冲。低频的数字电路PCB板,输入信号经过PCB内网络的处理后,网络输出的信号波形失真很小,而在高频的数字电路PCB板,如果PCB板设计稍有不当,被测试的网络输出信号与该网络输入信号相比,就会产生明显的延迟、失真,导致生产的PCB板不达标,无法使用。

进行信号完整性分析的前提条件:需要具备以下条件,才能进行信号完整性分析:

- 电路中被测试的网络,必须包含IC的一个信号输出脚,这个输出信号作为激励这个网络的信号源。如果一个网络只有R、L、C等无源器件,没有晶体管、IC等有源器件,那么这个无源网络,就不能进行信号完整性分析。也就是说:必须设定被测试网络的激励源。

- 在绘制电路原理图、PCB板图时,绘图使用的零件库应当使用集成零件库,集成零件库里面的零件包含了电路原理图符号、封装符号、仿真模型、信号完整性模型。如果零件库里的零件不包含完整性模型,就必须登录零件生产商的官网,下载信号完整性模型,或从其他文件找到模型。然后再加载到工程文件里面来。也可以在原理图中调整模型。

- 设定电路原理图中的电源网络电压值(如3.3V5V12V等等)、把电路图中电源的地网络,设定为0V。

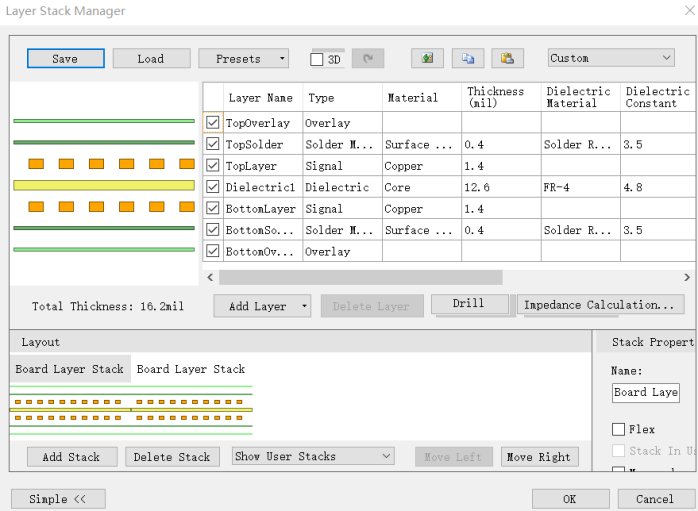

- 设定PCB板的PCB板层堆叠:单击design-------layer stack manager。一般采用系统默认值即可。

通过PCB板的信号完整性分析,可以仿真测量输入信号通过一个网络后,产生的反射畸变和相邻网络之间的信号串扰。

注意:进行信号完整性分析时,被测试的PCB文件,必须在工程中,不能是独立存在的free docment。

信号完整性分析的实例:

1、打开工程文件夹:projedts。这个工程文件夹内包括:电路原理图文件sch PCB板文件pcb。打开PCB板图。见下图。

2、设置PCB板的板层堆叠管理:design------layer stack manager-------弹出下图对话框:

单击上图右边:impedance calculation标签,弹出PCB阻抗计算对话框,见下图:

上图,采用默认值即可。

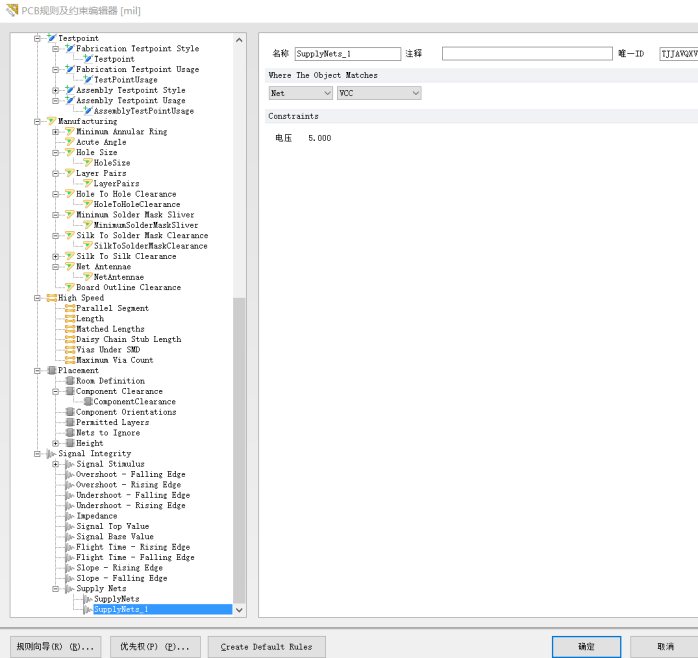

3、单击:design-----rules------弹出规则对话框,见下图:

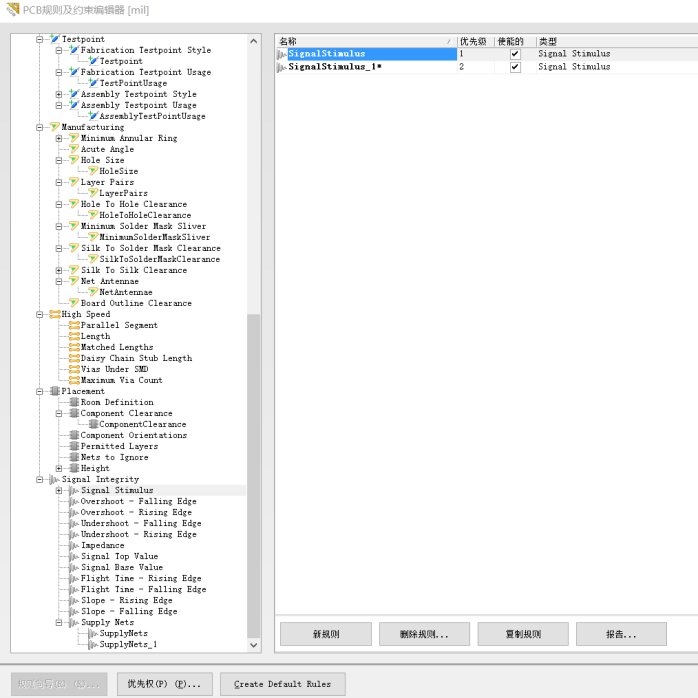

在上图中左下部位找到信号激励:signal stimulus,在signal stimulus上面右键单击,选择new rule,见下图:

在上图的右侧栏,设置激励信号的参数,采用系统默认值即可。

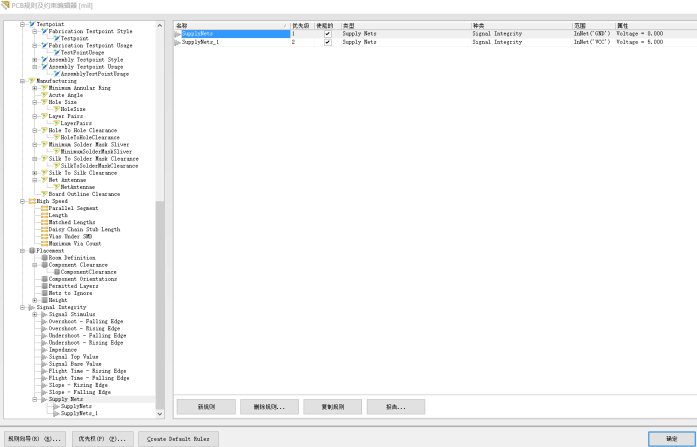

- 设置电压和地网络:在下图的左下角,单击:supply net,选择new rule.

在下图中,右上策新出现的电源网络,把GND网络电压设置为0V,将VCC电压设置为5V。然后单击OK。

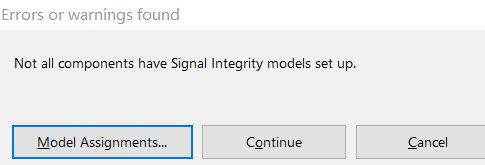

- 选择tools-----signal integrity------弹出一下对话框:

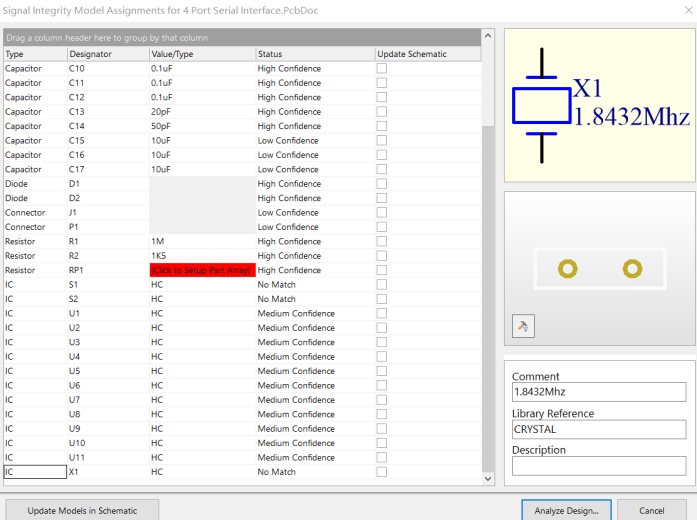

单击上图model assignnent配置完整性分析模型,就会弹出下面的对话框:

上表中的名称解释:

Not match: 表示AD16程序没有找到该器件的完整性分析模型。需要人为指定。

Low confidence:程序自动为该器件指定了一个模型,但置信度很低。

Medium confidence:中级置信度。

High confidence:置信度很高。

Model found:该器件的模型已经找到。

User modifined: 用户修改了模型。

Model added:用户创建了模型。

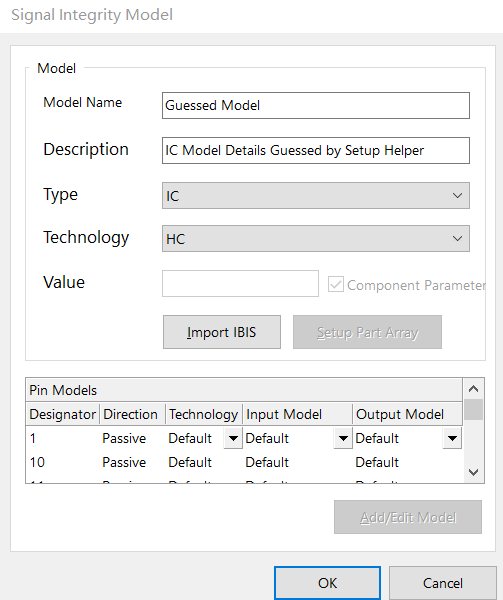

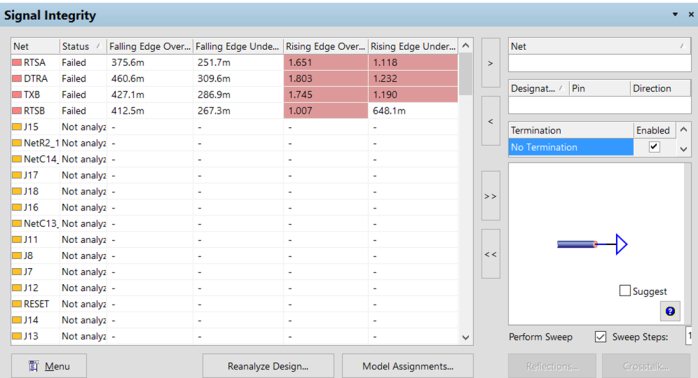

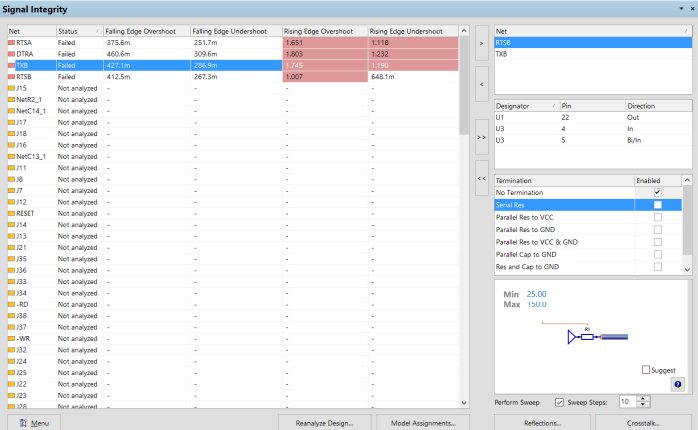

修改期间完整性分析模型的步骤:双击上图中要修改模型器件的status部分-------弹出下图:完整性分析模型修改对话框------在TAPE选项中选择器件的类型-------在technology选项中选择驱动类型-------也可以从外部文件导入与该器件相关联的IBIS模型-------大家IMPORT IBIS-------选择从器件厂商哪里得到的IBIS模型即可-----单击OK。单击上图左下角:update model schematic,将修改后的模型更新到原理图中。单击上图中右下角的analyze design标签------程序进入信号完整性分析------弹出:signal integrity分析网络状态表格:见下面第二图:

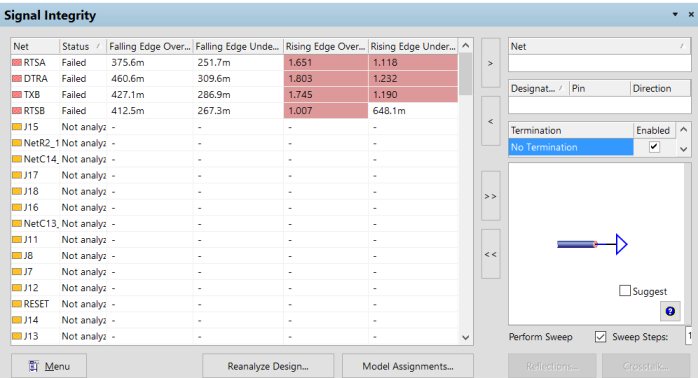

上面的网络完整性分析表格:status,最左的net:代表网络名称,作数第二:status,标明这个网络是否通过了完整性分析(failed:没有通过)、没有分析(not analyze)、分析通过(passed)。上表中的falling edge overshoot:代表脉冲下降沿过冲,falling edge undershoot:代表脉冲下降沿衰减。Rising edge overshoot:代表上升沿过冲。Rising edge undershoot:代表上升沿衰减。

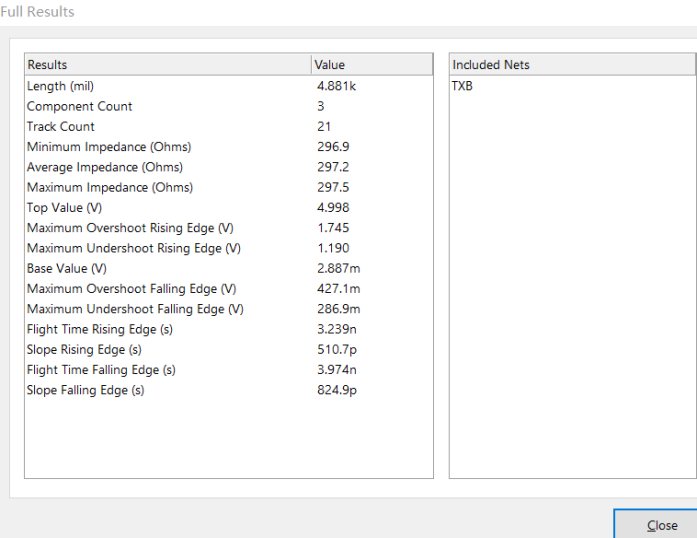

- 怎样查看上面网络表中某一个网络的完整性分析结果:右键单击上表中第三个网络:TXB-------在下拉菜单中选择details细节--------弹出下图:full result(该网络分析的详细结果)。

- 查看网络输出端的反射波形:

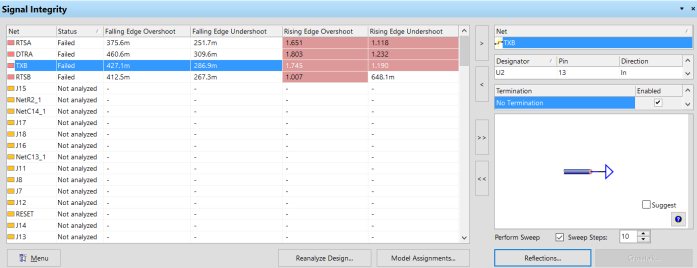

双击上图中网络名称:TXB-------就可把网络TXB运动到上图中的右侧:net(网络框中)-----此时上图右下角灰色(无效)的reflections变成黑色(有效)-------见下图:

单击上图右下角的reflections-------显示输入波形和输出带有反射的波形:见下图。

右键单击上图中右上角红色的TXB-U2 13-NOterm-------在弹出的下拉菜单中选择光标A和光标B,见下图:

利用上图中的光标A和光标B,精确测量,测量结果显示在sin data(在显示信号完整性分析的AD16窗口前提下,AD16屏幕的右下角,显示有:sin data标签)中。

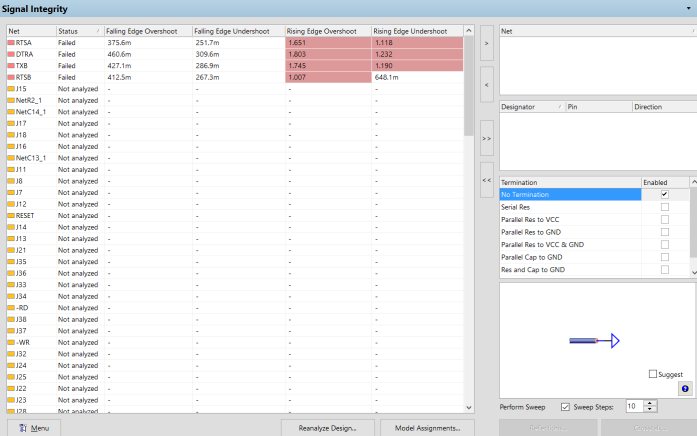

9:网络输出端式接不同的匹配电阻,以消除输出端的反射波形。见下图的右下角:给出了网络输出端试结串联电阻、并联电阻、串联电容、并联电容、并联D时的不同情况下,分别查看哪种情况下网络输出端的反射波形最小。试现在在网络输出端串联电阻的方法:serial res。如下面的第二图所示:

(上图右下角no termination:表示输出端没有接任何匹配电阻)

上图serial res:表示网络输出端串联了匹配电阻。上图中:min:代表匹配电阻取值的最小值:25欧,max:代表匹配电阻取值的最大值是150欧,这两个数值可以有用户任意修改。设定完最大值和最小值后,选中进行扫描:perform sweep,单击上图右下角的reflection------匹配电阻取值在25欧--------150欧之间联系均匀改变时,网络输出端反射波形,在哪个欧姆时最小。以此找到匹配电阻的最佳电阻值。

10、PCB板相邻网络的串扰分析:双击上图中左上角的TXB,使之选中进入上图右上角的NET内,再双击相邻的网络RTSB,也选中到右上角的NET内,右键单击右上角NET内的TXB,在下拉菜单中选择:set aggressor,把TXB设定为入侵者(干扰源),RTSB网络就是受干扰网络了。单击上图右下角的cross talk标签,分析串扰,过一会就显示串扰的波形。