配套FPGA开发板(含该设计的工程代码):https://item.taobao.com/item.htm?spm=a1z10.1-c.w4004-4676525296.4.6e8950ed57YPhv&id=17848039135

-

设计要求

利用FPGA设计一个信号测频器,要求:

(1)测量脉冲信号;

(2)频率测量1-10MHz以及占空比10%-99% 精确到1%;

(3)将测出频率和占空比显示在LCD1602上;

-

设计方案

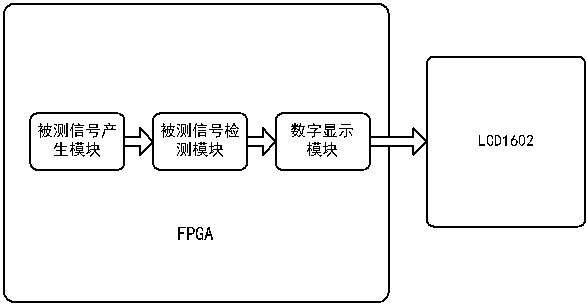

FPGA设计主要分为三个大模块来设计:1.被测信号产生模块;2.被测信号检测模块;3.数字显示模块。设计框图如图 1所示。

-

被测信号产生模块

该模块主要是用来产生被测信号,可以在模块中设置被测信号的频率和占空比。采用的方法是对系统时钟进行计数分频产生被测信号。这部分也采用了一个PLL,输出一个100MHz的时钟作为检测模块的采样时钟。该部分涉及的模块:signal_gen模块和PLL模块。

-

被测信号检测模块

该模块对被测信号进行检测的方法是等精度测频法:

(1)被测信号频率检测

检测被测信号的频率,通过在外部使能信号有效时(即一段时间内),计数系统时钟脉冲数Ns与被测信号脉冲数Nd,若系统时钟频率为Fs,被测信号频率为Fd,则有Fs/Ns=Fd/Nd 最后有Fd=(Fs/Ns)·Nd。

(2)被测信号占空比检测:

检测被测信号的占空比,利用系统时钟,在外部使能信号有效时(即一段时间内),计数被测信号的正脉宽数Np和负脉宽数Nn,则占空比ducy=Np/(Np+Nn)*100%。

该部分涉及的模块:signal_detect模块。

-

数字显示模块

该模块主要分为两个部分:一个部分是把检测的频率码转换为十进制BCD码,采用这种方法虽然会提高运算时间,但却可以大大节省FPGA的资源(面积与速度的折衷);另外一个部分是驱动LCD1602进行显示。这里给出二进制码转换为十进制BCD码的几个步骤(以8bit二进制码为例): 1.将二进制码左移一位(或者乘2);2.找到左移后的码所对应的个,十,百位;3.判断在个位,十位和百位的码是否大于等于5;4.继续重复以上三步直到移位8次后停止;5.如果是则该段码加3。该部分涉及的模块:BCD2to10模块和lcd1602模块。

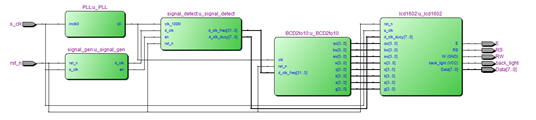

最终在FPGA的RTL视图如图 2所示:

图 2 基于FPGA的信号测频器的RTL视图

-

仿真测试

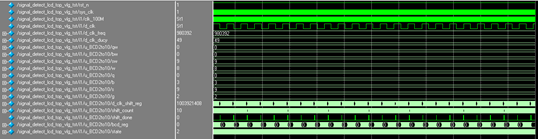

对设计进行Modelsim仿真测试,仿真采用一个近似于1MHz、占空比近似于50%的信号进行测试。在仿真中,我们可以发现经过检测之后的频率为980392Hz,占空比为49%。BCD转换模块分别每一位提取了出来,供LCD1602显示。如图 3所示。

图 3 Modelsim仿真测试

-

板级实验

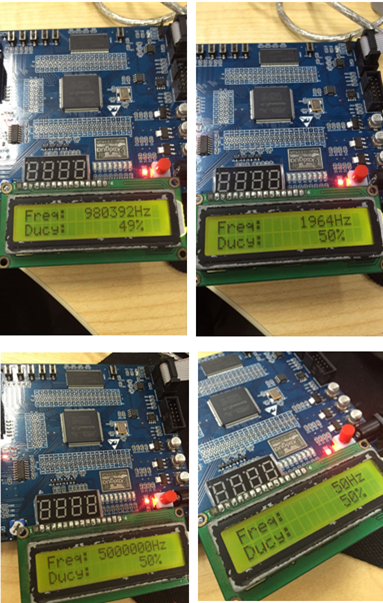

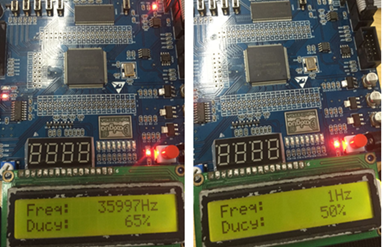

对设计进行板级实验,采用的FPGA是大西瓜的Logic3 FPGA开发套件。实验结果如图 4所示。在误差允许范围内,LCD1602可以准确把被测信号的频率及占空比显示出来。这里注意的是,由于为了检测到1Hz的信号,故设计中延长了LCD显示的刷新周期,所以在一开始LCD显示屏会有一个短时间的闪屏,最后才会稳定下来。

图 4 板级实验结果