数字IC笔试 -- 汇顶设计验证2018

补充知识:

线性反馈移位寄存器(LFSR)

卡诺图化简

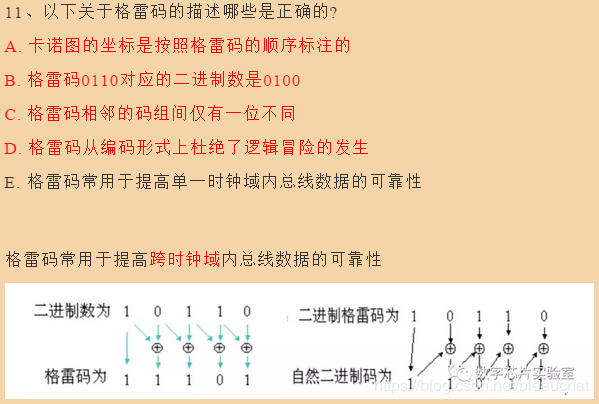

格雷码和二进制码互相转换

代码:

- 二进制数转格雷码

(假设以二进制为0的值做为格雷码的0)

格雷码第n位 = 二进制码第(n+1)位+二进制码第n位。不必理会进制。

Verilog 代码:

gray=(binary>>1)^binary;

- 格雷码转二进制数

二进制码第n位 = 二进制码第(n+1)位+格雷码第n位。因为二进制码和格雷码皆有相同位数,所以二进制码可从最高位的左边位元取0,以进行计算。

verilog 代码: ------假设 reg [n-1] gray,binary;

integer i;

for(i=0;i<=n-1;i=i+1)

binary[i]= ^(gray>>i) //gray移位后,自身按位异或

verilog运算优先级

verilog组合逻辑产生锁存器

https://blog.csdn.net/bleauchat/article/details/100068920

https://blog.csdn.net/qq_36126787/article/details/62054204?depth_1-utm_source=distribute.pc_relevant.none-task&utm_source=distribute.pc_relevant.none-task

最后,锁存器只存在于组合电路中,在时序电路上是不存在的。

待补充

中断:

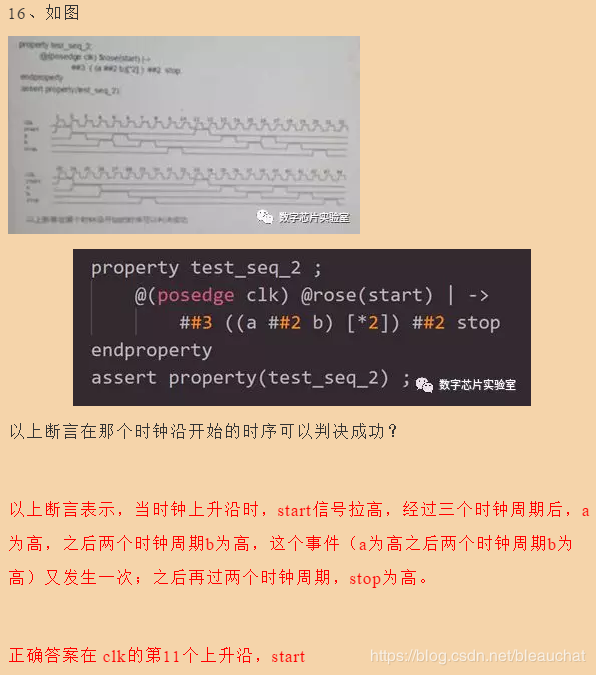

SV断言: