转自:https://zhuanlan.zhihu.com/p/271676045?utm_source=wechat_session&utm_medium=social&utm_oi=627130166644707328&utm_campaign=shareopn

1 Introduction

ADC:量化提高1bit,精度提高6db

信源:编解码,压缩

信道:调制解调,信道编码,提高传输速率与可靠性

发射天线的长度是波长的1/2或1/4,所以调制到高频可以减少天线长度;所以接收端要解调,调制到基带——频率低的部分

通讯系统的标准都是针对发送端,

为什么高铁上信号差:多普勒频移

4G: LTE关键技术

OFDM:正交频分复用,提高频带利用率

MIMO:多天线技术

2 迭代边界

寄存器:建立时间Tsu、保持时间Tn、Tco是从输入到输出的时间

组合逻辑:Td为组合逻辑的延时,理论上还要包括线延迟

这决定了时钟周期的

launch edge与latch edge之间有一个时钟周期

T c o + T d + T s u ≤ T

T n ≤ T c o + T d

时钟周期低的原因:逻辑延时长:关键路径长;线延时长:扇出太大,布局布线做的不好

作业要求:面积最小、时钟频率快吞吐率高

加法树表示滤波器

转置:输入输出交换,箭头方向变

优点:关键路径可以缩短

缺点:数据位宽更大,占更多的资源

两个10bit有符号数相乘,只要19bit存储结果即可

上图表示一输入三输出

=>表示一个延时,一个寄存器

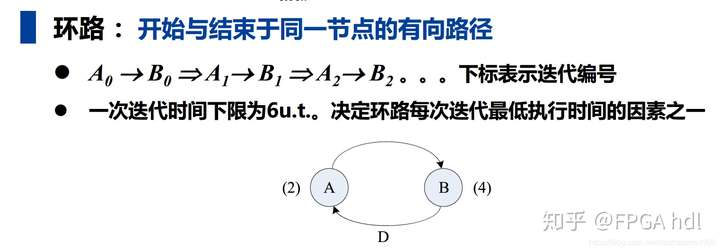

环路边界为什么要除以延迟数:表示电路优化极限

**迭代边界:**关键环路的环路边界,给出了所有环路迭代周期的下限

最长路径矩阵:L ( m ) L^{(m)}L(m)表示环路经过了m个延时,有多少个寄存器,最多有可能有多少个延时

矩阵为什么要看对角线?因为是环路

3 流水线与并行处理

并行处理要注意:当前时刻的输出,只与当前时刻的输入有关,还是还与之前的输入相关

并行系统中,时钟频率低于采样频率,且关键路径基本保持不变

流水线插入FF:时钟频率增大,吞吐率增加;latency增加,面积增加,

- 流水线:交替式并发,有数据依赖

- 并行处理:同时并发,无数据依赖

3.1 低功耗设计

- 静态功耗:漏电流,工艺提高能减少静态功耗

- 动态功耗:取决于电容的充放电,电容、电压、开关频率

电源电压减小->传播延时增大

为什么流水线能降低功耗? 流水线切组合逻辑,则电路电容减少,这时候如果减小电源电压,那么传播延时不变,时钟频率不变而功率降低。

并行处理如何降低功耗? 硬件资源加倍,总负载电容增加,时钟频率降低->传播延时可以增加,电源电压有降低->功耗降低

4 重定时技术

时钟频率差一点会有什么现象:图像会有拖尾,没处理完

重定时技术:可以减少关键路径,改变寄存器数量,但不改变系统功能和迭代边界

重定时方式:在割集一个方向的边增加延时,另一个方向减少延时,可以将流水线视为重定时的一种特例

环路加不了流水线,因为没有前馈割集;迭代边界是针对环路,不是环路的可以无限加流水。

vivado有retiming的选项,可以自动布局布线的时候优化

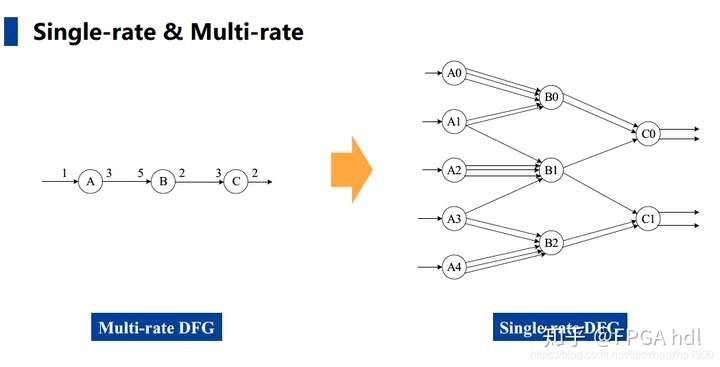

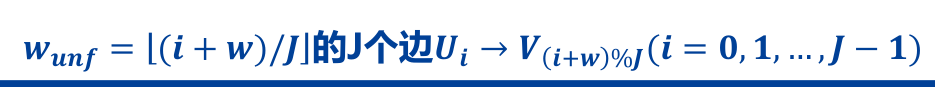

5 展开

w为延时,i为计数下标,J为J倍展开

课后思考,看书

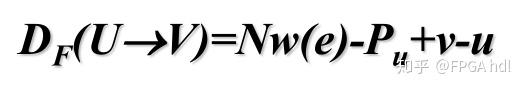

6 折叠

折叠方程:

7 定点量化

为什么用定点化表示:

- ADC输入本来就是有限字长

- 节省存储空间和计算资源,不需要浮点运算单元

8 testbench方法

- 自己给激励

initial begin end或者fork join - 读文件写文件

$readmemh

beyond compare

$fwrite(data,"%h ",xxxx.yyy) - 自动化对比

9 基带信号的调制与解调

手机通信系统:蜂窝通信系统,因为基站是呈蜂窝状分布

数字通信的两个指标:

有效性:传递速率,信源编码就是为了压缩,提高传递速率

可靠性:误码率,信道编码就是为了提高可靠性

天线长度是1/2波长到1/4波长

接受滤波器:

- 最小化误码率:

最大似然 - 最大化信噪比:

利用柯西施瓦兹不等式,得到匹配滤波器公式,也是相关滤波器