将FPGA代码和实际的数字电路对应起来。

always @ (negedge clk_ref_200)

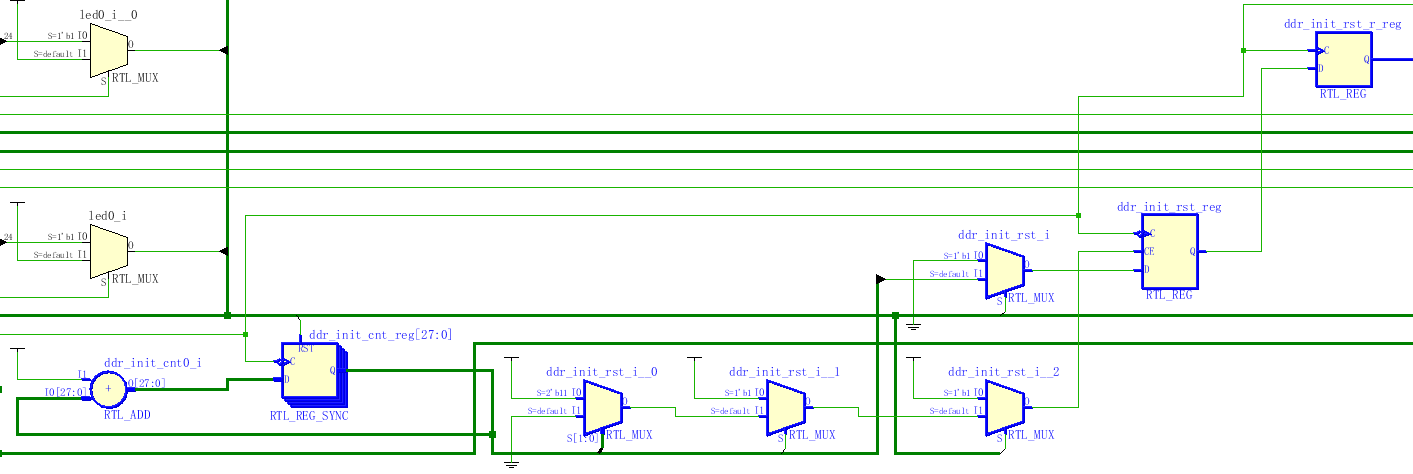

RTL图可以看到,ddr_init_cnt[27:26]==2'b11时,ddr_init_rst_i__0输出1,并且连接到ddr_init_rst_reg的set引脚上,产生DDR3 复位信号。

ddr_init_rst_i的S引脚上连接的是ddr3_init_done信号,当ddr3_init_done为1时,ddr_init_rst_i输出1,连接到ddr_init_rst_reg的rst引脚上。

修改代码后,

always @ (negedge clk_ref_200)

begin

if(ddr3_init_done)

begin

ddr_init_cnt<=28'b0;

end

else

begin

ddr_init_cnt<=ddr_init_cnt+1;

end

end

always @ (negedge clk_ref_200)

begin

if(ddr3_init_done)

begin

ddr_init_rst<=1'b0;

end

else

begin

if(ddr_init_cnt[27]==1'b1)

ddr_init_rst<=1'b1;

else if(ddr_init_cnt[27:26]==2'b11)

ddr_init_rst<=1'b0;

end

end

always @(posedge clk_ref_200) begin ddr_init_rst_r <= ddr_init_rst ; end

下图中可以看到,ddr_init_rst_i__0的S引脚上为2B'11时输出1,然后ddr_init_rst_i__1的S引脚上为1'b1时,输出1。因此

always @ (negedge clk_ref_200)

begin

if(ddr3_init_done)

begin

ddr_init_cnt<=28'b0;

end

else

begin

ddr_init_cnt<=ddr_init_cnt+1;

end

end

always @ (negedge clk_ref_200)

begin

if(ddr3_init_done) //实际上,ddr_init_rst复位是没有什么必要的。

begin

ddr_init_rst<=1'b0;

end

else

begin

if(ddr_init_cnt[27:26]==1'b10) //应该是2'b

ddr_init_rst<=1'b1;

else if(ddr_init_cnt[27:26]==2'b11 || ddr_init_cnt[27:26]==2'b00 || ddr_init_cnt[27:26]==2'b01)

ddr_init_rst<=1'b0;

end

end

always @(posedge clk_ref_200) begin ddr_init_rst_r <= ddr_init_rst ; end

因为 if(ddr_init_cnt[27:26]==1'b10) //应该是2'b 写错,导致下面ddr_init_rst_i和ddr_init_rst_i的S引脚上为“00”时输出为1。应该ddr_init_rst_i和ddr_init_rst_i的S引脚上为“10”时输出为1。