参考:

http://blog.chinaunix.net/uid-20321537-id-3519059.html

http://blog.csdn.net/greston/article/details/8076584

I2S仅仅是PCM的一个分支,接口定义都是一样的, I2S的采样频率一般为44.1KHZ和48KHZ做,PCM采样频率一般为8K,16K。有四组信号: 位时钟信号,同步信号,数据输入,数据输出.

I2S总线标准

I2S(Inter-IC Sound Bus)是飞利浦公司为数字音频设备之间的音频数据传输而制定的一种总线标准。在飞利浦公司的I2S标准中,既规定了硬件接口规范,也规定了数字音频数据的格式。I2S有3个主要信号:

- 串行时钟 SCLK,也叫做位时钟BCLK,即对应数字音频的每一位数据,SCLK的频率=2×采样频率×采样位数 ,呵呵,现在问题来了,有人会问这些东西到底是什么意思呢?其实,I2S一般是传输立体声,有两个声道channel,采样频率指得是采样数率,多久去采集一个点,每个点是几个bit组成。

- 帧时钟LRCK,用于切换左右声道的数据,LRCK为“0”表示正在传输的是左声道的数据,为“1”表示正在传输的是右声道的数据。LRCLK == FS,就是采样频率

- 串行数据SDATA,就是用二进制补码表示的音频数据,有时为了使系统间能够更好的同步,还需要另外传输一个信号MCLK,称为主时钟,也叫系统时钟(System Clock),是采样频率的256或384倍

I2S协议时序

I2S格式的信号无论有多少位数据,,数据的最高位总是出现在LRCK变化(也就是一帧开始)后的第2个BCLK脉冲处。这就使得接收端与发送端的有效位数可以不同。如果接收端能处理的有效位数少于发送端,可以放弃数据帧中多余的低位数据;如果接收端能处理的有效位数多于发送端,可以自行补足剩余的位。这种同步机制使得数字音频设备的互连更加方便,而且不会造成数据错。

从时序图可以看出,I2S左右声道分别为高低电平,PCM只有一个起始信号,左声道数据紧跟右声道.

PCM协议

PCM(PCM-clock、PCM-sync、PCM-in、PCM-out)脉冲编码调制,模拟语音信号经过采样量化以及一定数据排列就是PCM了。理论上可以传输单声道,双声道立体声和多声道。是数字音频的raw data.

从时序图可以看出,I2S左右声道分别为高低电平,PCM只有一个起始信号,左声道数据紧跟右声道.

==============================================================================

引言

I2S(InterIC Sound Bus)是飞利浦公司针对数字音频设备之间的音频数据传输而制定的一种总线标准,采用沿独立的导线传输时钟与数据信号的设计,通过分离数据和时钟信号,避免了时差诱发的失真。I2S总线简单有效,可以有效提升输出数据的质量,在各种嵌入式音频系统中有广泛应用。但是在嵌入式音频系统设计中,并不是所有的MCU都支持I2S总线格式,再加上I2S还没有统一的接口标准,不同的厂家生产的设备接口也是五花八门,采用软件模拟实现I2S总线可有效解决在不支持其的MCU和设备之间通过I2S总线实现数据传输时出现的问题。

本文通过在以太网数字语音广播系统中软件模拟I2S总线实现语音数据传输,给出了软件模拟实现I2S总线的方法。

1 I2S总线规范

I2S为三线总线,3个信号分别为:

① 串行时钟SCK,也叫位时钟(BCK)。即每发送1位数字音频数据,SCK上都有1个脉冲。SCK的频率=2×采样频率×采样位数。在数据传输过程中,I2S总线的发送器和接收器都可以作为系统的主机来提供系统的时钟频率。

② 帧时钟WS,即命令(声道)选择,用于切换左右声道的数据。WS的频率等于采样频率,由系统主机提供。WS为“1”表示传输的是左声道的数据,WS为“0”表示传输的是右声道的数据。

③ 串行数据信号SD,用于传输二进制补码表示的音频数据。

I2S格式的信号无论有多少位有效数据,数据位的最高位(MSB)总是被最先传输,1次能够发送的数据决定于I2S格式的有效位数。

1个典型的I2S信号时序如图1所示

图1 I2S总线典型时序图

随着技术的发展,在统一的I2S接口下出现了多种不同的数据格式。根据SD信号相对于SCK和WS位置的不同,分为左对齐和右对齐2种格式,如图2和图3所示。

图2 16位有效位数的左对齐格式

图3 16位有效位数的右对齐格式

在上面2种数据传输格式中,当WS为“1”时传输的是左声道的数据,当WS为“0”时传输的是右声道的数据。为了保证数字音频信号的正确传输,发送端和接收端必须采用相同的数据格式。

2 软件模拟I2S

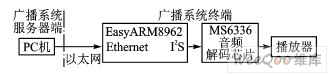

以太网数字语音广播系统主要是指以以太网为传播介质提供音频服务的广播系统,将语音信号以标准IP包的形式在以太网上进行传送,以实现语音广播功能。该系统在PC机端通过麦克风采集语音数据,然后将采集到的语音数据通过以太网发送给嵌入式终端,嵌入式终端将接收到的语音数据进行数/模转换后进行播放。系统实现框图如图4所示[5]。

图4 以太网数字语音广播系统框图

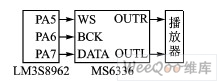

图5 LM3S8962与MS6336的连接图

广播系统终端的MCU LM3S8962将接收到的语音数据通过I2S总线发送给语音解码芯片MS6336进行数/模转换并播放,

LM3S8962和MS6336的连接如图5所示。为了完整还原出语音信号,需要保证软件模拟I2S信号时序严格精确,高低电平的转换采用延时程序实现。MS6336为16位D/A芯片,其I2S时序如图6所示。

图6 MS6336的典型I2S时序图

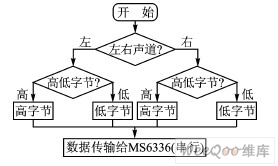

该系统中的语音数据双声道,16位采样,1个采样点的数据为4字节,1个采样点数据通过MCU发送给MS6336,数据发送流程如图7所示。

图7 1个采样点数据发送流程

软件模拟I2S引脚的定义如下:

#define I2S_WS GPIO_PIN_5//模拟I2S声道选择时钟控制位

#define I2S_BCK GPIO_PIN_6//模拟I2S位时钟控制位

#define I2S_DATA GPIO_PIN_7//模拟I2S数据传送位

根据MS6336的I2S总线格式以及数据发送流程,软件模拟I2S总线的步骤如下:

① 根据语音数据采样率及采样位数计算得到SCK的值和WS的值(WS的值等于采样频率)。

系统采样率为44.1 kHz,则SCK=2×44.1 kHz×103×16=1 411 200 Hz,WS=44 100 Hz。1个SCK时钟周期T=1/SCK=0�7 μs。采用延时程序模拟SCK时钟周期需要应用示波器来精确延时时间。本系统中一个SCK周期的延时为delayI2S(2)。

② 将WS、BCK和DATA均置为高电平。

③ 选择左右声道。首先发送左声道数据,将WS置低(若发送右声道数据则将WS置高)。

for(ChannelCnt=0;ChannelCnt<2;ChannelCnt++){//双声道选择播放

if(ChannelCnt==0){//右声道选择信号为高电平

HWREG(GPIO_PORTA_BASE + (GPIO_O_DATA + (I2S_WS << 2))) = ~I2S_WS;

}

else{//左声道选择信号为低电平

HWREG(GPIO_PORTA_BASE + (GPIO_O_DATA + (I2S_WS << 2))) = I2S_WS;

}

……

}

④ 选择高低字节。将左声道数据以高低字节的顺序发送,在发送高字节第1位数据之前先发送1个周期的串行时钟。

for(HorLCnt=0;HorLCnt<2;HorLCnt++){//声道数据高低字节选择

if(ChannelCnt==1){//左声道

if(HorLCnt==0){//低字节

c=*(SampleData+1);//SampleData指向音频数据缓冲区首地址,即左声道低字节

delayI2S(2);//发送第一个数据位之前需要延迟一个位时钟周期

}

else{//低字节

c=*SampleData;

}

}

……

}

⑤ 开始传输音频数据(音频数据的传输在SCK下降沿准备数据,在SCK的上升沿发

送给数据接收端)。将采样点左声道数据的高字节最高位送给SD,设置SCK为低电平,此时为SCK的下降沿,数据准备好。延时半个SCK周期以后将SCK置为高电平,此时SD线上的数据发送给数据接收端,延时半个SCK周期。依次将左声道剩余位数据按照最高位的方式发送出去。

for(BitCnt=0;BitCnt<8;BitCnt++){//1次传送的数据长度为8位,先传送高字节再传送低字节置时钟线SCK为低,开始准备数据位

HWREG(GPIO_PORTA_BASE + (GPIO_O_DATA + (I2S_BCK << 2))) = ~I2S_BCK;

if((c<<BitCnt)&0x80) {

HWREG(GPIO_PORTA_BASE + (GPIO_O_DATA + (I2S_DATA << 2))) = I2S_DATA;

}

else{

HWREG(GPIO_PORTA_BASE + (GPIO_O_DATA + (I2S_DATA << 2))) = ~I2S_DATA;

}

delayI2S(1); //延时半个SCK时钟周期置时钟线为高,开始传输数据位

HWREG(GPIO_PORTA_BASE + (GPIO_O_DATA + (I2S_BCK << 2))) = I2S_BCK;

delayI2S(1);//延时半个时钟周期

}

⑥ 当将1个采样点的左声道的数据发送完以后,延时2个SCK周期,然后发送右声道的数据(同左声道数据的发送过程)。

根据以上的过程对每个采样点的数据进行处理,就可以实现通过软件模拟I2S总线传输音频数据了。以上实现的是典型I2S时序模拟,而左对齐和右对齐2种格式只是时序稍有差异,模拟实现过程同典型I2S总线模拟实现过程基本相同。

结语

在以太网数字语音广播系统中应用软件模拟实现I2S总线时序,能够成功地实现语音信号的数据传输,实现语音信号的实时广播,表明了软件模拟实现I2S总线的可行性,为解决不支持I2S总线的MCU和各种I2S总线设备间的通信提供了一种可行的方法。但是,在应用软件模拟实现I2S的以太网数字语音广播系统实时播放语音信号时,存在一些噪声,表明在采用软件模拟实现I2S的时序精确性上存在一些欠缺。