课堂测试(ch06)

-

1.下面代码中,对数组x填充后,采用直接映射高速缓存,所有对x和y引用的命中率为(D)

A .1

B .1/4

C .1/2

D .3/4

解析:缓存命中:当程序需要第(k+1)层的数据对象d的时候,首先会在第k层找d;如果d刚好缓存在第k层,那么就叫做缓存命中;反之,不命中,在填充了之后,对于x和y数组,只有在引用第0个和第4个元素的时候发生不命中。因而命中率为75%(即(8-2)/8)。

- 有关高速缓存的说法正确的是(A C D )

A .高速缓存的容量可以用C=S* E * B来计算。

B.高速缓存容量为2048,高速缓存结构为(32 ,8,8,32)

C.直接映射高速缓存要:组选择、行匹配、字抽取

D.当程序访问大小为2的幂的数组时,直接映射高带缓存中常发生冲突不命中

解析:选项B:高速缓存容量为2048,高速缓存结构为((32),8,8,32)

-

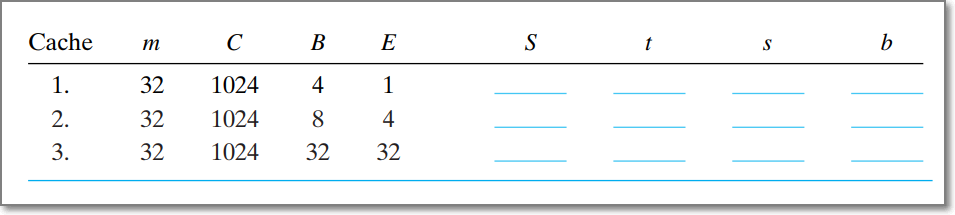

The following table gives the parameters for a number of different caches. For

each cache, determine the number of cache sets (S), tag bits (t), set index bits (s),

and block offset bits (b) ( A C D )

A .第三行S为1

B .第一行t为24

C .第二行b为5

D .第三行s的值为0

解析:

-

有关缓存的说法,正确的是(A C)

A .LRU策略指的是替换策略的缓存会选择最后被访问时间距现在最远的块

B .不同层之间以字节为传送单元来回复制

C .缓存不命时,决定哪个块是牺牲块由替换策略来控制

D .空缓存的不命中叫冲突不命中

解析:B:第k层和第k+1层之间以块大小为传送单元来回拷贝

D:取数据时也分缓存命中和缓存不命中。缓存不命中也分为几大类

1)强制不命中:即如果第k层的缓存是空的,那么一定就会不命中了。2)冲突不命中:假如发生了不命中之后,数据是会被缓存在第k层的,硬件通常将第k+1层中某个块限制在第k层中的某个子集中(采用映射)。

3)容量不命中:当第k层的容量不足以缓存下需要缓存的数据时,就称为容量不命中。因此,空缓存的不命中属于强制不命中

-

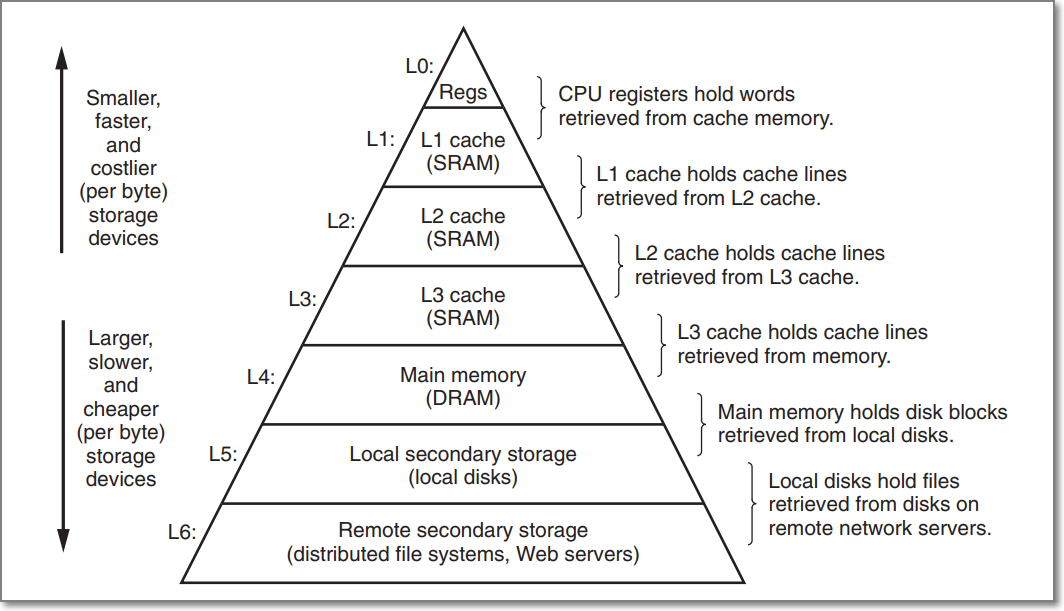

下面说法正确的是(ABC)

A. 存储层次结构中最小的缓存是寄存器

B. 存储层次结构的中心思想是每一层都缓存来自较低一层的数据对象

C. L4主存可以看作是L5:本地磁盘的缓存

D. L4主存可以看作是L6的缓存

解析:在寄存器和内存、内存和磁盘之间读写速度差距很大时,插入一个高速缓存存储器,这样的思想形成了存储器层次结构。图中每一层都是下一层的缓存,也就是说,层次结构的每一层都缓存来自较低一层的数据。缓存存储器是分块的,数据总是以块为基本单位在每一层之间传递,块的大小只在相互传递的两层之间是相同的,并且一般是越位与底层的块大小越大,这样就弥补了底层存储器每次访问的所花销的大量的时间。另外,数据是缓存好了,但是不一定缓存的数据就是需要的数据。

-

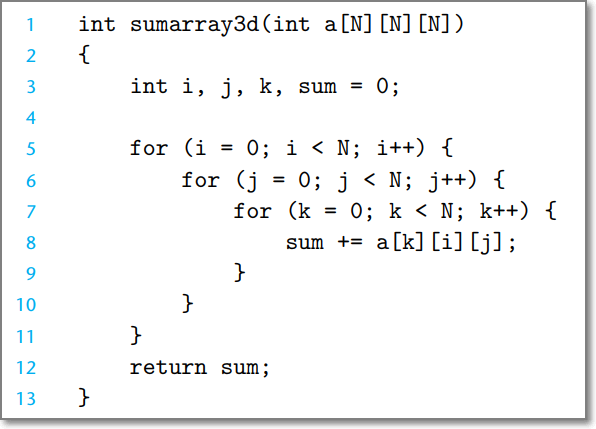

下面代码的步长是(C)

A. 1

B. N

C. N*N

D. N * N * N

解析:步长值就是循环体中计数器每次的增量值啊,当然,增量也可以是负数的。 For...Next循环的步长step应依据你作该循环的需求确定,以下提供MSDN的说明: For...Next 语句

以指定次数来重复执行一组语句。本题该循环体中计数器每次的增量为N*N。

-

下面代码中(C)局部性最差

A.

1 #define N 1000

2

3 typedef struct {

4 int vel[3];

5 int acc[3];

6 } point;

7

8 point p[N];

B.

1 void clear1(point *p, int n)

2 {

3 int i, j;

4

5 for (i = 0; i < n; i++) {

6 for (j = 0; j < 3; j++)

7 p[i].vel[j] = 0;

8 for (j = 0; j < 3; j++)

9 p[i].acc[j] = 0;

10 }

11 }

C.

1 void clear2(point *p, int n)

2 {

3 int i, j;

4

5 for (i = 0; i < n; i++) {

6 for (j = 0; j < 3; j++) {

7 p[i].vel[j] = 0;

8 p[i].acc[j] = 0;

9 }

10 }

11 }

D.

1 void clear3(point *p, int n)

2 {

3 int i, j;

4

5 for (j = 0; j < 3; j++) {

6 for (i = 0; i < n; i++)

7 p[i].vel[j] = 0;

8 for (i = 0; i < n; i++)

9 p[i].acc[j] = 0;

10 }

11 }

D .不确定

解析:C只具有时间局部性,而AB具有时间和空间局部性

-

程序中(C)语句具有良好的局部性

A .顺序

B .分支

C .循环

D .以上都是

解析:程序的局部性原理是指程序在执行时呈现出局部性规律,即在一段时间内,整个程序的执行仅限于程序中的某一部分。相应地,执行所访问的存储空间也局限于某个内存区域。也就是说,程序倾向于引用邻近于其他最近引用过得数据项,或者最近引用过的数据项本身。我的理解就是:通过利用“缓存”来提高程序运行效率,所以循环语句具有良好的局部性

-

下面代码,(C)具有差的空间局部性。

A .1 int sumvec(int v[N])

2 {

3 int i, sum = 0;

4

5 for (i = 0; i < N; i++)

6 sum += v[i];

7 return sum;

8 }

B .1 int sumarrayrows(int a[M][N])

2 {

3 int i, j, sum = 0;

4 5

for (i = 0; i < M; i++)

6 for (j = 0; j < N; j++)

7 sum += a[i][j];

8 return sum;

9 }

C .1 int sumarraycols(int a[M][N])

2 {

3 int i, j, sum = 0;

4 5

for (j = 0; j < N; j++)

6 for (i = 0; i < M; i++)

7 sum += a[i][j];

8 return sum;

9 }

D .以上都不对

解析:空间局部性是指一旦程序访问了某个存储单元,则不久之后。其附近的存储单元也将被访问。C的函数的空间局部性很差,这是因为它使用步长为N的引用模式来扫描

-

有关局部性原理,说法正确的是( A B D )

A .CPU通过内存映射I/O向I/O设备发命令

B .DMA传送不需要CPU的干涉

C .SSD是一种基于闪存或Flash的存储技术

D .逻辑磁盘块的逻辑块号可以翻译成一个(盘面,磁道,扇区 )三元组。

解析:控制器上的固件执行一个快速表查找,将一个逻辑块号翻译一个(盘面、磁道、扇区)的三元组,这个三原则唯一地表示了对应的物理扇区。书P411

-

下面(B)是I/O总线

A .USB

B .PCI

C .网卡

D .图形卡

解析:PC机中的总线分为CPU总线和I/O总线,PCI总线属于I/O总线,I/O总线指缆线和连接器系统,用来传输I/O路径技术指定的数据和控制信号,另外还包括一个总线终结电阻或电路,这个终结电阻用来减弱电缆上的信号反射干扰。

-

图中磁盘一个扇区的访问时间约为(A )ms

A .10

B .5

C .6

D .8

E .12

解析:无。

-

有关磁盘操作,说法正确的是(A C)

A .对磁盘扇区的访问时间包括三个部分中,传送时间最小。

B .磁盘以字节为单位读写数据

C .磁盘以扇区为单位读写数据

D .读写头总处于同一柱面

解析:读取数据的时候首先寻找的是数据所在的扇区,而数据是以字节为基本单位记录在各个扇区上,磁盘以扇区大小的块来读写数据。

-

计算下面磁盘的容量(C):4个盘片,100000个柱面,每条磁道400个扇区,每个扇区512个字节

A .81.92GB

B .40.96GB

C .163.84

D .327.68GB

解析:存储容量C=柱面(磁道)数T x 磁盘面(磁头)数H x 扇区数S x 字节数 =4x2x100000x400x512=163.84GB

-

有关磁盘,说法正确的是(AC)

A. 磁盘的读取时间为毫秒级

B. 每张磁盘有一个表面

C. 表面由磁道组成

D. 每个扇区的面积不同,包含的数据位的数量也不一样

解析:磁盘的记录方式有两种:1.旧式——非分区记录方式(不同磁道扇区数相同);2.新式——分区记录方式(不同磁道扇区数不同)。旧式每个磁道所拥有的扇区数量都是一样的,且越往外面,扇区的面积越大,越往外面,转动的速度越快。每个扇区所能容纳的数据量是相同的,都是512字节,数据量需要平均分配在扇区面积的每个角落,所以外面扇区的数据密度低,里面扇区的速度密度高。

-

根据携带信号不同,总线可分为(B D E)

A. 系统总线

B. 数据总线

C. 内存总线

D. 地址总线

E. 控制总线

解析:无

-

关于非易失性存储器,下面说法正确的是(C E)

A. DRAM是非易失性存储器

B. SRAM是非易失性存储器

C. PROM只能编程一次

D. EEPROM可以用紫外线进行擦除

E. 存在ROM中的程序通常被称为固件

解析:非易失存储器中:如果断电,DRAM和SRAM会丢失他们的信息,从这个意义上讲,他们是已丢失的。PROM只能被编程一次,其中的熔丝只能用高电流熔断一次。EEPROM才是非易失性的、随机存取的存储器,DRAM和SRAM不是非易失性的。

-

通过使用两个时钟沿作为控制信号,对DRAM进行增强的是(C)

A. FPM DAM

B. SDRAM

C. DDR SDRAM

D. VRAM

E. EDO DRAM

解析:双倍数据速率同步DRAM(DDR SDRAM):使用两个时钟沿作为控制信号,使DRAM速度翻倍

-

有关RAM的说法,正确的是(A D E G)

A. SRAM和DRAM掉电后均无法保存里面的内容。

B. DRAM将一个bit存在一个双稳态的存储单元中

C. 一般来说,SRAM比DRAM快

D. SRAM常用来作高速缓存

E. DRAM将每一个bit存储为对一个电容充电

F. SRAM需要不断刷新

G.DRAM被组织为二维数组而不是线性数组

解析:SRAM将一个bit存在一个双稳态的存储单元中,而DRAM一般采用电容作为存储单元。DRAM每一个2ms要刷新1次避免数据丢失而SRAM是静态的不需要刷新。SDRAM在1个时钟周期内只传输1次数据,它是在时钟的上升期进行数据传输;而DDR内存则是1个时钟周期内传输两次次数据,它能够在时钟的上升期和降落期各传输1次数据,因此称为双倍速率同步动态随机存储器。

-

有关计算机存储系统,下面说法正确的是(B C D)

A. 程序具有良好的局部性表现在倾向于从存储器层次结构中的较低层次处访问数据,这样节省时间

B. 存储层次涉用不同容量,成本,访问时间的存储设备

C. 存储层次设计基于局部性原理

D. “存储山”是时间局部性和空间局部性的函数

解析:程序具有良好的局部性表现在倾向于从存储器层次结构中的较高层次处访问数据,这样节省时间,层次越低,访问速度越慢。